今日はアルゴリズムの工夫による低消費電力化についてです。

動画処理の世界では、動画をフレームで記録する際に、データ線の遷移確率を減らすデータ表現等が次々に発表されていきました。今日は私が以前映像録画機器で用いた事例として「符号付き絶対値表現」を用いた低消費電力化手法を紹介いたします。

ビデオ信号のフレーム差分データ処理

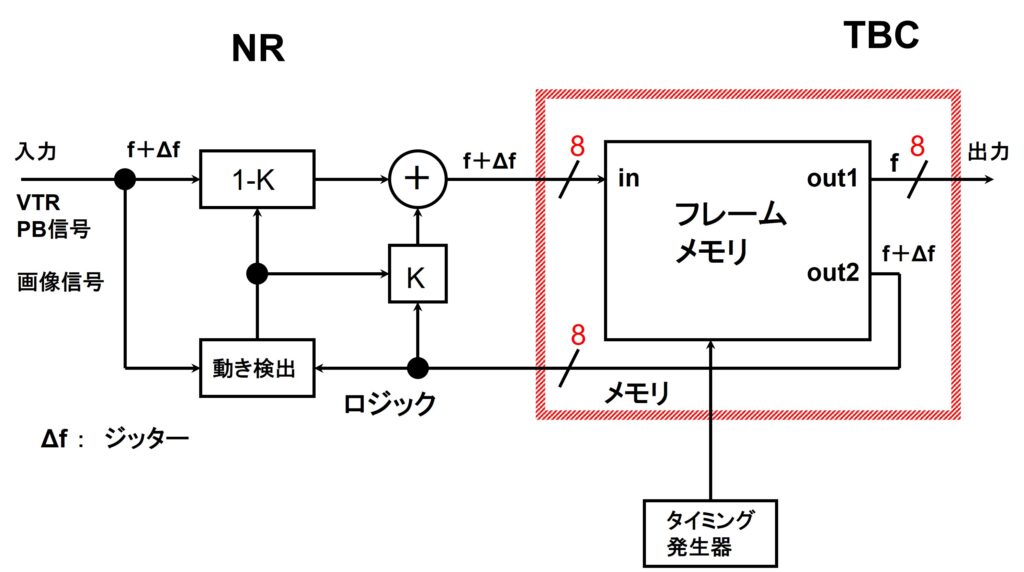

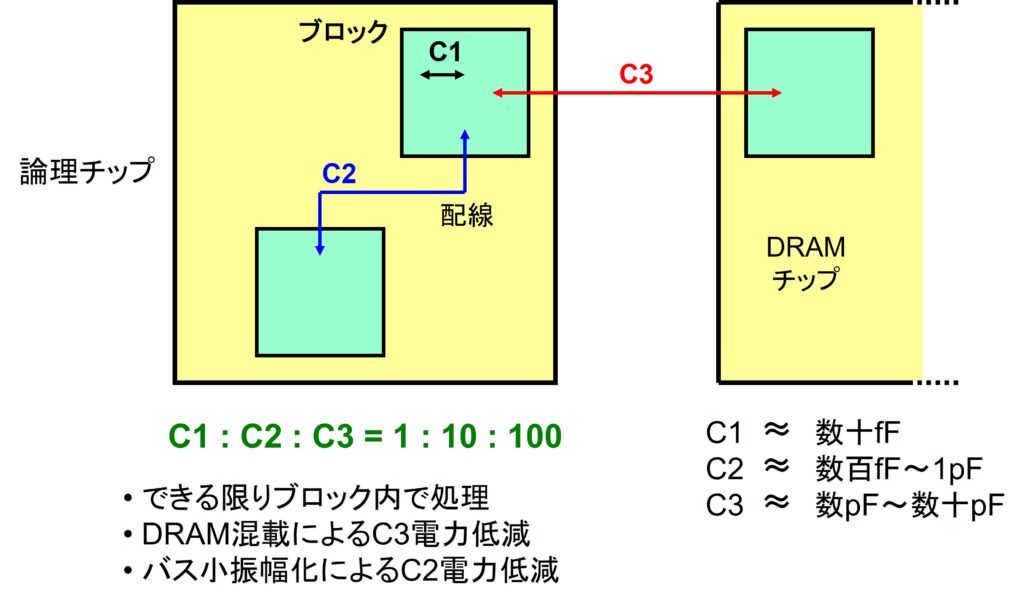

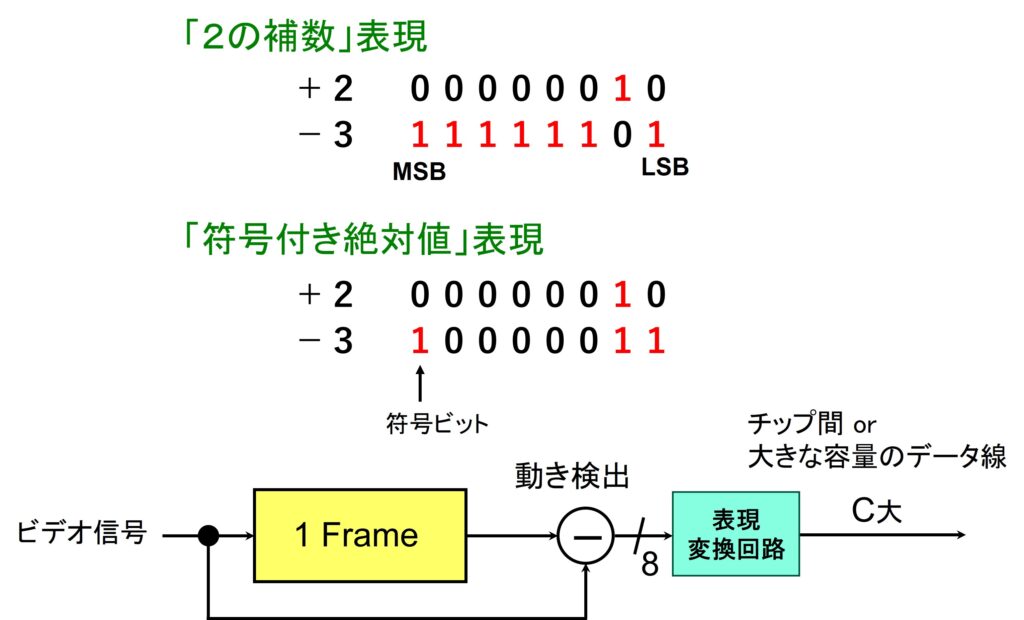

記録中の映像フレームで、絵の一部が動いたか、そうではないか、をLSIで検出処理する場合、現在のフレームと1フレーム前とのビデオ信号の差を判別する処理が必要となります。15図で示した通り、この時必要なフレーム差分データは、一般に大きな容量ノードであるバスラインあるいはチップ外へ出力されることが多いので、消費電力が大きくなりがちです。またビデオ信号はフレーム間の相関が大きく、差分処理の出力が、「少し大きい」あるいは「少し小さい」値となる場合が多いです。

デジタルデータで処理する場合、通常「2の補数」で表現します。図15にも示しましたが、1サンプルごとにMSBからLSBまで表現する場合、ほとんどのビットが赤数字で示したようにデータ遷移してしまいます。このビットのデータ遷移=電力消費の発生ですから、大きな電力消費をしていることになります。

符号付き絶対値表現

これに対し図15の中央のように「符号付き絶対値表現」を用いますと、この仕組みでは専用の符号ビットを持たせていますので、符号ビット自身は頻繁にデータ遷移しますが、一方で絶対値データ値のビット(LSB近傍を除く)はほとんどデータ遷移しません。データ遷移がなければ電力消費しないので、「符号付き絶対値表現」を用いると、データバスやLSIチップ間配線の様な(消費電力が大きくなる)大容量ノードでのデータ遷移の確率を減らすので、十分な低消費電力化が見込めます。

この方法によって、世の中のビデオカメラの画像信号のフレーム間処理や、水平走査線間処理等の相関の大きな信号処理の低消費電力化に成功するなど、家庭録画機器の低消費電力化と性能アップに特に有効な手法となりました。

次はチャージリサイクリングによる低消費電力化について、ご紹介します。