今日は、アーキテクチャの工夫による低消費電力化の方法です。

アーキテクチャの工夫による低消費電力化の方法として、並列処理、パイプライン処理が従来よりある処理技術として有名です。

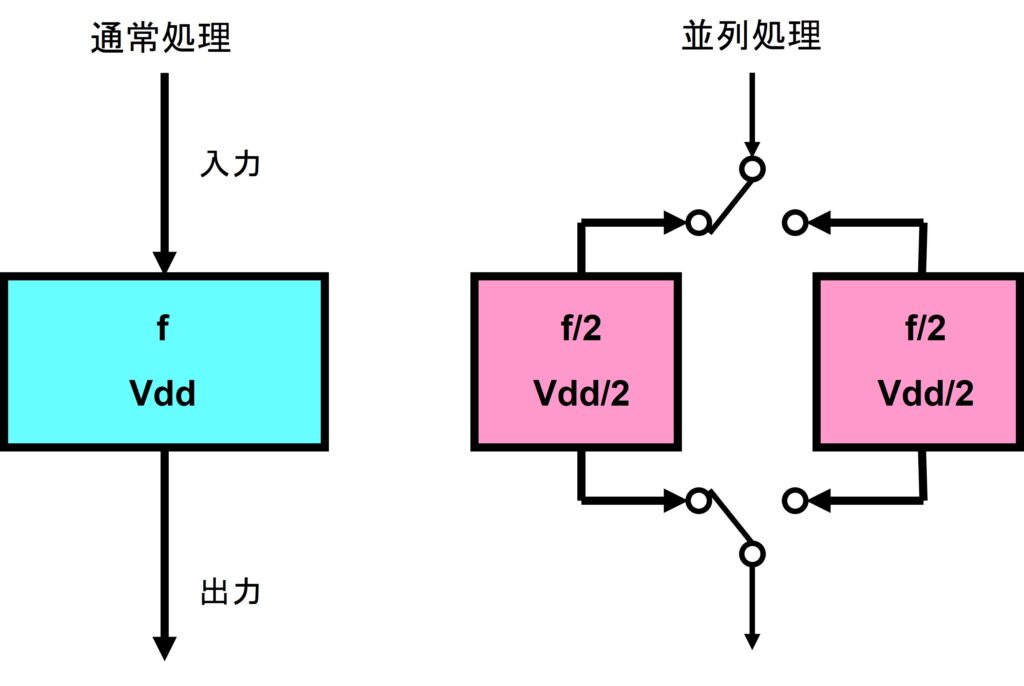

並列処理

そのうちの1つ、並列処理の概略図を(図14)に示します。例えば、ある演算器を2つ並列に配置します。この配置ですと演算機1つの場合と比較して、同一スループットに対して演算サイクルタイムを2倍に広げる事ができます。という事は動作周波数を1/2に下げられるので、電源電圧Veを約1/3にする低消費電力化が図れることになります。

ただしデメリットもあります。並列2系統の回路が必要ですから、当然ながらチップ面積が大きくなりますので、システムLSIのコスト(またはチップサイズ)と消費電力とはトレードオフの関係になりますので、並列処理はとにかく低消費電力を重視する製品向けのLSIに適した方式であると言えます。