今回はPLLの元となる「負帰還」について話してみたいと思います。

負帰還は何かを制御するときの基本中の基本です。これを理解していないと、回路が不安定になり時には発振し、大きな問題を引き起こしたりします。

負帰還とは

負帰還回路の”帰還”とは、信号が戻ってくるから帰還といい、戻ってくる値が入れた信号に対して負(つまり、反対)なので、負帰還といいます。

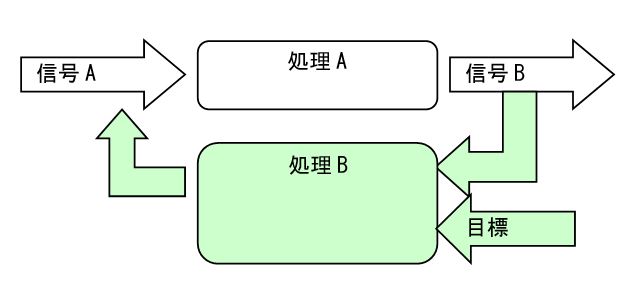

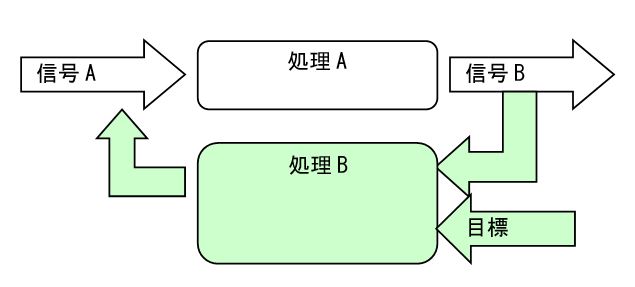

信号Aは処理Aを経由して信号Bに変化するとします。しかし、信号Aを送った人は、本当に信号Bに変化したか分かりません。処理Aがあまり信用出来なかった場合どうするかというと、信用できる処理Bを使って信号Bの様子を聞きだそうとします。もし信号Bが目標とずれていたら、ずれている分だけ信号Aを補正し、信号Bを目標に一致させます。

このような面倒な事をしなくても、処理Aをきちんと設計して、目標通りに動作するようにしたら良いと考える方もいると思います。確かにその通りなのですが、電子回路の中にも得意/不得意があって、オールマイティな回路はなかなか出来ないものです。

DCフィードバック回路で負帰還を説明する

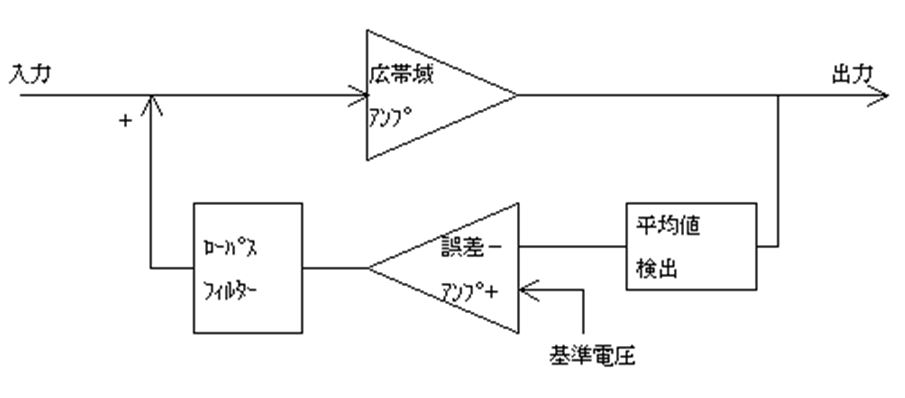

通信系の回路で、DCフィードバックという回路(別の名前で言うかもしれませんが)があります。この回路を例にして、もう少し具体的に説明してみたいと思います。

微小信号を増幅して、デジタル回路でも判別できるように増幅する”広帯域アンプ”は、出来るだけ高速に動作するように寄生容量を少なくする必要があります。そのため、トランジスタのサイズは小さいほうがいい事になるのですが、小さくなると絶対値がバラツクだけではなく、相対精度も悪くなり、適切なバイアス状態に増幅器を保てなくなります。

これを防ぐために出力電圧の平均値(つまりバイアス)を検出して、基準電圧(目標)と誤差アンプで比較し、入力を補正する回路を追加します。平均値を制御するわけですから、誤差アンプは高速動作する必要は無くなりトランジスタサイズを十分大きく出来ます(でも、チップサイズとのトレードオフがありますが)。

このDCフィードバック回路を使うことで、温度や電源が変わっても、製造ロットが変わっても、常に広帯域アンプの出力バイアス電圧は基準電圧と同じなので、この次の段、例えばA/Dコンバータは安心してデジタルに変換できる事になります。

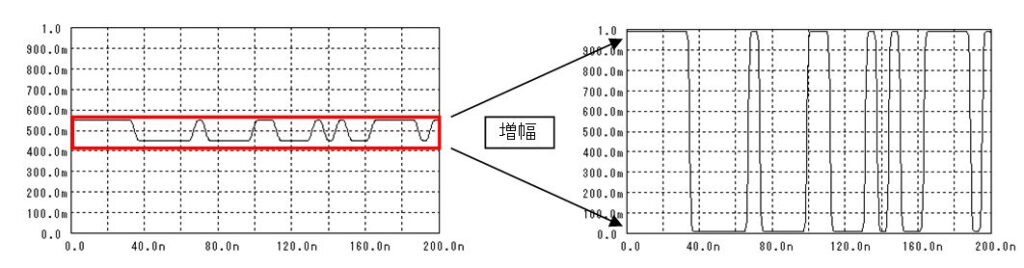

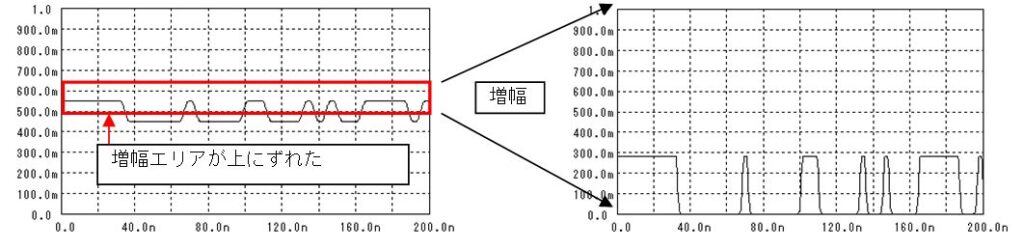

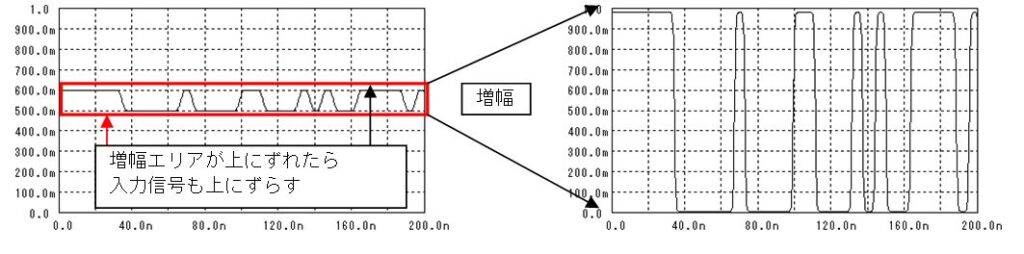

上図のような小さな信号が入力された時、広帯域アンプが0.5V付近を増幅できるようにバイアスされていたら、出力にきちんと増幅した信号が出てくるのですが、

バイアスが上にずれて”0.55V”付近を増幅するようになっていたとしたら、下半分にしか信号が出てこなくなり、デジタル信号変変換が出来なくなります。

DCフィードバックはこの状態にならないように、入力信号のレベルを(または広帯域アンプのバイアスを)調整する役目をしています。

通信系の回路では、主信号通すブロックには低雑音、線形性や高利得、広帯域、高速、高駆動などの厳しい要求が課せられるため、主信号系回路のバイアス制御などは負帰還回路を用いて行う事が一般的です。

オールマイティな回路が作れたら負帰還回路は要らないかもしれませんが、現実はそんなにうまくいきません。

主信号系と制御系(負帰還回路)がお互いに補正しあいながら全体としてうまく動作しているところは、仲の良い夫婦と似ていると思うのは僕だけでしょうか。

次回は、負帰還の安定性に触れたいと思います。(美斉津)