今日はとトランジスタのオフセットが引き起こす問題について紹介したいと思います。

物を作るときには必ず製造上のバラツキが発生します。

(コピーすれば同じものが2つ出来ますが、これはデジタル化しているから同じといえるのであって、この世にまったく同じものはないと思っています)

バラツキは回路の特性を大きく変えますが、差動増幅器で特に気をつけないといけないのは入力段トランジスタに発生する“相対バラツキ”です。

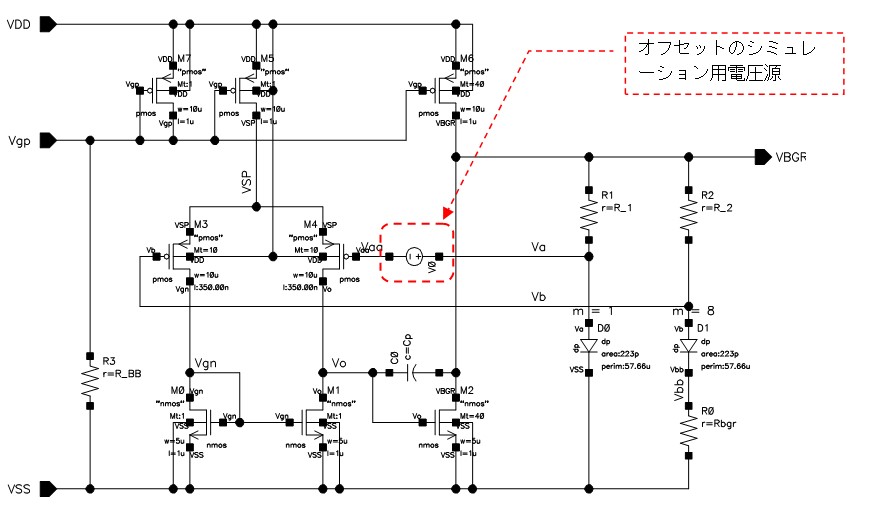

これらの製造上のバラツキは、“モンテカルロ解析”でシミュレーションすることが出来ますが、上の図のようにシミュレーション用に電圧源を追加することで簡易的に確認出来ます。

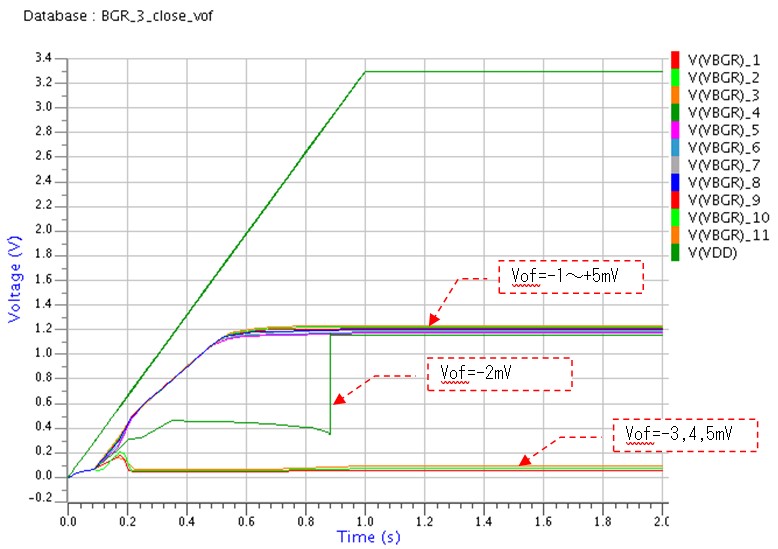

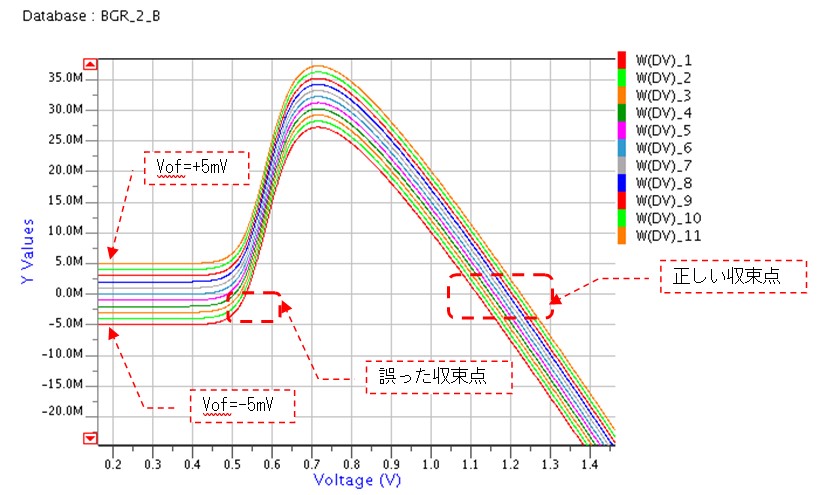

図 2はオフセット電圧をパラメータにして、電源をゆっくり起動したときの様子です。

オフセット電圧が、-2mVより低いときはきちんとBGR電圧が起動できていません。

CMOSトランジスタのVthには5mV程度のオフセットが普通に発生しますので、このまま作ってしまうと半分近くのデバイスはBGR電圧が起動出来ずに不良となってしまいます。

オフセットがあるとなぜ起動できないかというと・・・

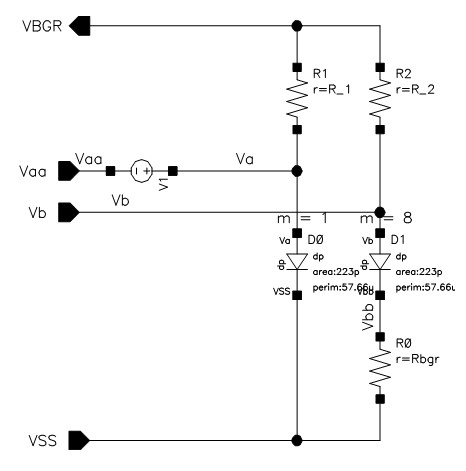

BGRの基準部分にオフセットつけた回路だけのシミュレーションをしてみると分かります。

(オフセットはアンプの入力段のトランジスタに発生するのですが、等価的に基準部にオフセットが発生し、アンプは理想的に出来ているとしたほうが、わかり易いです)

VBGRに電圧を加えたときに各部の特性は上の図の様になっていて、VaaとVbが等しくなる点で収束します。(VaaとVbが等しくなるようにアンプはVBGRを制御します)

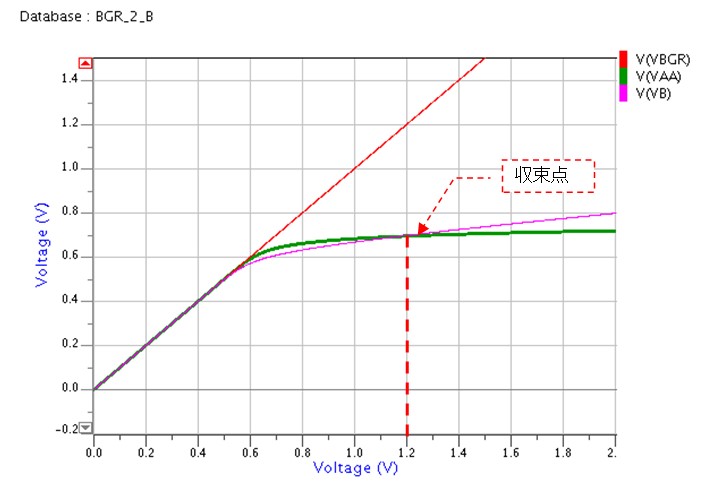

VaaとVbの差電圧をプロットすると図 5の様になります。

(オフセット電圧Vofを-5mVから+5mVまで1mV刻みの変化させた結果です)

期待している動作は、横軸が1.2V付近に収束する(差電圧=0となる)わけですが、0.5V付近にも差電圧=0となる収束点があります。Vofが正であれば誤った収束点は発生しないのですが、負の場合に発生します。

こちらに収束してしまうとBGRが起動できない事となってしまいます。

次回は、この誤った収束を起こさないようにするための対策(スタートアップ回路)を紹介したいと思います。

コメント

この記事へのコメントの受付は締め切りました。