こんにちは。今日はDRAM,SRAM, フラッシュメモリなどの低消費電力化についてお伝えします。

活性化領域の最小化技術とは?

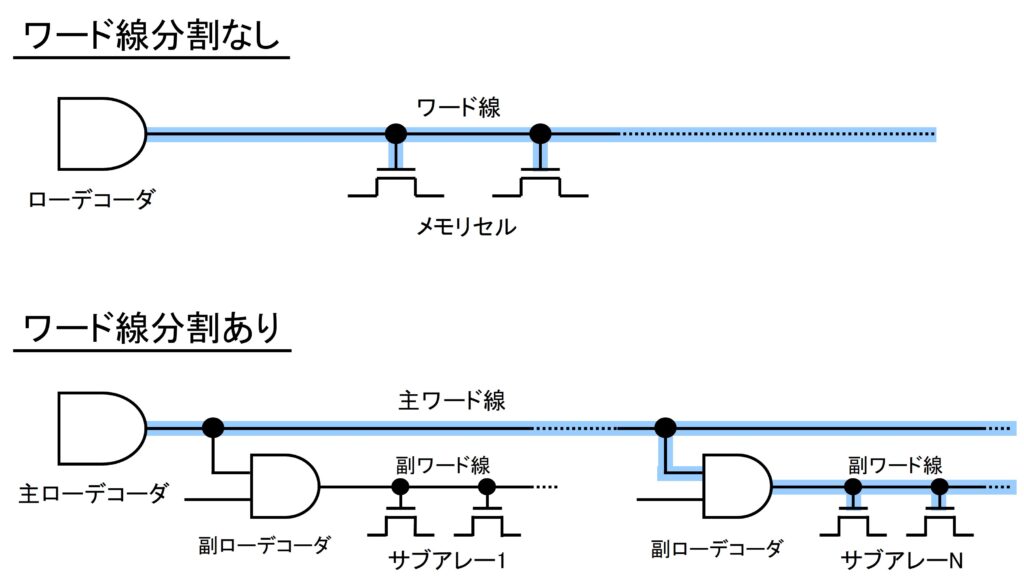

DRAM、SRAM、フラッシュメモリ等のメモリでは、ワード線およびビット線分割によるアレー分割によって、その空間的活性化領域を低減し、低消費電力化を図っています。携帯機器等に使用されるプロセッサでは、プロセッサを構成する各機能ブロックへのクロックの供給を必要に応じて断続的にコントロールするパワーマネジメントによって低消費電力化を図っています。こうした活性化領域の最小化技術について説明します。

ワード線分割

ワード線分割の原理を図9※に示します。ワード線を分割してN個のサブアレーに分ける事により、1本のワード線に接続されるセル数を1/Nに減らします。1個のサブアレーのみが活性化されるので、低消費電力化が図れます。

※原理を示したもので、現在実践されるワード線分割は多様化しています。

フラッシュメモリのプログラム動作時の様に高電圧パルスが必要な場合は、上図の副ローデコーダに増幅器の役割も担わせて、高電圧系の活性化領域を減らし低消費電力化を図る事もできる。ビット線についても同様に階層化する事により、同様の効果が得られます。

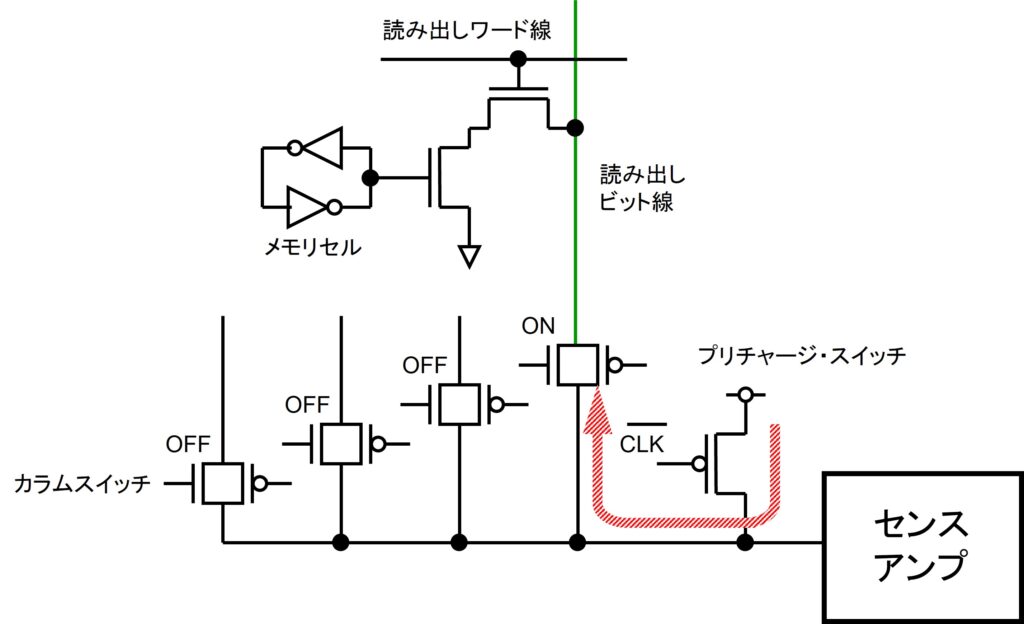

選択的ビット線プリチャージ

選択的ビット線プリチャージは、ASICにおけるRAMやROM等で用いられている技術で、その原理を図10に示します。

本方式のコンセプトは読み出し動作において選択されたビット線のみプリチャージして、低消費電力化を図る事です。プリチャージはカラムスイッチを介してセンスアンプ側から行います。読み出し動作で選択されていないビット線は、カラムスイッチが閉じているため、プリチャージされず、活性化領域の最小化=低消費電力化が図れます。

以前に画像処理に使うMPEG2ビデオコーデックLSIを開発したことがありますが、従来版ではLSIの全消費電力の2/3をデュアルポートRAMが占めていたのですが、この選択的ビット線プリチャージ方式を用いる事によって、RAMの消費電力を1/3以下にする事に成功し、600mWという低消費電力のMPEG2ビデオコーデックチップを実現したことがあります。

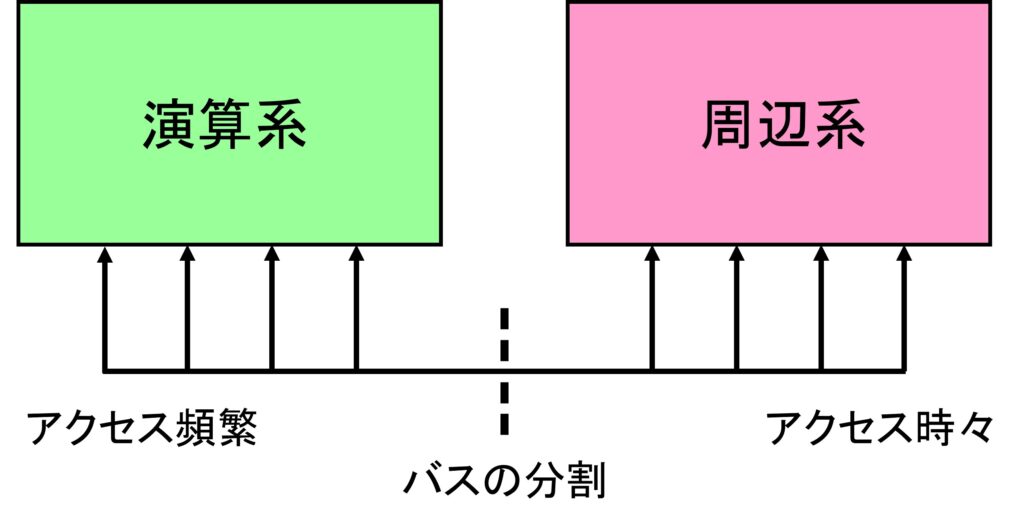

バス分割

現在のMPUやDSPでは、そのメインバスがチップ全体に及んでおり、より大きな容量値を持っていることが多いです。こうしたチップではDCTやディジタル・フィルタ等の処理を行う時、積和演算がくり返し行われますが、この積和演算はALU及び乗算器とレジスタとのデータのやりとりが頻繁で、しかもそれをメインバスを介して行うため、大きな容量ノードであるメインバスの活性化率が上がってしまい、消費電力的に問題となっておりました。その解決策であるバス分割を図11に示します。

バス分割では、あたかも得意な機能の異なる右脳と左脳を脳梁で分けるように、積和演算を行うアクセスが頻繁な「演算系」とアクセス頻度が高くない「周辺系」とを分割する事によって低消費電力化が図られています。

次に、DRAM混載SOCについて事例を折り混ぜながら解説していこうと思います。

コメント

この記事へのコメントの受付は締め切りました。