今日は電源などに広く使われているBGR(Band Gap Reference)について今回は触れてみたいと思います。

Band Gapと言われても、Bandとは? 何と何のGap?などの疑問が出てきますが、その辺りの歴史は良く知りません。ただ、Referenceと言うことから”基準“であることに間違いはないです。

基準電圧を作るには電源電圧を使う(抵抗で分圧して欲しい電圧を作る)のが一番簡単なのですが、電源電圧が変化すると、基準電圧も変わってしまいます。

回路設計をしていると、コンパレータの閾値や電流源の電流値など、電源が変化しても変って欲しくない値が必要になってきます。

こういった値を回路の中で作るには基準となるものが必要で、BGRが良く使われます。

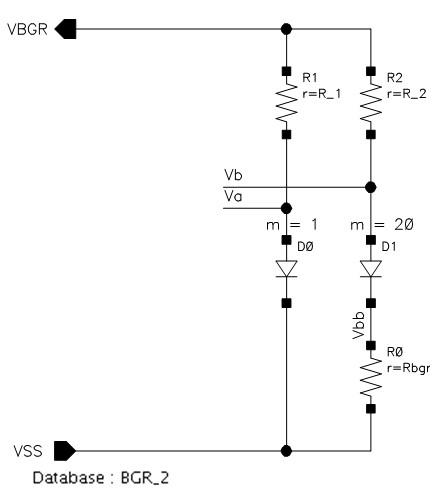

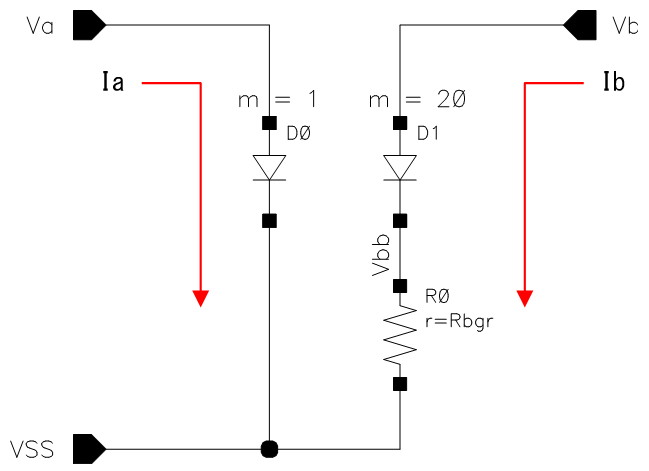

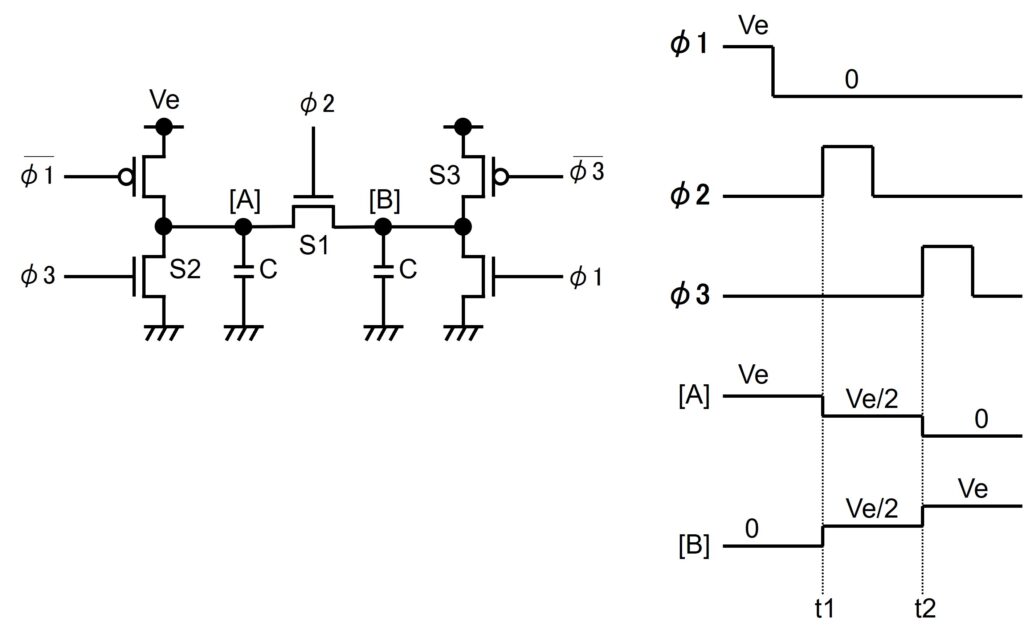

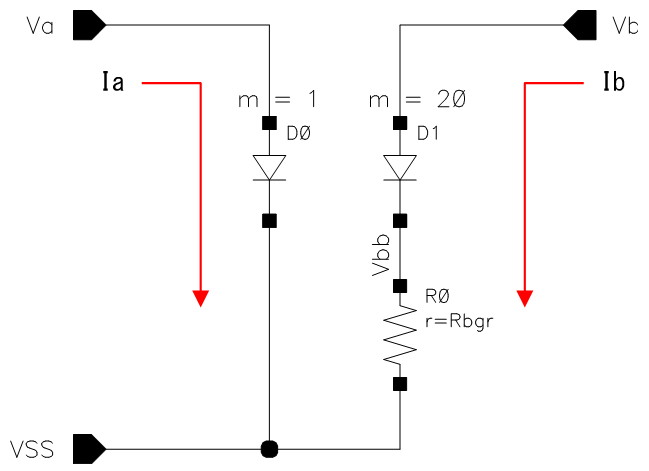

図1 BGR

図1 BGR

BGRを作っているのは図 1にかいた2つのダイオードと抵抗です。

特徴的なのは、抵抗が付いている側のダイオードは並列なのですが、抵抗がないほうは1つです。

この回路のVa,Vbに同じ電流を流した時に、Va,Vbの電圧を見て見ると、次のようになります。

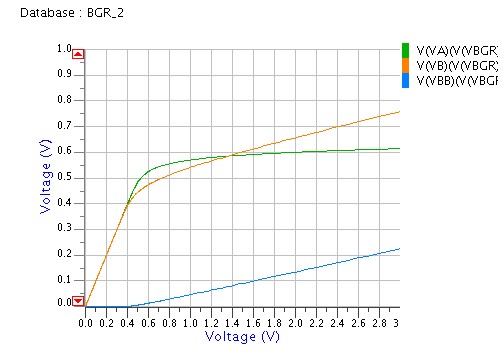

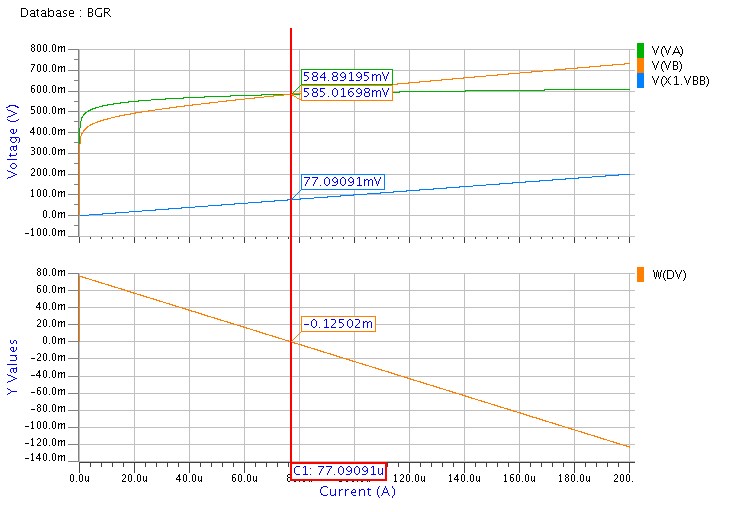

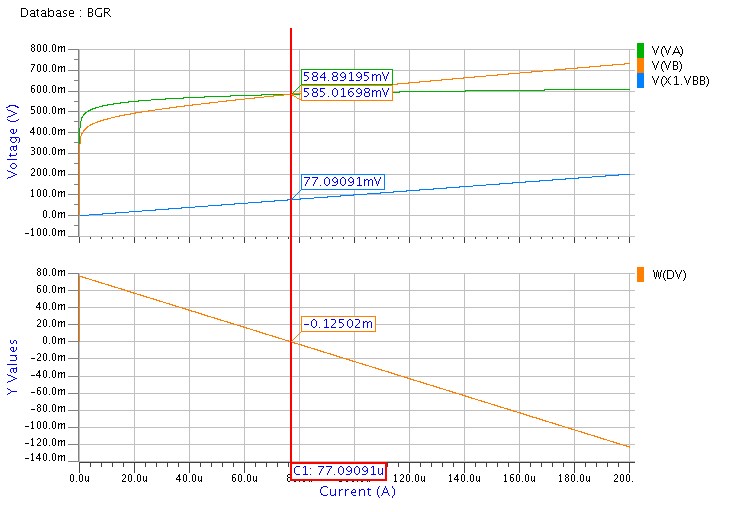

図2

図2

ダイオードしか付いていないVa(緑の線)はあまり傾斜が無く比較的平らになります。(つまり、電流が流れてもあまり電圧は変化しません)。一方で抵抗が付いているVb(オレンジの線)は傾斜を持っています。(抵抗があるので、電流が増えれば電圧も増えます)。

このVaとVbの交わる点(縦の赤いカーソル)がBGR電圧を作り出しているのです。

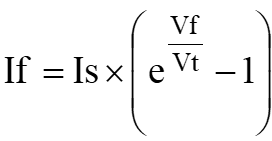

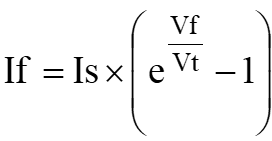

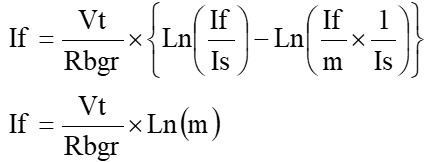

つまり、この交点となる電流は温度と抵抗値のみで決まっていて、電源電圧とは全く無関係なのです。計算式を使って説明しないと納得できない方もいると思いますので、やってみます。ダイオードの順方向電圧Vfと順方向電流Ifの関係式は、

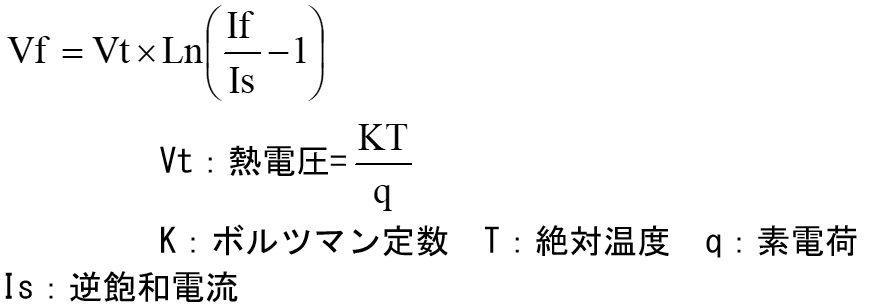

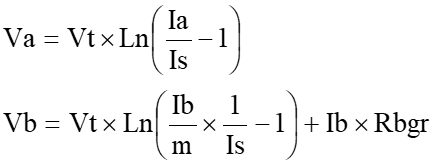

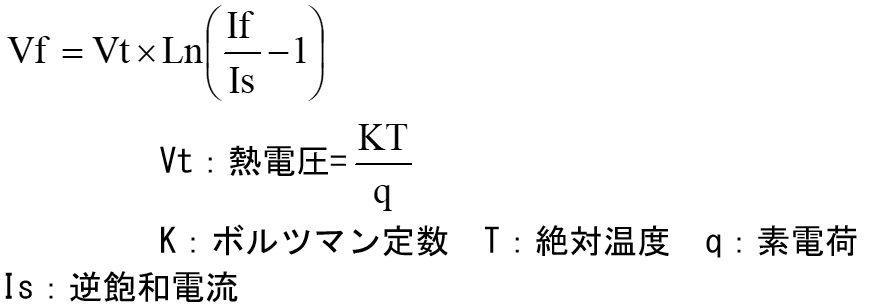

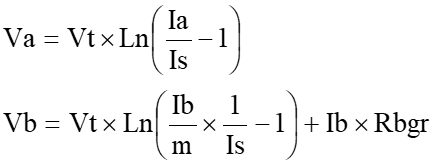

で表されて変形すると

となります。図 1の回路に当てはめると、

注)右側のダイオードは並列にm個並んでいるので、一個当たりに流れる電流はIb/mと成ります。

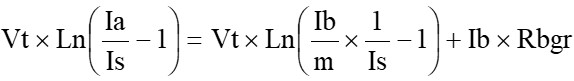

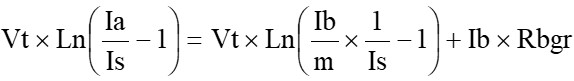

このVaとVbが等しくなる点の電流を計算すると、

と成りますが、逆飽和電流:Isは通常1e-15などと非常に小さな値をとるので、Ia>>Is、Ib>>Isから

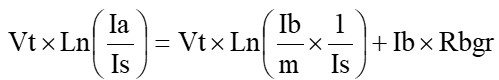

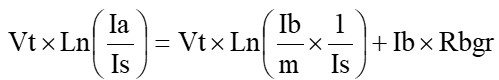

と近似できます。更にIa=Ib=Ifとすると、

を得ることが出来ます・・・VtとRbgrと定数しか残っていないです。

この式の凄い所は「電源電圧や電流がどこにも入っていない!」ことです。つまり、電流Ifは電源電圧や電源電流とは無関係に決まると言うことです。

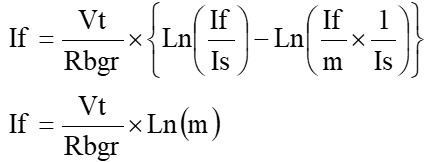

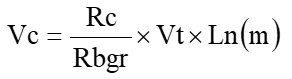

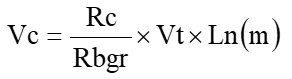

この電流Ifに抵抗Rcを付けた時に発生する電圧Vcは、

と成って、電源電圧とは全く無関係で、抵抗比 と定数Ln(m)とVt(つまり温度)に依存する電圧を作り出すことが出来ます。

と定数Ln(m)とVt(つまり温度)に依存する電圧を作り出すことが出来ます。

更にVtに依存する部分、つまり温度をキャンセルできれば、温度、電源電圧、素子の絶対値バラツキとは全く無関係な電圧を作り出すことが出来ます。

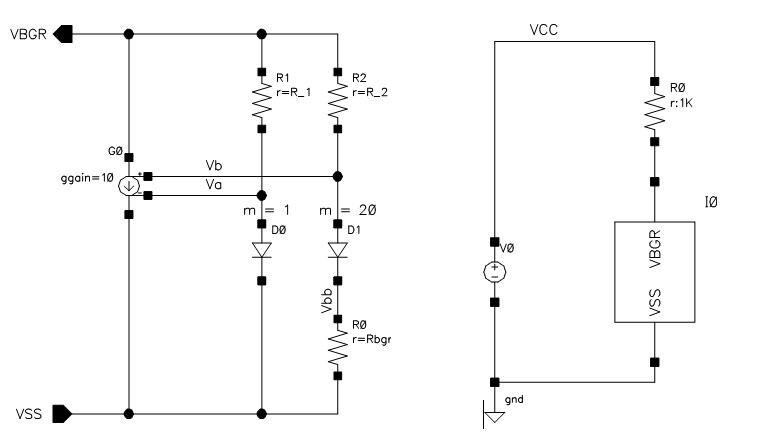

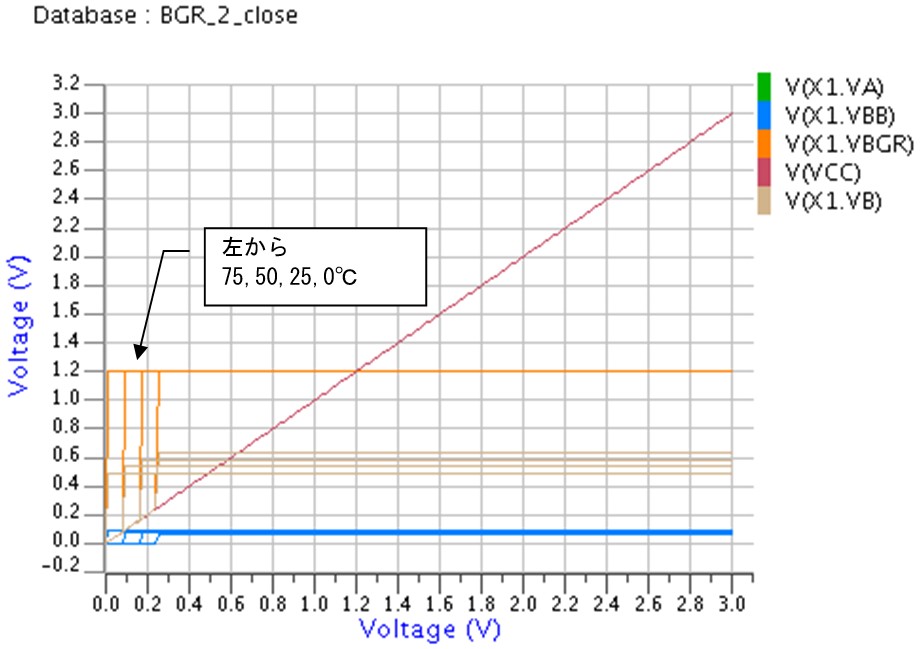

次回は、VaとVbを一致させる回路を含めて、BGR回路全体を紹介したいと思います。