CMOS LSIについての3回目です。

今日はLSIのデザインルール微細化に伴う低電源電圧化についてお話します。

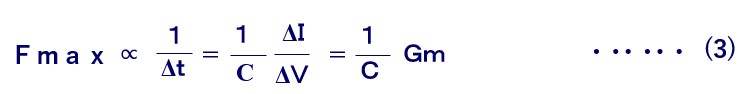

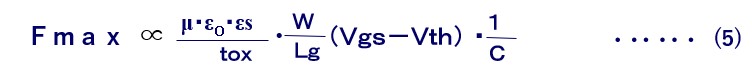

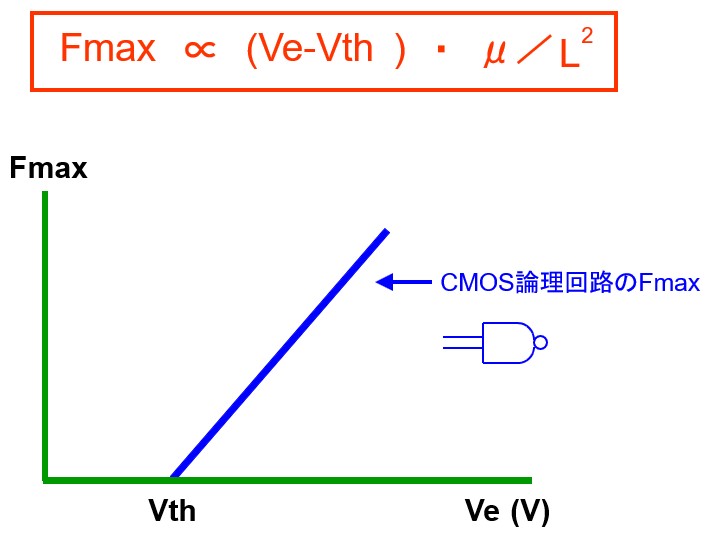

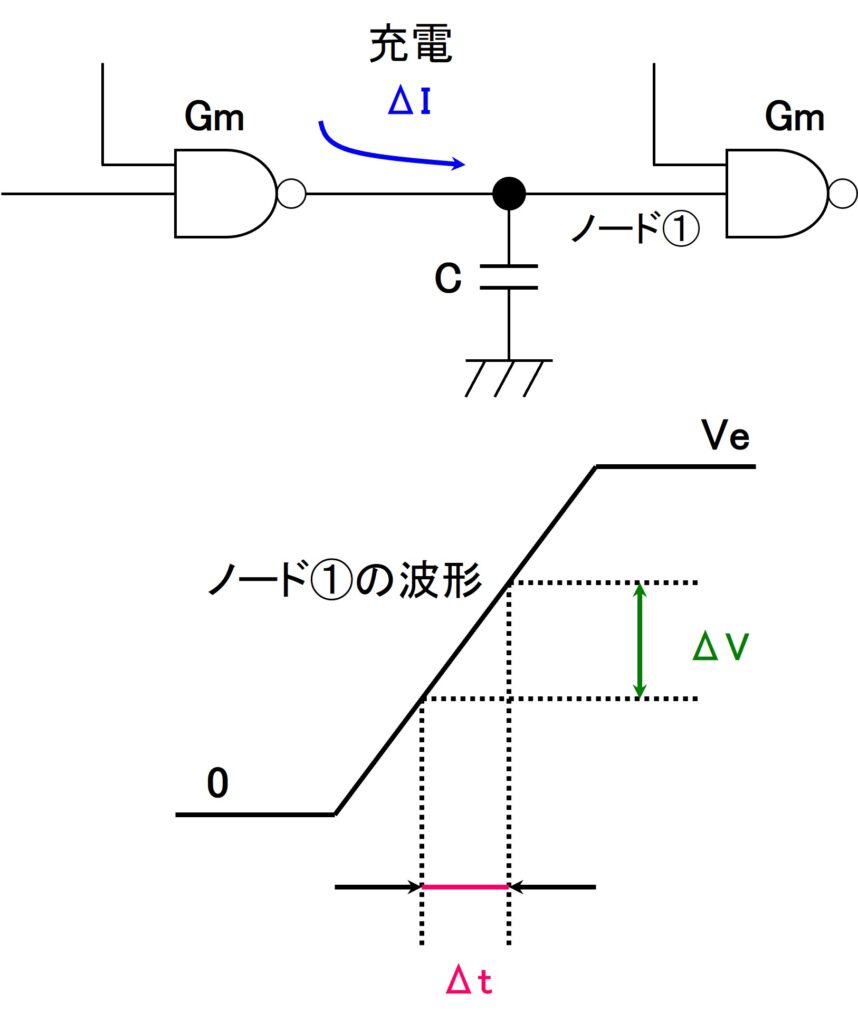

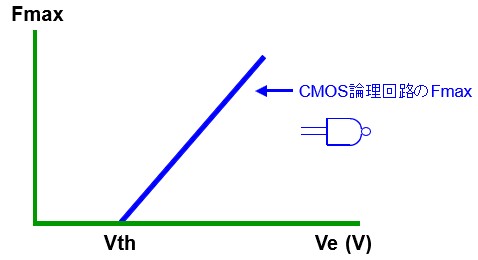

CMOSLSIの低消費電力化のためには、電源電圧Veの低減が最も有効であることは、前回記事でもお話した通りですが、最大動作周波数FmaxがVeに依存しているので、最大周波数も低下してしまうという問題がございます。これはどう解決したらよいのでしょうか。

デザインルール微細化に伴う低電源電圧化

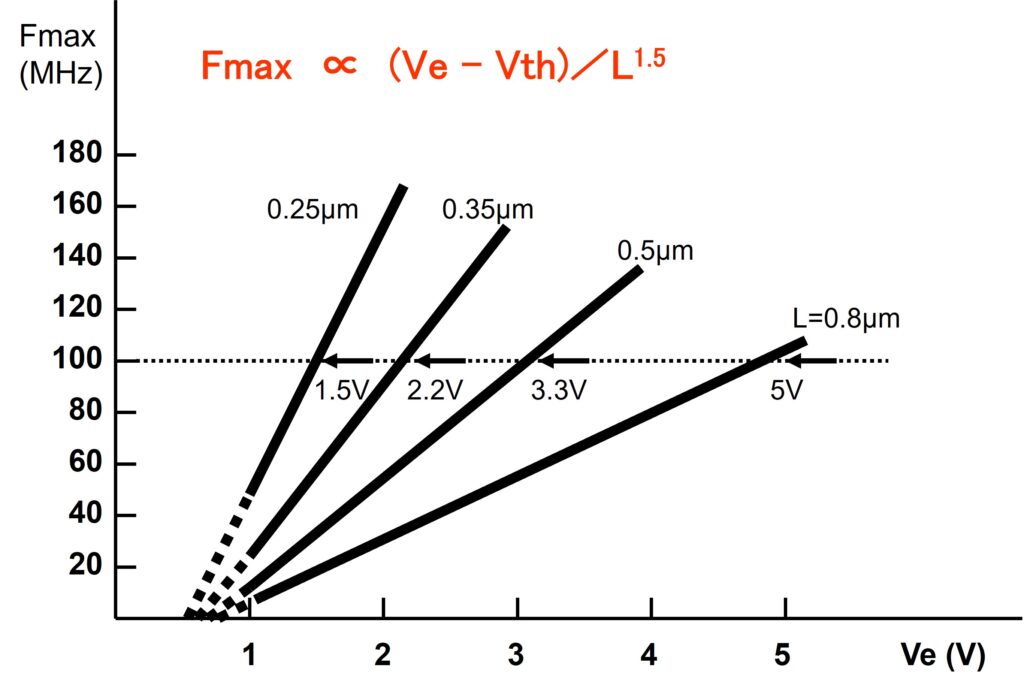

CMOSプロセスは、3年(1世代)でデザイン・ルール“L”が0.7倍にスケールダウンされるので、前回お示しした(7)式の分母のL1.5が小さくなります。

これは図4のVe-Fmax特性の勾配が大きくなる事を意味し、同一電源電圧であれば3年で約1.7倍の高速化を図れることになります。

別の言い方をすれば、ある周波数Fxを動作させる電源電圧は3年で2/3にできる(図5)。さらにスケールダウン則に伴う容量低減も考慮すると消費電力は3年で1/3にする事ができる。

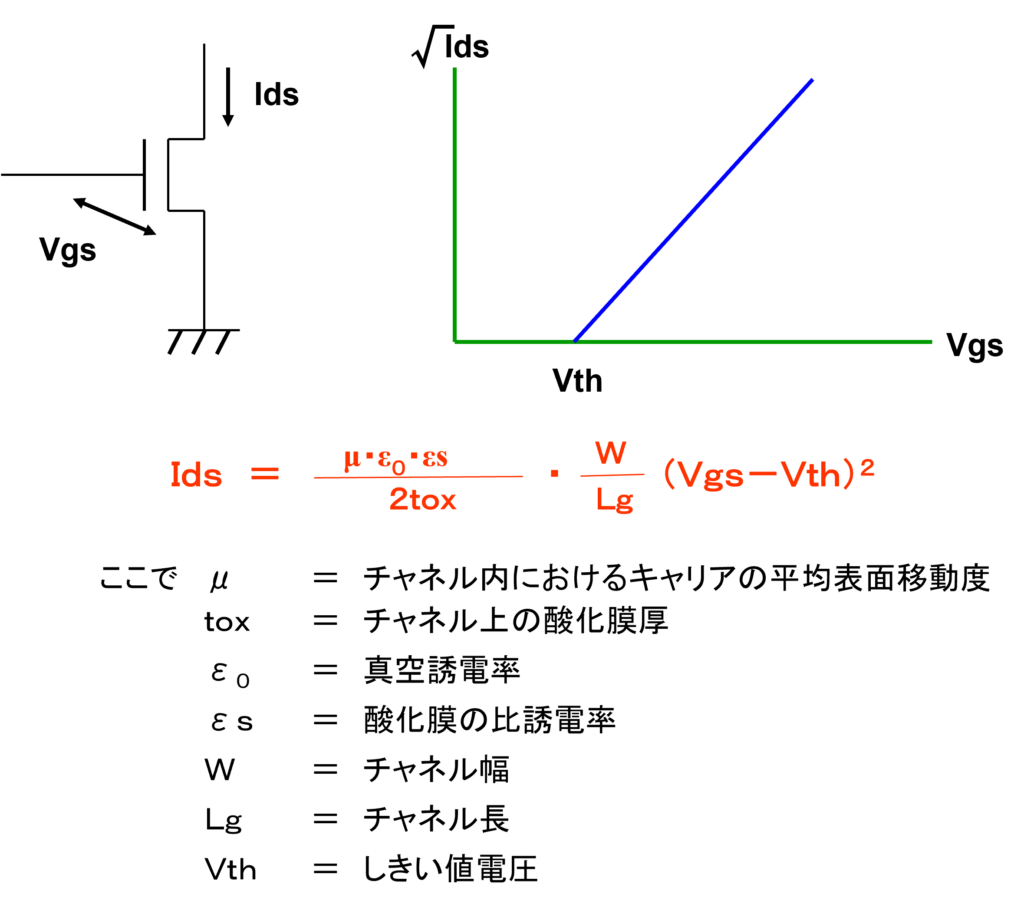

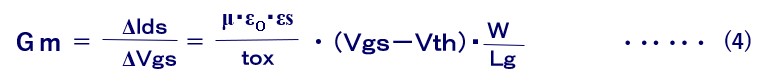

すなわち、デザイン・ルール“L”の微細化に伴い、キャリアの移動度の速度飽和現象およびホットキャリア耐性の問題が発生し、MOSトランジスタの最高性能を発揮する電圧、いわゆる「最良電圧」は低電圧化していく、という事になります。

最大動作周波数 Fmaxの温度特性について

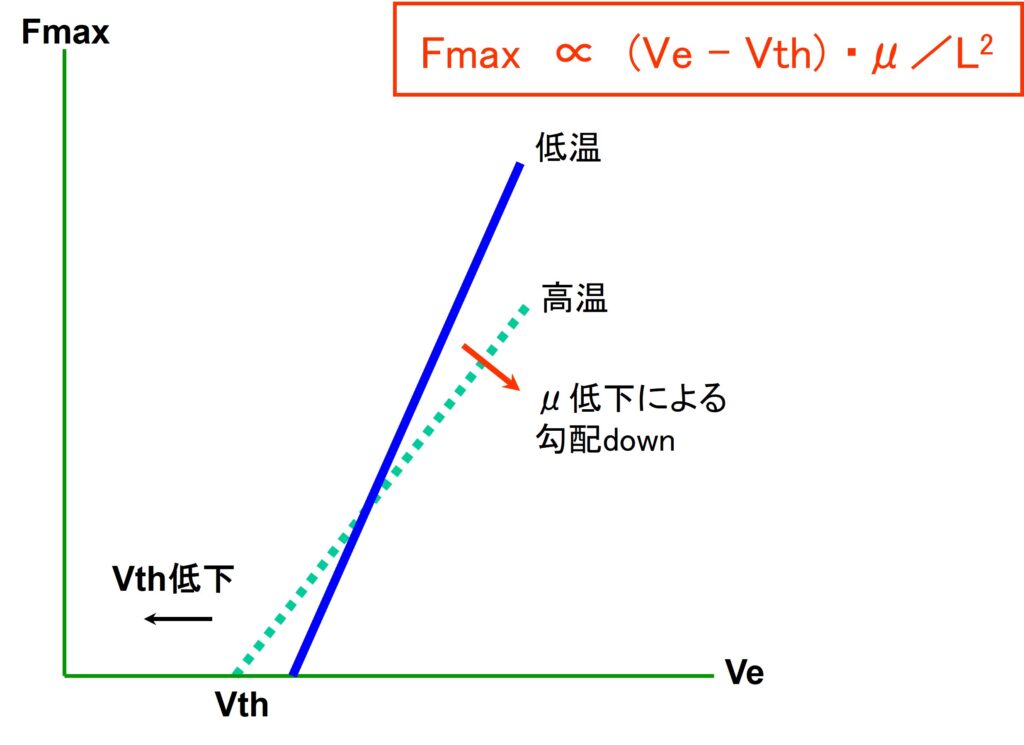

低電源電圧動作では、Fmaxの温度特性に注意する必要があります。(6)式を高温および低温について図示すると図6となります。

高温環境ではキャリア移動度が低下するため、キャリア移動度μは負の温度係数を持っている。また高温環境では印加ゲート電圧に対してウェルにチャネルができ易くなるので、Vthは負の温度係数を持っている。

以上からFmaxの温度特性は、「高い電源電圧では低温環境の方が、低い電源電圧では高温環境の方が高速化する逆転現象」が起こります。プロセスによっても依存いたしますが、一般にVdd=1~1.5Vの間に温度係数ゼロの点が存在するようです。

CMOS LSIで高速応答性を維持しながら、低消費電力化を図る

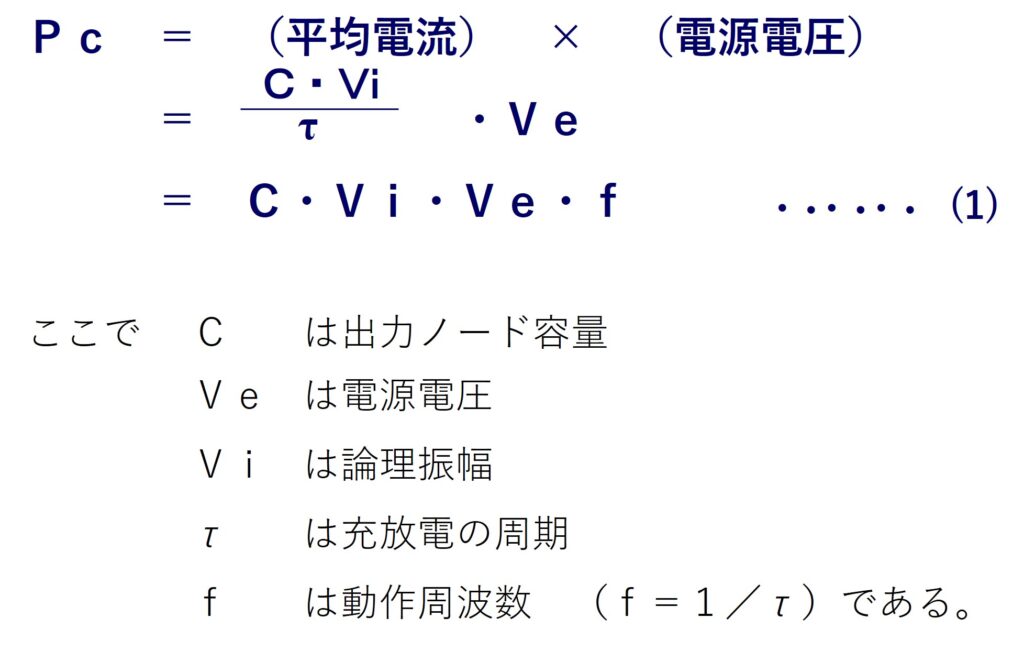

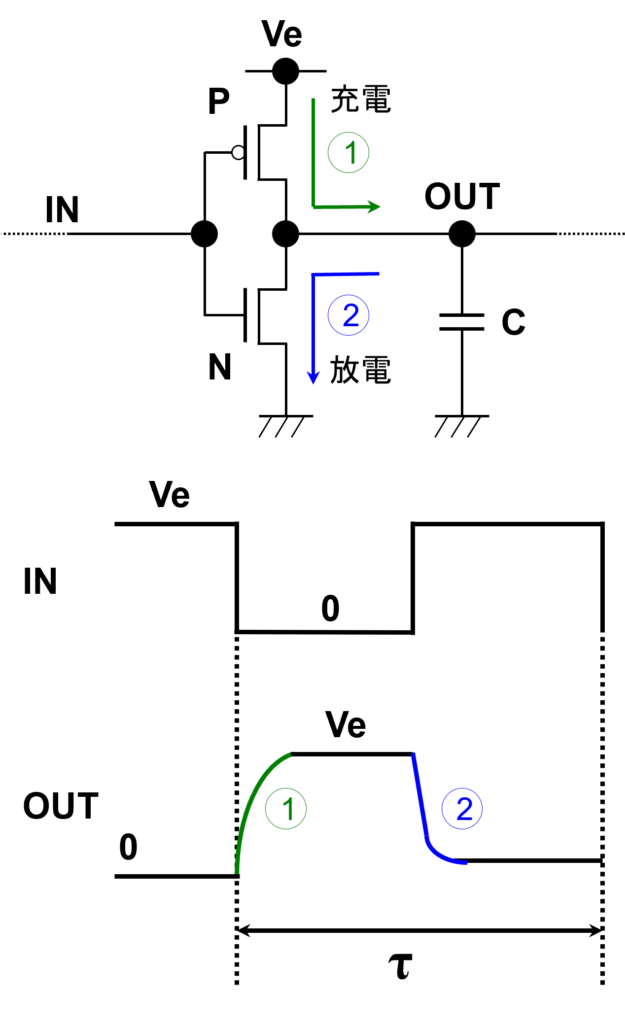

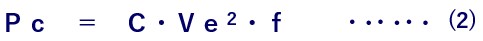

CMOS・LSIの設計において、その高速性を維持しながら、低消費電力化を図る事が重要である。ここで、(1)式に示した消費電力の式を再度(8)として示します。

Pc = C・Ve・Vi・f+Ve・Idc ・・・・・(8)

ここでIdcはDC電流成分で、センスアンプの電流源、ダウンコンバータのバイアス電流、低しきい値MOSトランジスタのサブスレッシュホールド・リーク電流等です。

LSIの低消費電力化とは、所望の動作をさせながら、(8)式の各項の値をいかに低減するかの技術です。その代表的な技術について、また次の記事でご紹介いたします。