この記事では、システムLSIの低消費電力化技術の1つとして、一世を風靡した8ミリビデオ・カムコーダ用に開発したDRAM混載SoCについてお話します。

8ミリビデオカムコーダとは?

使ったご経験がある方おられると思いますが、個人がテープに録画記録するビデオカメラで、運動会で活躍するお子さんをこぞって撮影するお父さんたち、旅行先で動画撮影のために持ち歩く旅行スタイルなど、当時の生活の楽しみ方を根本から変える画期的製品でした。持ち歩いて長時間撮影したいと、より軽量かつ小型なカムコーダを市場から求められましたので、それを実現するための技術開発が行われました。

当時のマルチメディア画像処理の仕組み

画像処理を中心としたマルチメディア信号処理では、大容量メモリ(フレームメモリ)とロジックとの信号のやりとりが特に頻繁になります。

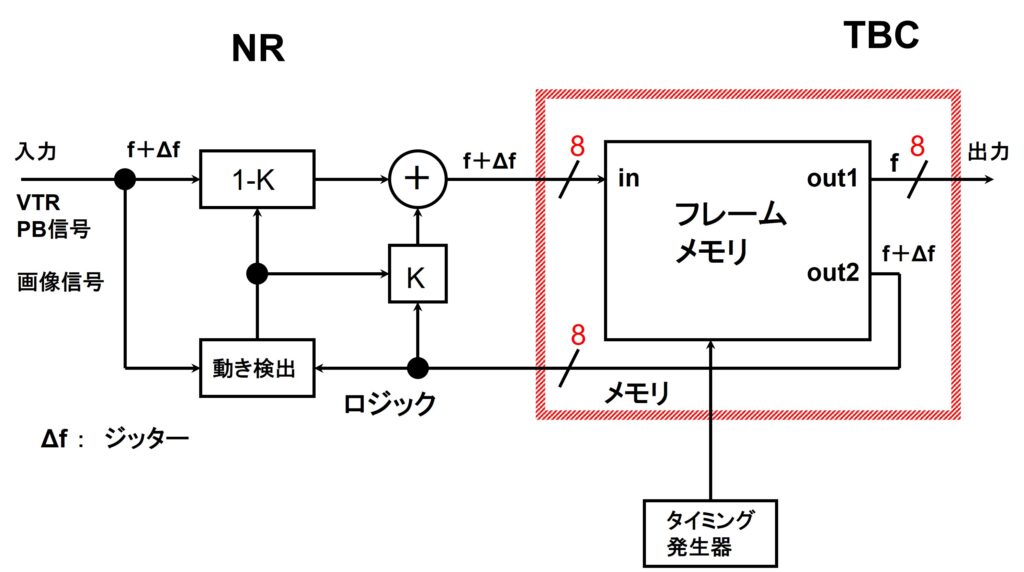

カムコーダでは画像処理のために、「ノイズ・リデューサ+タイム・ベース・コレクタ」略してNR+TBCシステム(図12)を用いていました。入力であるVTR(録画映像)のPB信号は、録画テープを回転させるドラムの回転ムラ等に起因した時間的な「ゆらぎ」、Δfジッターを持っています。映像をきれいに残すためにはSN比の向上を図るNRが重要で、これを実現する為に「ジッターを持った」1フレーム前の信号との相関を利用します。これがNR+TBCシステムです。

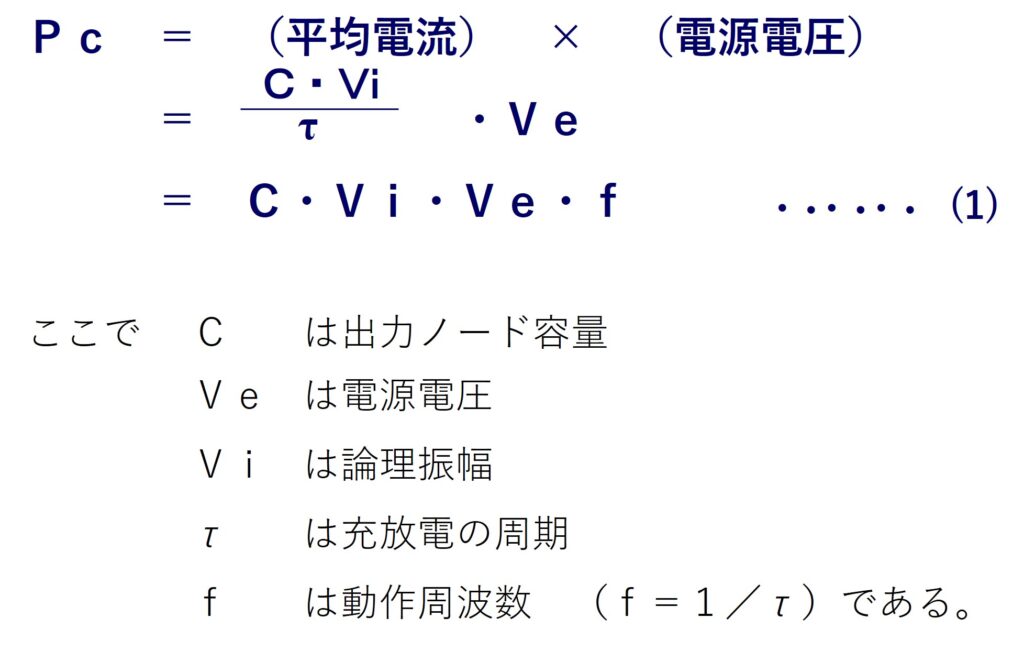

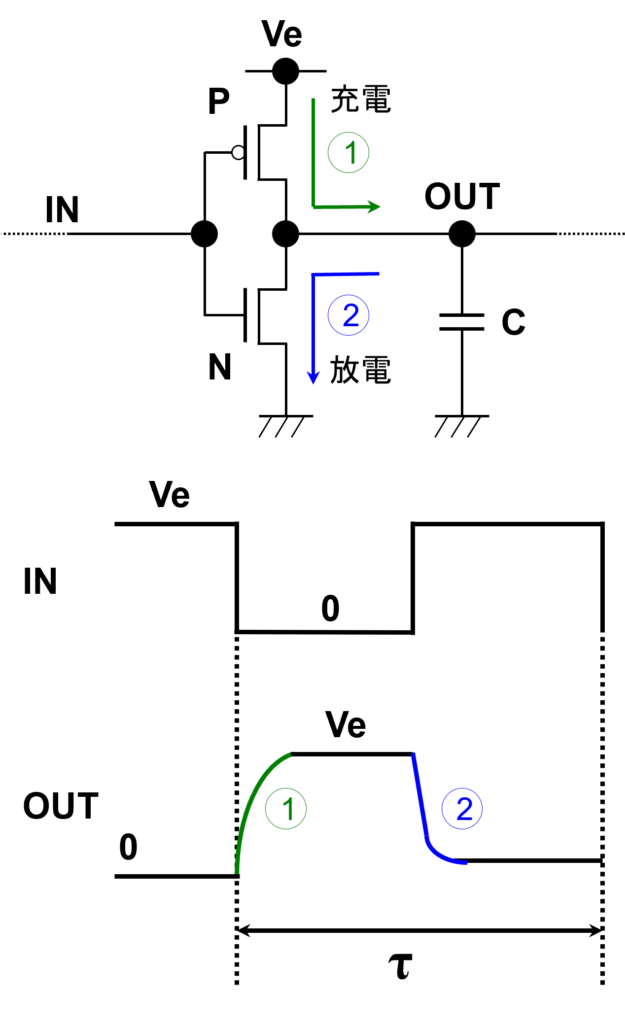

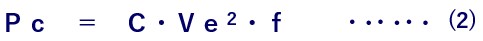

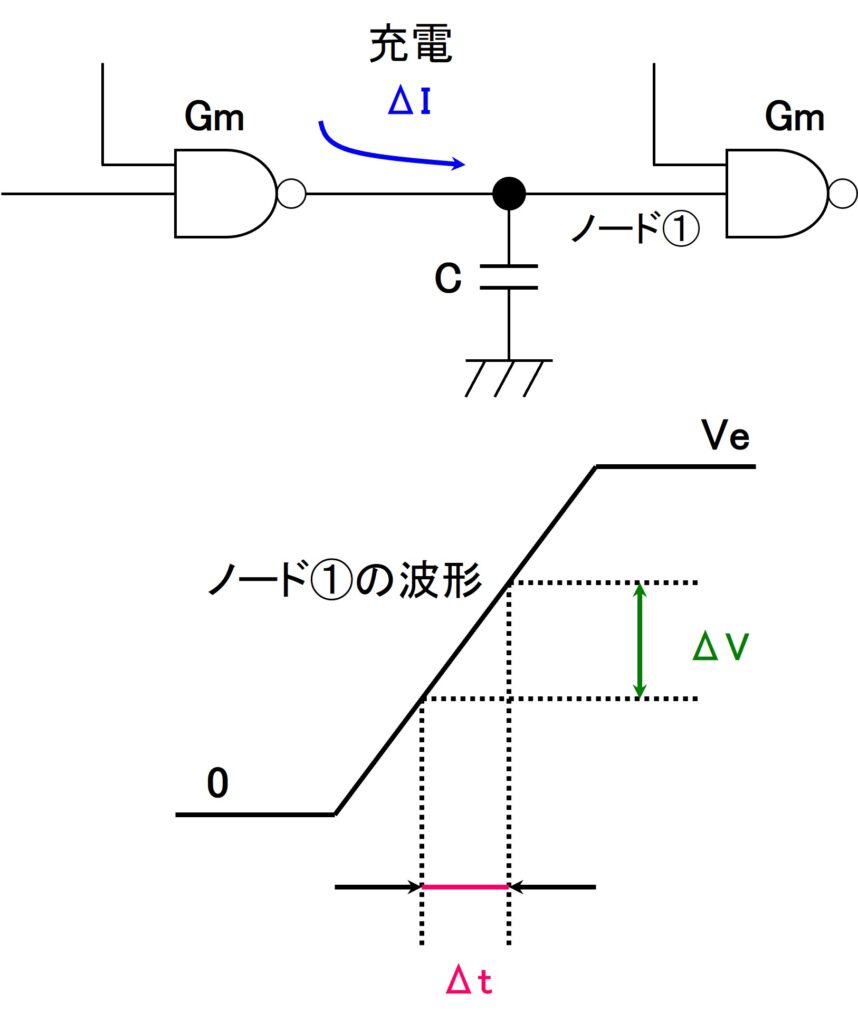

1フレーム前の相関を利用するためにはフレームメモリからTBCされたジッターの無い信号を出力する必要があります。しかし、各々8ビットのビデオ・データともなると、NR+TBCの処理だけでも、メモリとロジックとで、24本のデータラインが13.5MHzのサンプリング・レートで結ばれることになり、消費電力が高くなってしまいます。

ロジック+DRAM混載のSoCの必要性

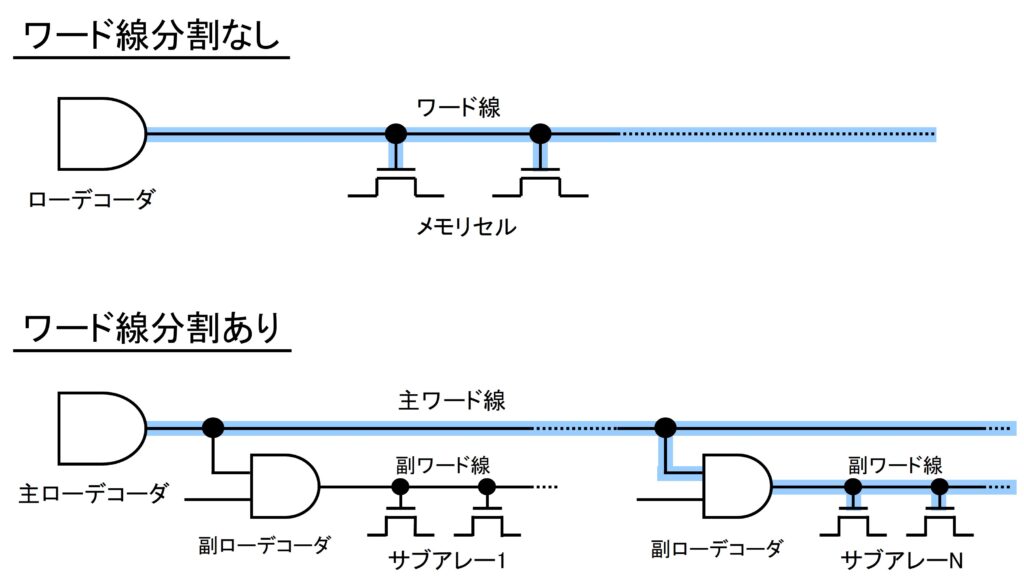

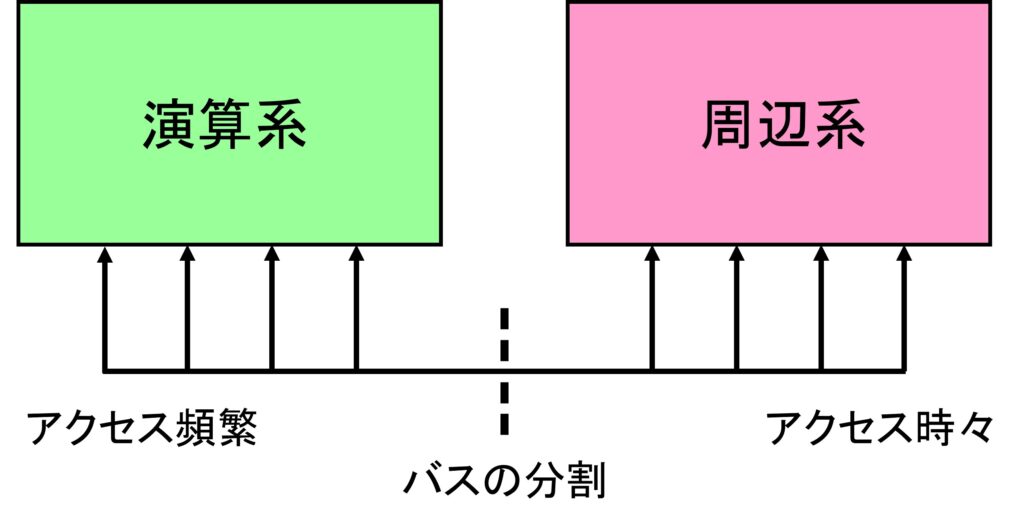

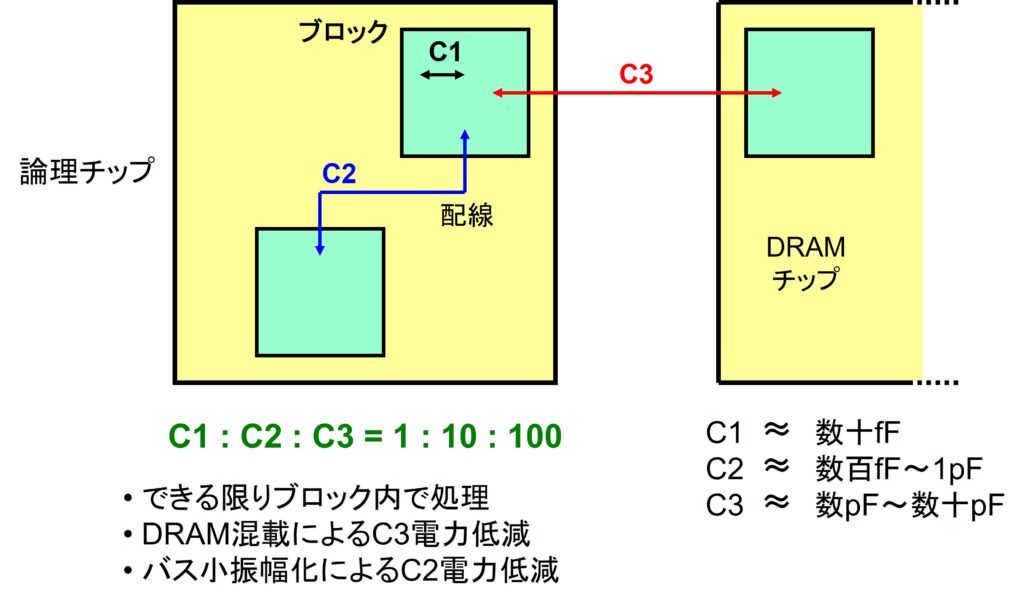

当時はフレームメモリ(DRAM)とロジックとは別チップであり、その場合ピン間容量が大きく、消費電力の点で、携帯用機器としては大きな問題でした。通常LSIのブロック内、ブロック間、チップ間の配線部分の容量比率は、おおよそ1:10:100(図13)であり、ここまでのピン間容量比率であればもう信号処理ロジックとフレームメモリとを同一チップに入れる方が、消費電力的に圧倒的に有利です。そういう経緯から、ロジックとDRAMを混載した「システム・オン・チップ」(SoC)の新規技術開発およびその実現プロセスが必要となったのです。

これから先のマルチメディア信号処理

今回はDRAM混載による消費電力削減の重要性について、お伝えしました。その後ビデオ撮影のできる製品は携帯電話、スマホな高解像度で撮影できる製品は増えましたが、これから先の画像処理においても、さらなる高解像度化への要求は続くはずです。特に画像圧縮/伸長、画像認識、3次元グラフィックス等が主役となるマルチメディア信号処理では、今後もメモリ中心の処理が避けられないはずです。こうしたことからも、DRAMプロセスをコアとしたDRAM・ASIC混載プロセス技術が今後重要になるのではないかと想定しています。

次は、低消費電力化を実現するアーキテクチャの工夫について、書きたいと思います。