CMOS LSIの強み

LSI(大規模集積回路)はCPUやメモリ、各種デジタル回路など、幅広いアプリケーションで使用されており、現代のエレクトロクス製品になくてはならない技術です。

LSIに搭載するトランジスタを小さくたくさん並べ集積度をあげるほどLSIの演算性能は上がるのですが、様々な課題が発生します。LSIの動作周波数を上げればトランジスタの処理速度は上がりますが、消費電力も上がります。トランジスタは0と1を電気的に切り替えるスイッチなので、スイッチを動かせば動かすほど当然電力消費が増加します。

CMOS LSIは、こうした課題に対処できるように、低消費電力でありつつ高速応答性がその特徴です。このブログでは、どのようにCMOSの技術特性を活用し、高い応答性能をどのように引き出していったのか、数式や図を使ってご紹介していきたいと思います。

CMOS LSIの Pc(消費電流)の求め方

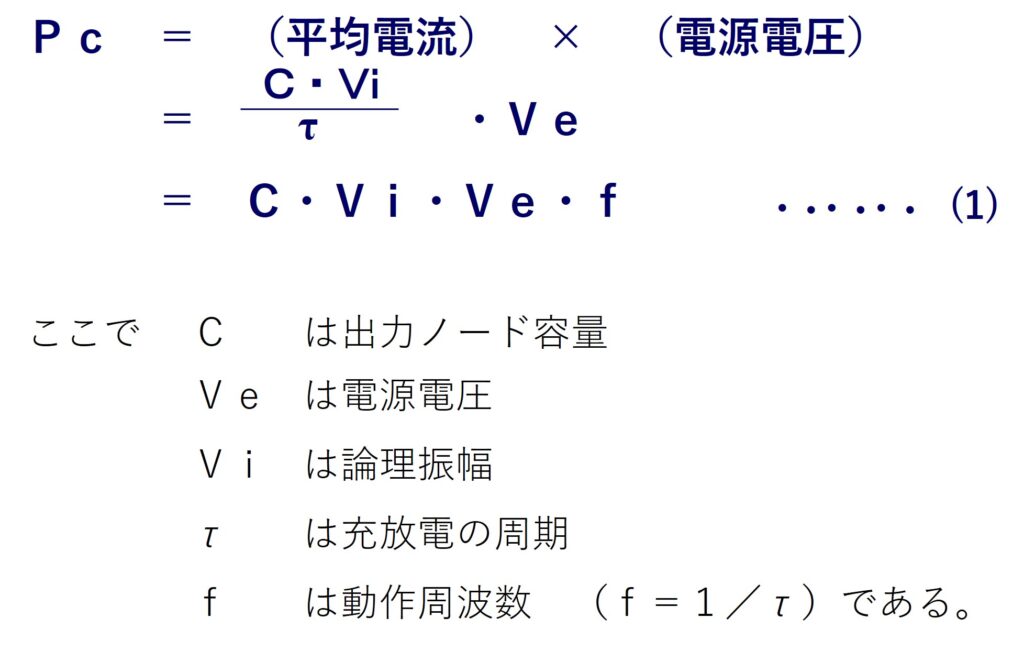

さて、CMOS LSIの中で、電力はどのように供給され、どのように使われるのでしょうか。数式によって導き出してみます。まず始めに、CMOS LSIのPc (消費電流)の求め方式にまとめてみました。これは式(1)のように示すことができます。

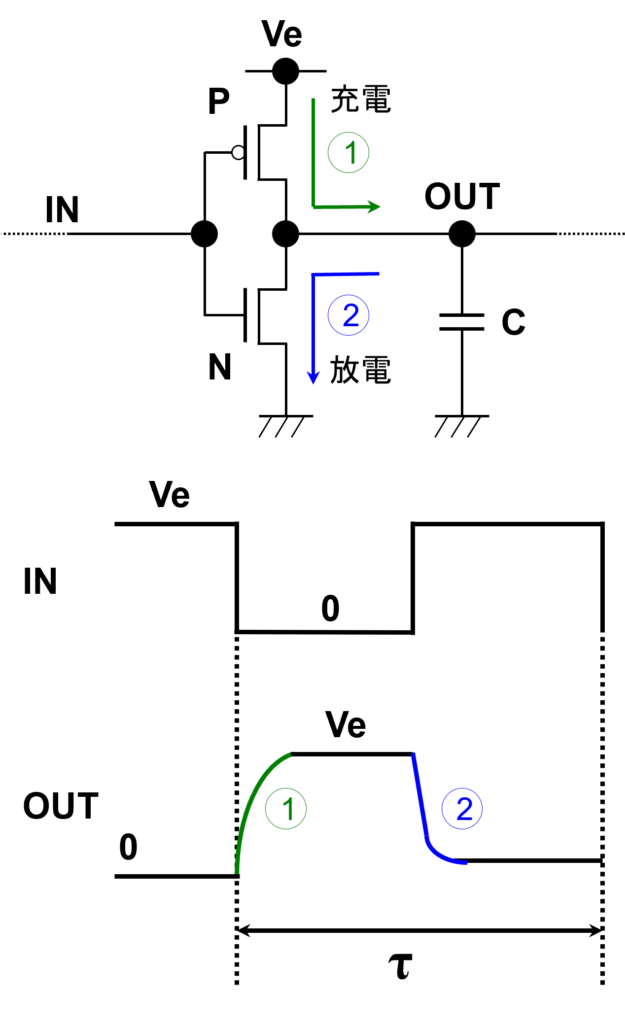

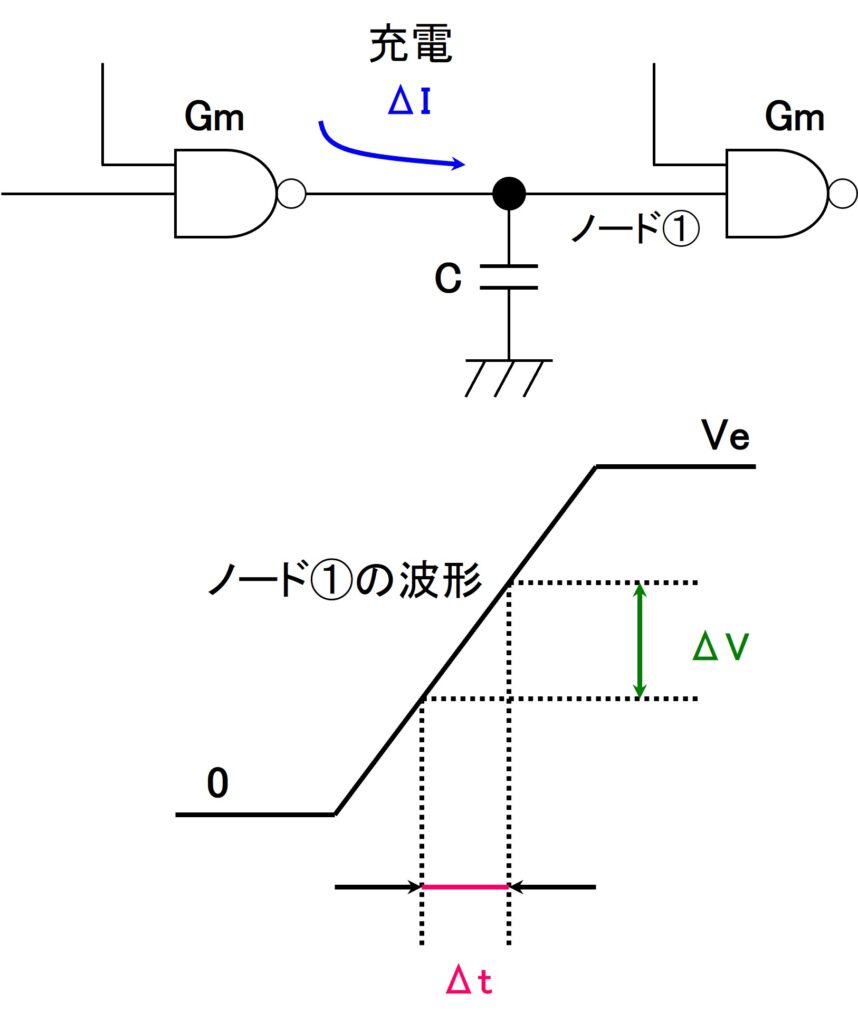

次にCMOS LSIのトランジスタで起きている電流の動きについて図1に示しました。

CMOSのMOSとは「MOSトランジスタ(金属酸化膜半導体トランジスタ)」のことで、このMOSトランジスタにはNチャネル型とPチャネル型があります、CMOS LSIはこれらのトランジスタを組み合わせて構成されます。LSI内部ノードおよび外部ピンの容量を充放電する際、この図で「P」と書いているPチャネル型MOS(PMOS)で充電し、「N」と書いているNチャネル型MOS(NMOS)を用いて放電されます。

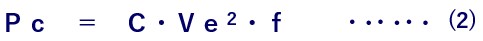

一般にCMOS回路はフルスイング動作なので、Vi=Veとなります。したがって消費電力は式(1)を変形して、式(2)でも表すことができます。

すなわち消費電力Pcは電源電圧Veの2乗に比例するので、電源電圧Veの低減が低消費電力化に最も有効であることがわかります。

Fmax(最大周波数) の求め方

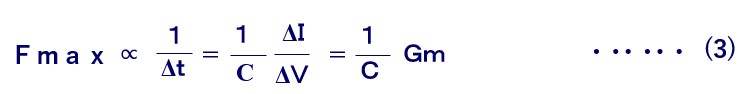

つぎに、最大動作周波数 “Fmax”についてです。

図2でCMOS LSIの内部を簡易的に示してみました。ここで“Fmax”は、図2の”ノード①” をいかに早く充電できるかに等しいので、式(3)で表すことができます。

ここで想定していただきたいことがあります。単に電源電圧Veを下げると、CMOS LSIの最大動作周波数Fmaxが低下する問題が生じます。CMOS LSIの技術では、低消費電力でありながら高速応答性が保てることが特徴ですから、そのあたりを解決していく術であります。

次回は、電源電圧Veと最大周波数Fmaxの依存関係についてもう少し深く説明していきます。

コメント

この記事へのコメントの受付は締め切りました。