本章では、前章で解説したΔΣ ADCのシステム設計工程(①〜④)を1章ずつ掘り下げて解説していきます。

第6章 仕様の決定

前章で示したように、ΔΣADCの設計は 「仕様 → OSR・次数 → NTF → モデリング」 の順で進めることが重要です。このうち最初のステップである「仕様の決定」は、後続の設計全体に影響するもっとも重要な工程です。

ここで求められるのは、単なる「〜bitが欲しい」という要求だけでなく、帯域・SNR・最大入力といった総合的な性能要件を整理することです。

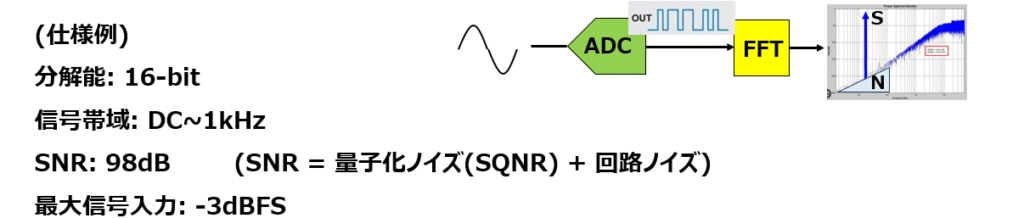

仕様例を上記に示しました。この仕様例を元に、代表的な4つの使用項目について説明します。

①分解能(Resolution)

まず求められるのは、最終的に達成したいディジタル分解能です。ここでは 16-bit を目標としています。

ただし、ΔΣADCでは「量子化bitの数 = 出力分解能」ではありません。1bitまたは数bitの量子化器からスタートし、OSR(オーバーサンプリング比)とノイズシェーピング効果により16-bit相当の性能を作り上げます。

このため、後の章で扱う OSR や NTF を設計するための“目安”となる項目です。

②信号帯域(BW: Signal Bandwidth)

今回の例では DC〜1kHz を対象帯域とします。この帯域が広いほどサンプリング周波数(fos)への要求が高くなり、OSRの選定にも直接影響します。

ΔΣADCは「高精度・低帯域」用途に向いているため、1kHz程度の帯域は典型的なユースケースといえます。(低消費で高分解能が求められるため、医療・計測・IoT用途と親和性が高い帯域です)

③SNR(Signal-to-Noise Ratio)

今回の仕様では SNR = 98 dB を目標値としています。

ここで重要なのは、SNRが 量子化ノイズ(SQNR)+アナログ回路ノイズの合計 で決まる点です。

ただしΔΣADCの設計初期では、

- 物理ノイズ(抵抗熱雑音など)

- 回路ノイズ(アンプの入力換算ノイズなど)

をすべて正確にモデル化して評価するのは困難です。

そこで設計初期段階では、

量子化ノイズだけを取り出した SQNR を基準に SNR を概算します。

SNR(dB)≈6.02B+1.76SNR(dB) \approx 6.02B + 1.76SNR(dB)≈6.02B+1.76

は理想的な量子化ノイズのSNRであり、B に 16bit を代入すると約 98 dB となります。

今回の設計例では、「回路ノイズはSQNRより十分小さく抑える」という前提のもと、SNR ≒ SQNR として 98 dB を目標値に設定しています。

④最大入力レベル(Input Range)

最大入力は –3 dBFS(Full Scale) に設定されています。

これは実際の信号がクリッピングする余裕(ヘッドルーム)を確保するための設定で、

後段のFFT解析や実装時のダイナミックレンジ確保にも影響します。

ΔΣADCでは、入力信号のレベル設定が

- 積分器の内部状態

- ループの安定性

- SNDR(Signal-to-Noise-and-Distortion Ratio)

に強く影響するため、この値を適切に設定することが重要です。

次章では、この仕様を用いて、オーバーサンプリング比(OSR)と変調器の次数の決め方

について具体的に解説していきます。

第7章 オーバーサンプリング比(OSR)と変調器の次数の決め方

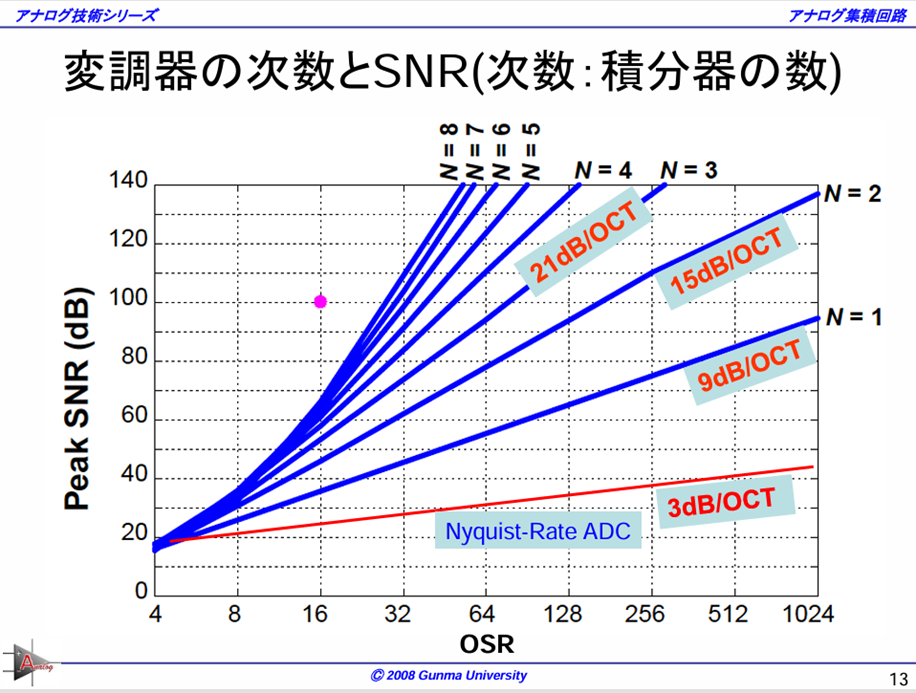

前章で設定した仕様では、ΔΣADCとして SNR = 98 dB を達成する必要があります。

この目標を満たすためには、

- オーバーサンプリング比(OSR)をどれだけ大きくするか

- 変調器の次数(1〜4次)をどう選ぶか

を適切に決める必要があります。

この説明をするために、群馬大のアナログ技術シリーズの解説がとても分かりやすかったので、引用させていただきました。

ΔΣ変調器では次数が1段上がるごとに帯域内ノイズの低減量が大きくなるという特徴があります。

図の傾きに書かれている

- 1次:9 dB/Oct

- 2次:15 dB/Oct

- 3次:21 dB/Oct

という数字は、「OSRを2倍にしたときに何dB SNR が改善するか」を表しています。

◆98 dBのSNRを得るためのOSR候補

図の曲線から、SNR = 96〜98 dB を達成するためのOSRと次数の組み合わせを読み取ると、代表的には次の2つが候補として挙げられます。

(A)OSR ≈ 100、3次(N=3)

(B)OSR ≈ 200、2次(N=2)

(A) 3次変調器はノイズシェーピング効果が強く、OSRが100程度でも約100 dB前後のSNRが得られます。

ただし、デメリットとしてループが複雑になり安定性確保が難しい、高次になるほど係数調整の難易度が上がる、という設計上の課題があります。

一方(B) 2次変調器では、OSR=200付近で100 dBに達しますが、2次はループが比較的安定で扱いやすく、アナログ回路も簡潔にできるというメリットがあります。

ここで、実装可能なクロック周波数 fos を 1 MHz 程度 と仮定すると、次の計算でOSRが求まります。

信号帯域(前章):1 kHz

OSR = fos / (fs/2) = 1 MHz / (2 kHz) = 500

本システムではOSR ≈ 500 が実現できる条件になるため、実装可能なクロック周波数や特性(2次の青いライン)から見て、(B)の2次変調器で十分に98 dB を達成できそうです。

最終的に採用する構成は以下のとおりとなりました:

◆ΔΣADC構成

- 次数:2次

- OSR:500

- fos(変調器動作周波数):1 MHz

長くなりましたので、システム設計の残りの工程は次回解説します。