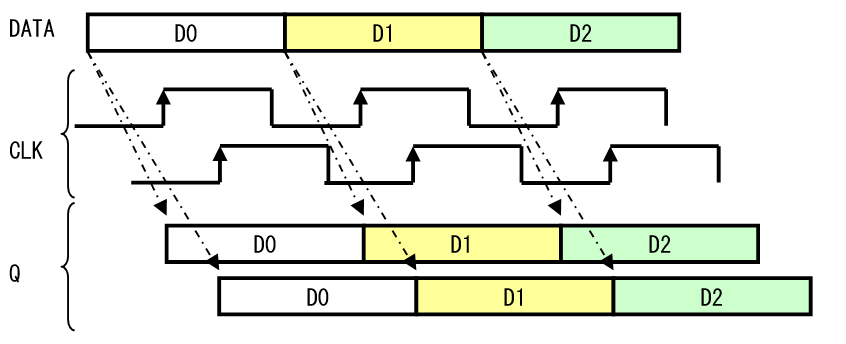

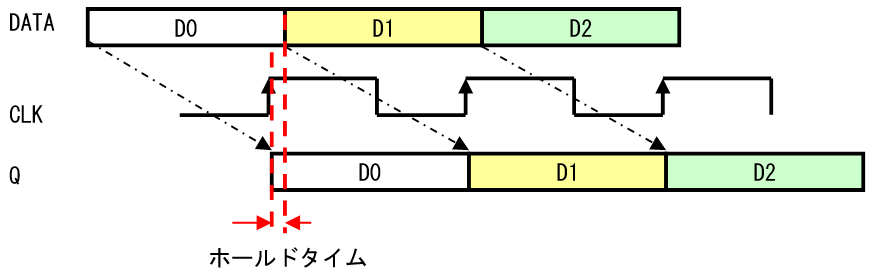

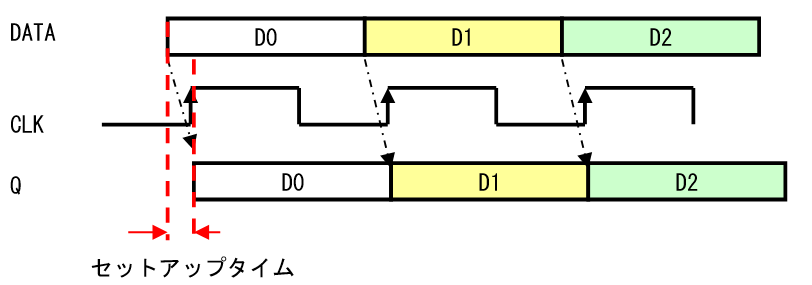

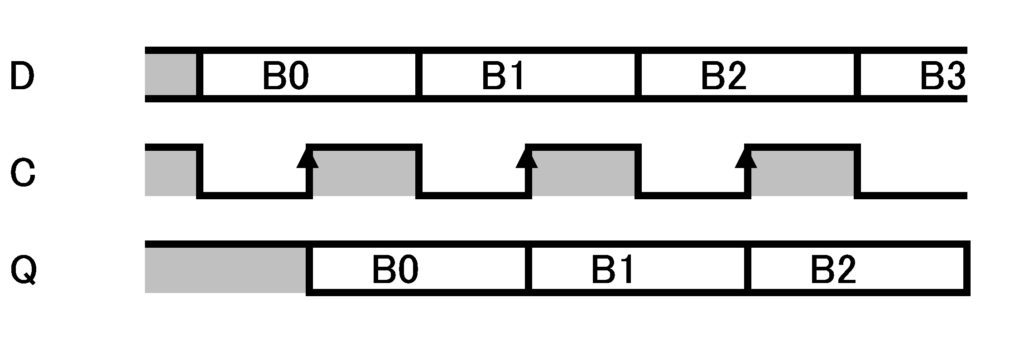

前回、DFFにはセットアップ・ホールドタイムがあり、このタイミングでデータとクロックを入力すると、正しく出力されず、メタステーブルという現象が発生することを紹介しました。

【前回の記事】

今回は、セットアップ・ホールドタイムの特徴とメタステーブル対策を紹介したいと思います。

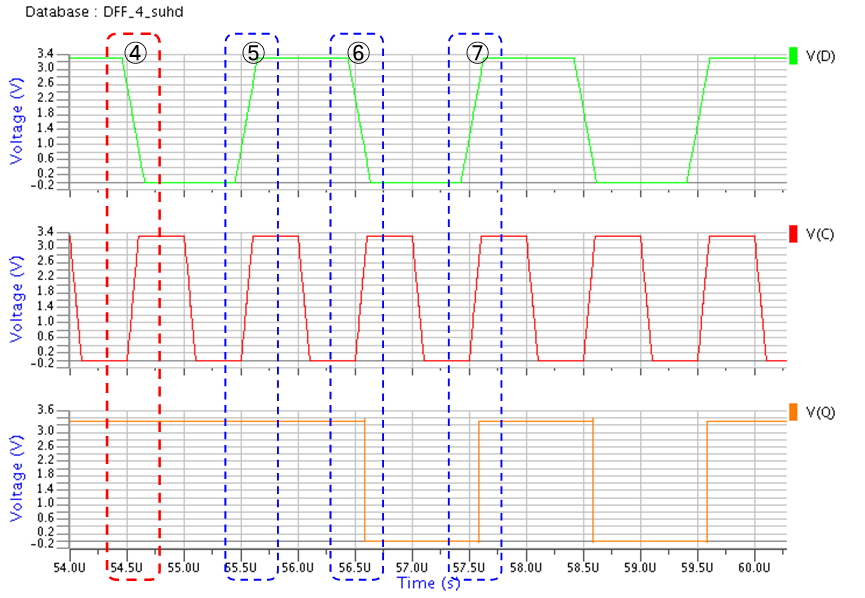

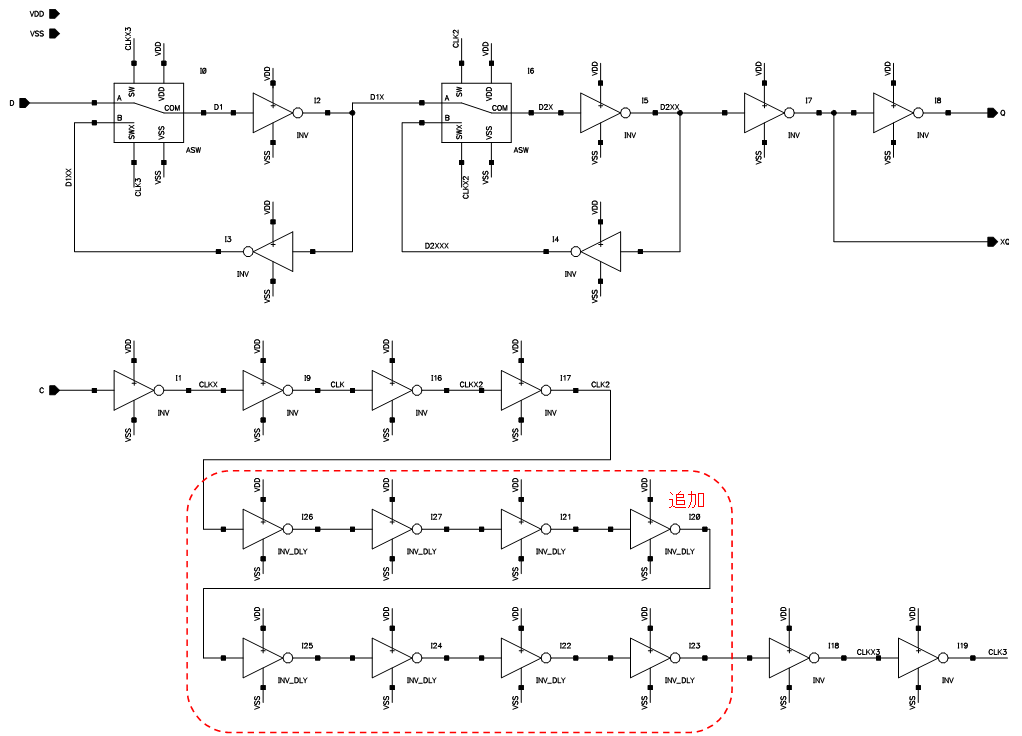

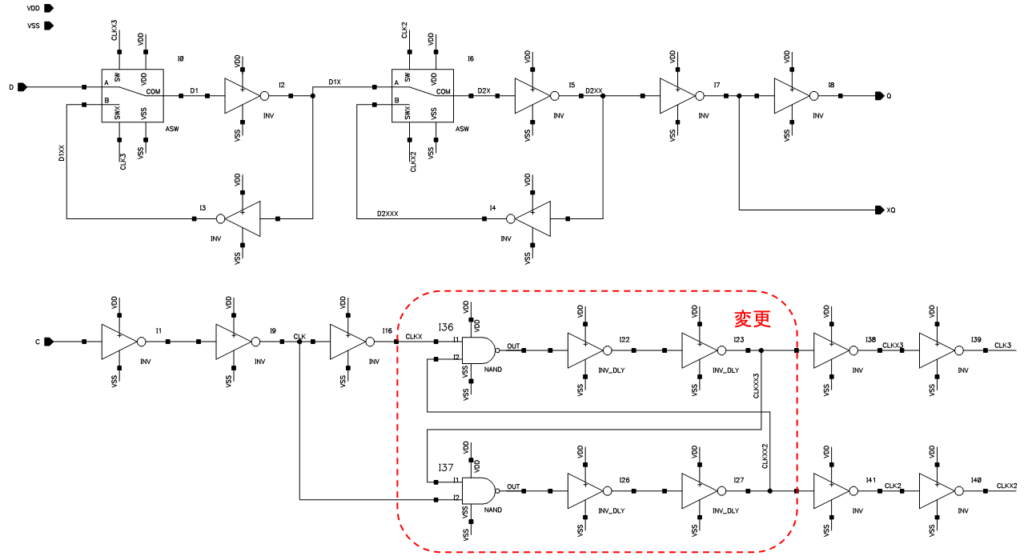

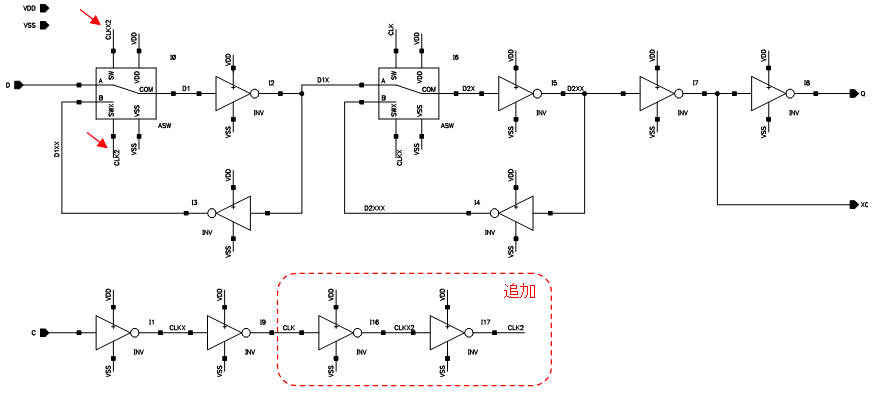

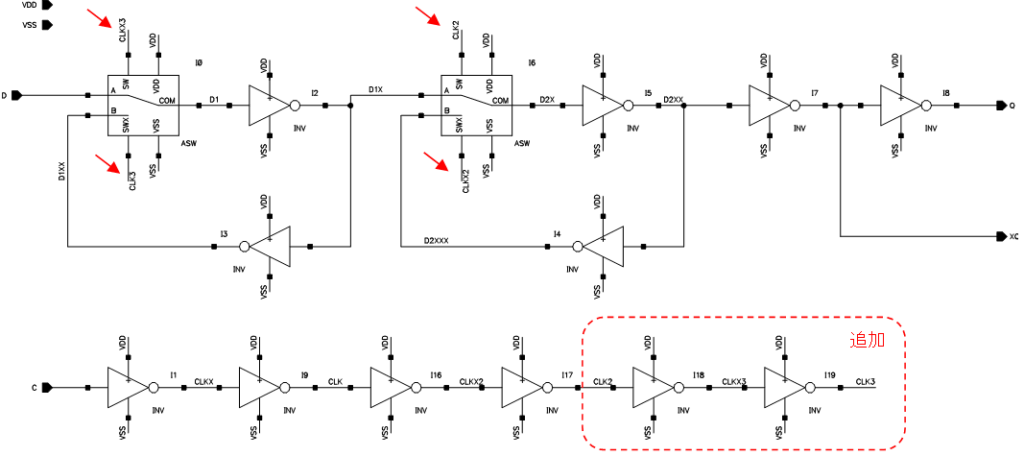

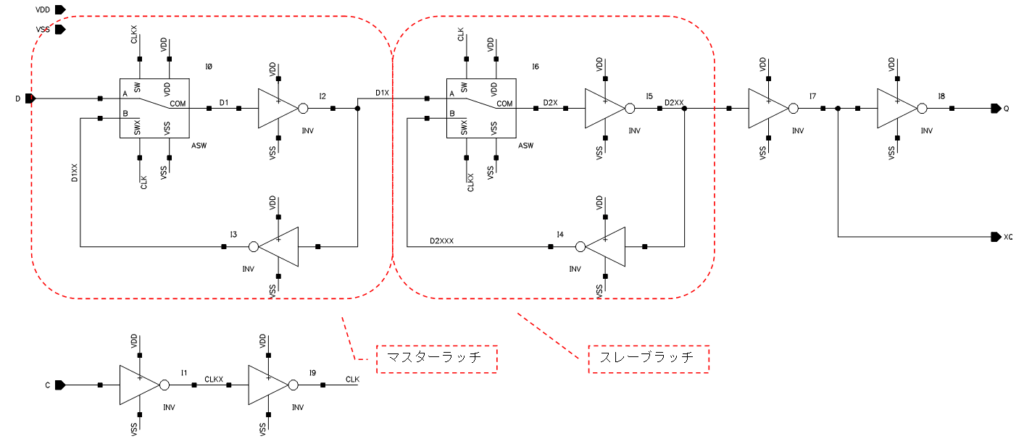

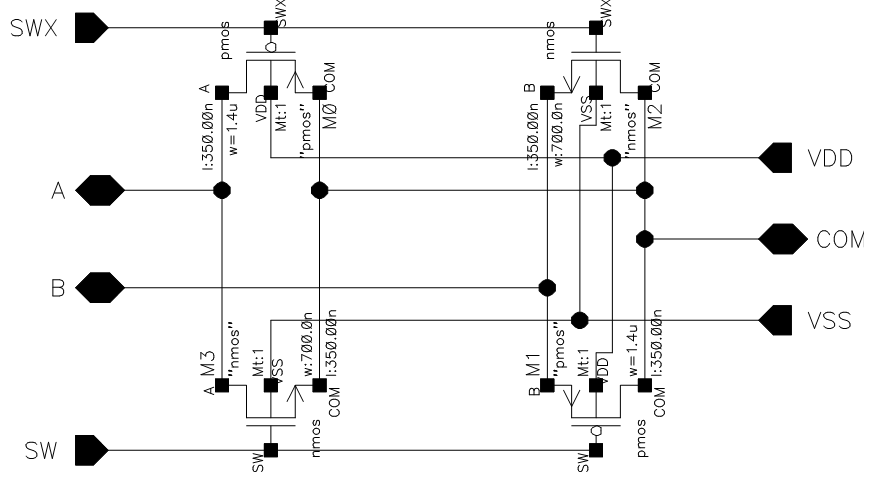

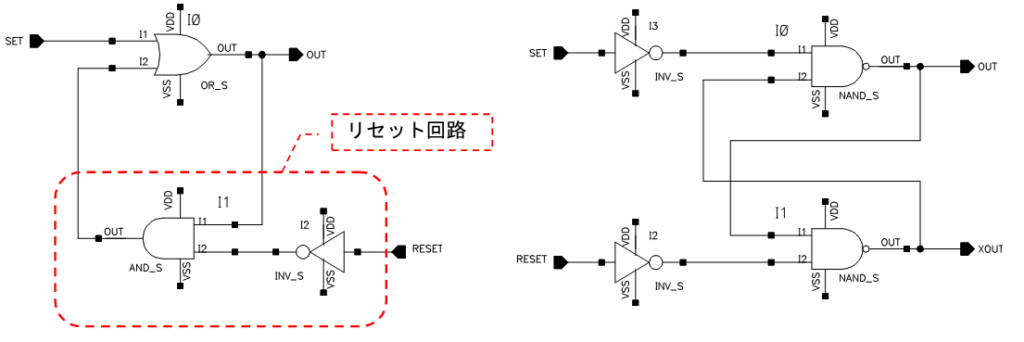

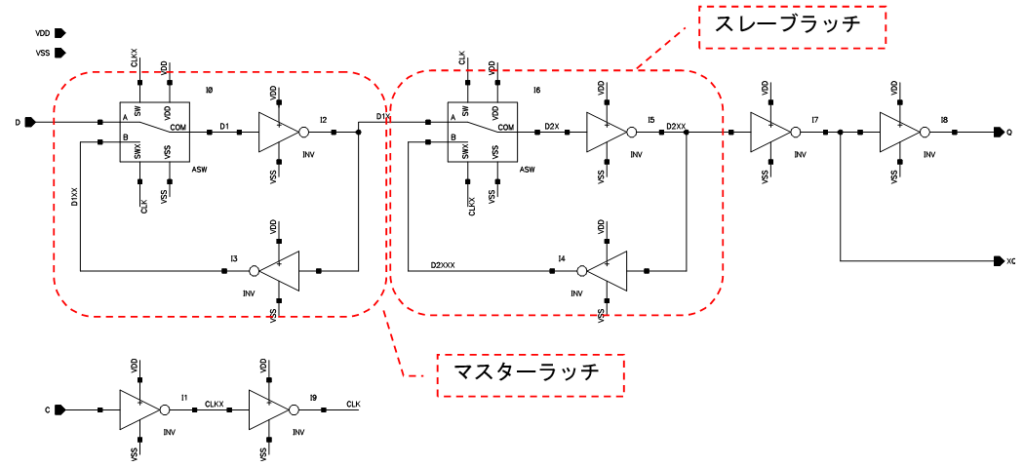

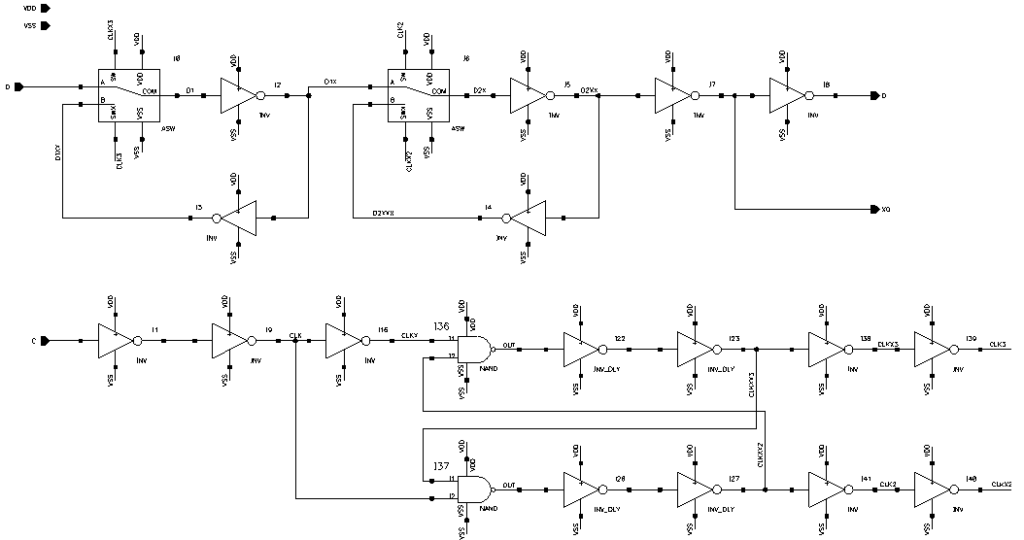

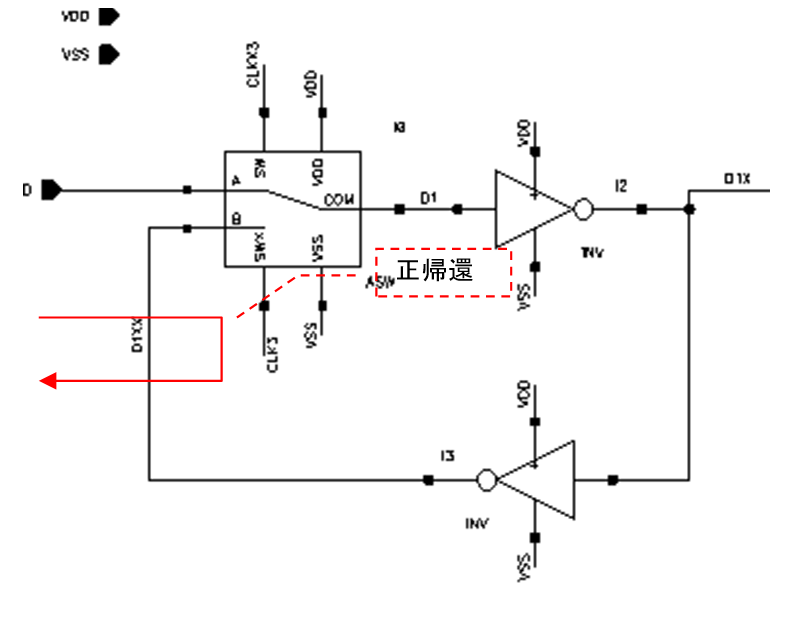

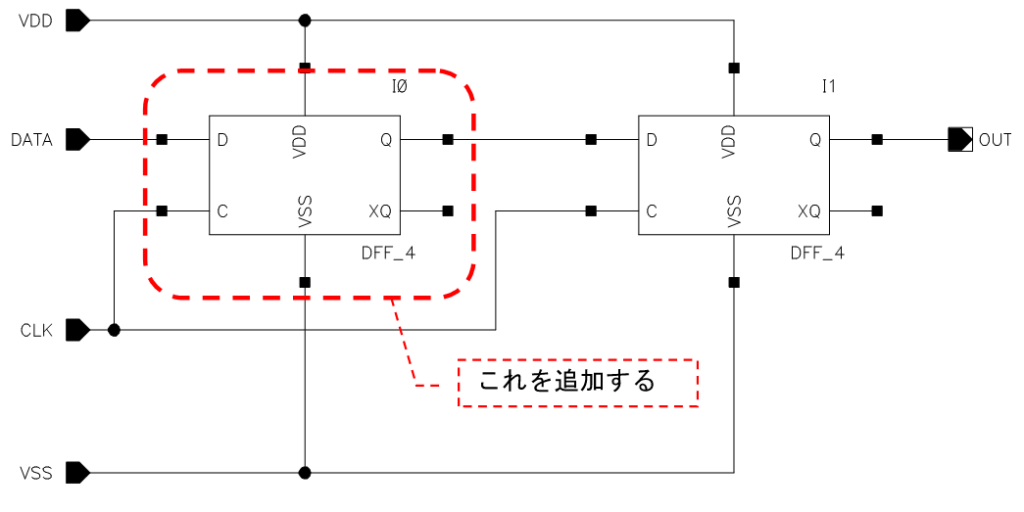

シミュレーションに使ったDFFの回路は、DFF(その4)で使った下記の回路です。

セットアップ・ホールドタイムへの影響

DFFの入力信号の条件として以下の4種類が考えられます。

- CLKの振幅

- CLKのTR/TF

- DATAの振幅

- DATAのTR/TF

これらのセットアップ・ホールドタイムに対する影響を見てみると次のようになります。

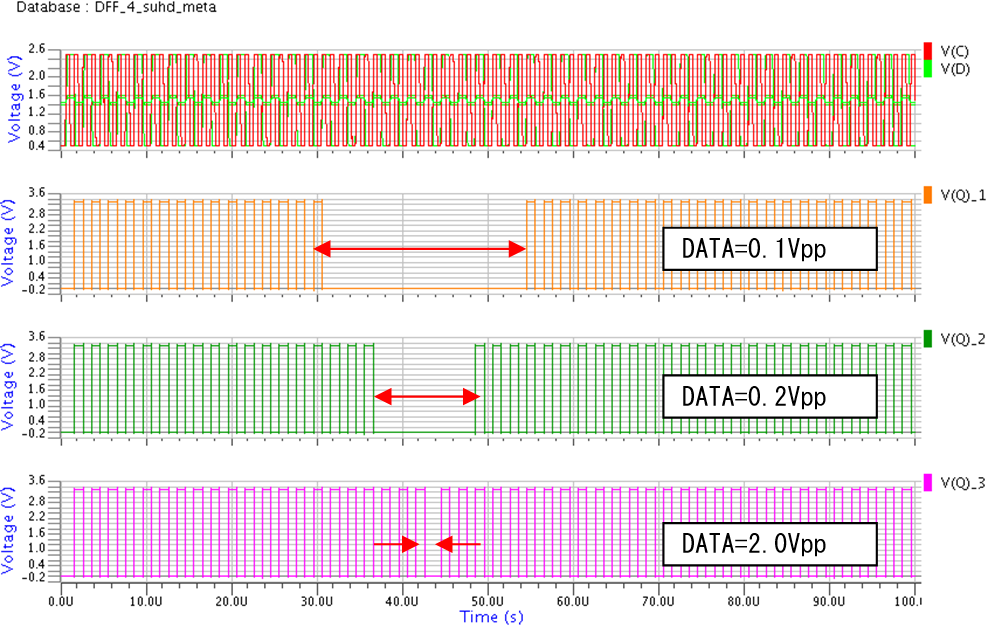

DATA入力振幅を変えた場合

CLK入力振幅を変えた場合

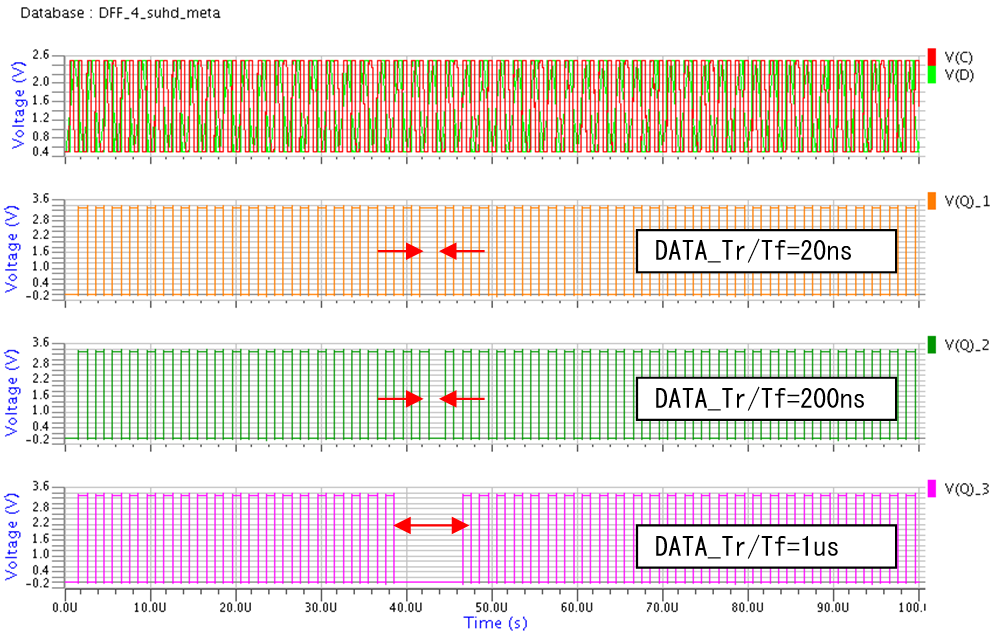

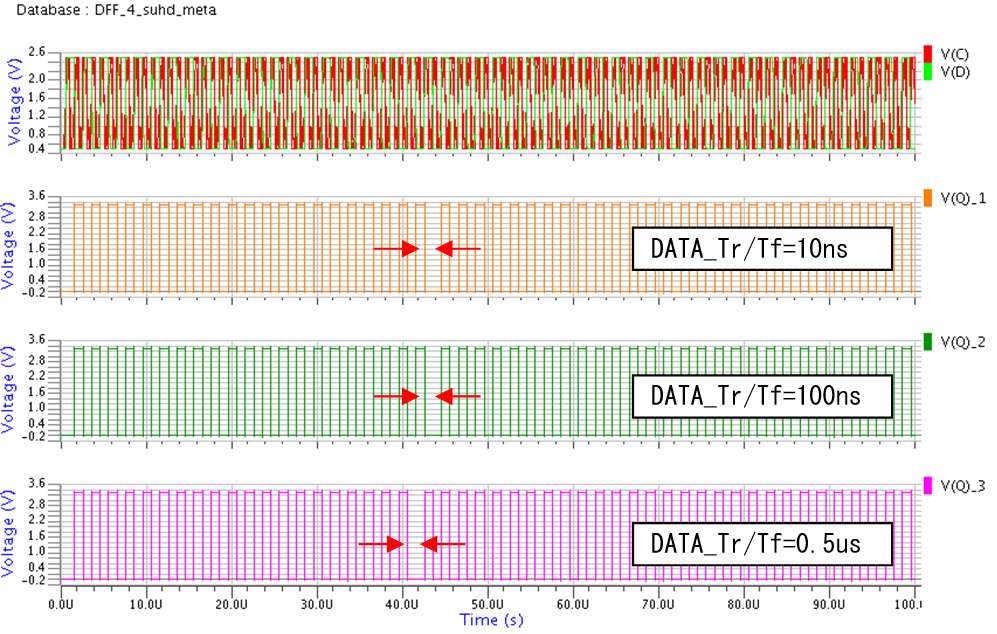

DATA入力波形のTR/TFを変えた場合

CLK入力波形のTR/TFを変えた場合

結果

以上の結果から、

- DATA入力振幅が小さくなると、セットアップ・ホールド時間が長くなる

- CLK入力振幅と波形のTr/Tf時間はセットアップ・ホールド時間への影響は少ない

- DATA入力波形のTr/Tf時間が長くなると、セットアップ・ホールド時間が長くなる

事が分かります。要するに、いかに“DATAをきれいにしてDFFに入力する”かが大事と言えます。

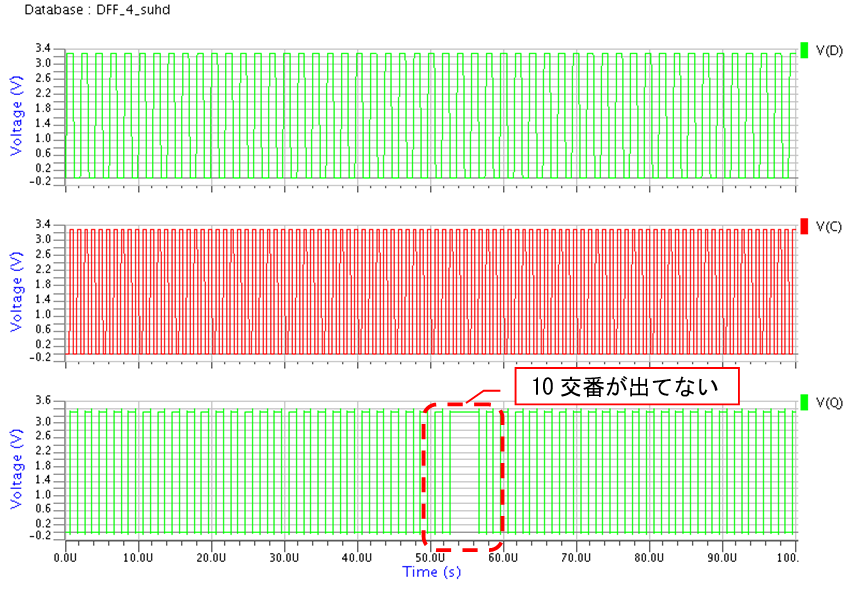

シミュレーションでは発生しにくいメタステーブル

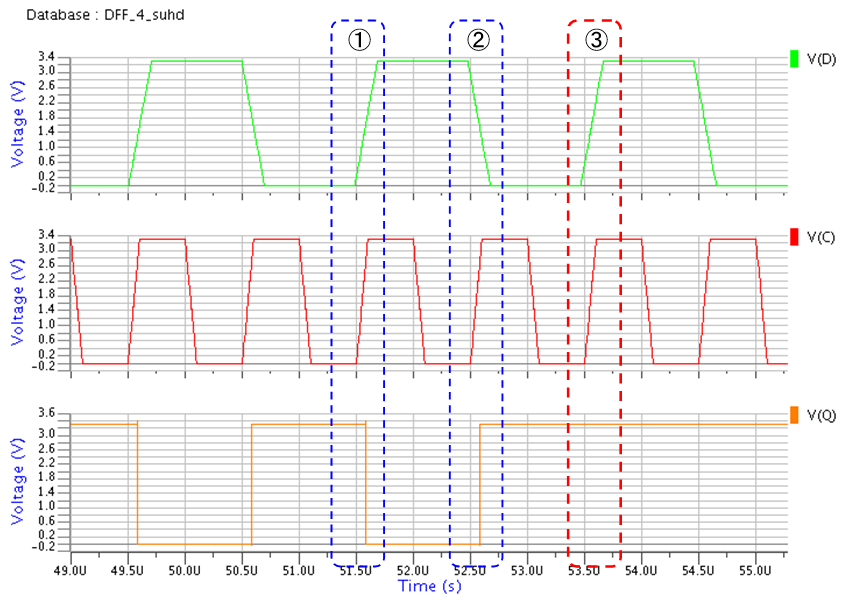

ちなみに、セットアップ時間を調べたのは、メタステーブルをシミュレーション発生させるためでした。ところが、実際はメタステーブルはなかなか発生しません。

メタステーブルの発生メカニズム

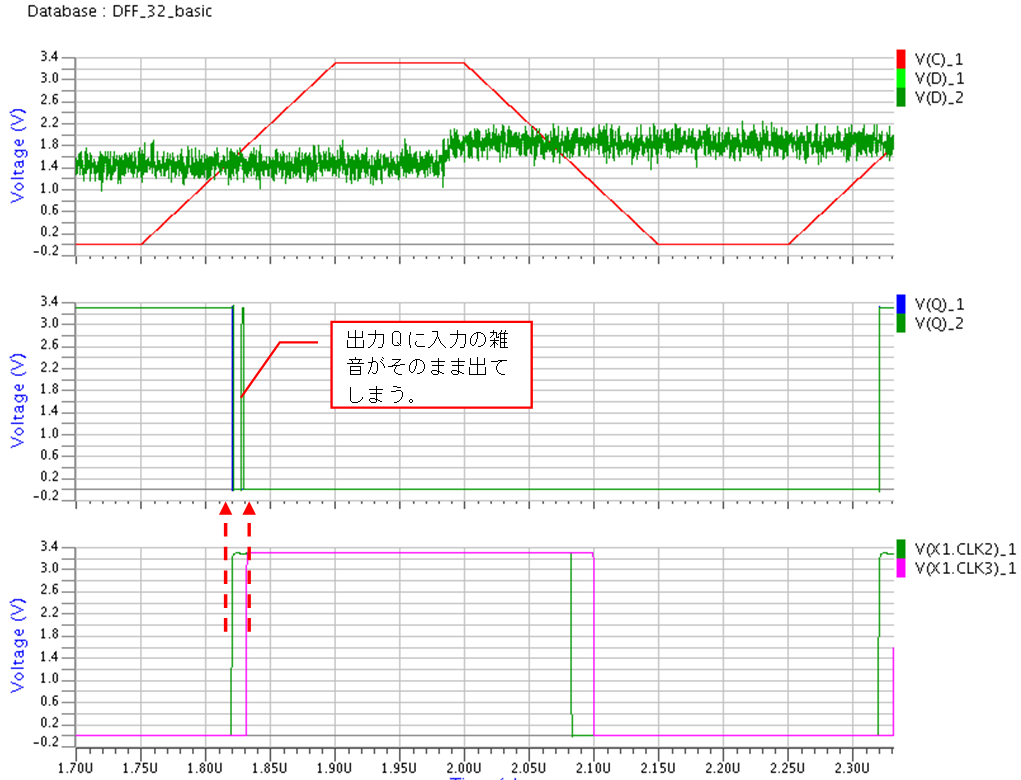

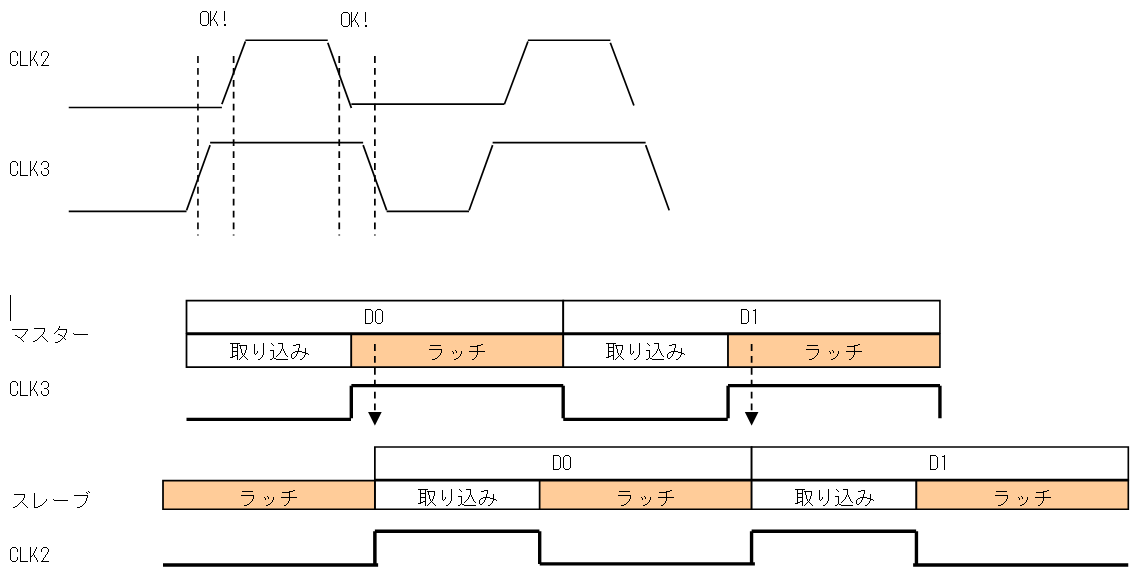

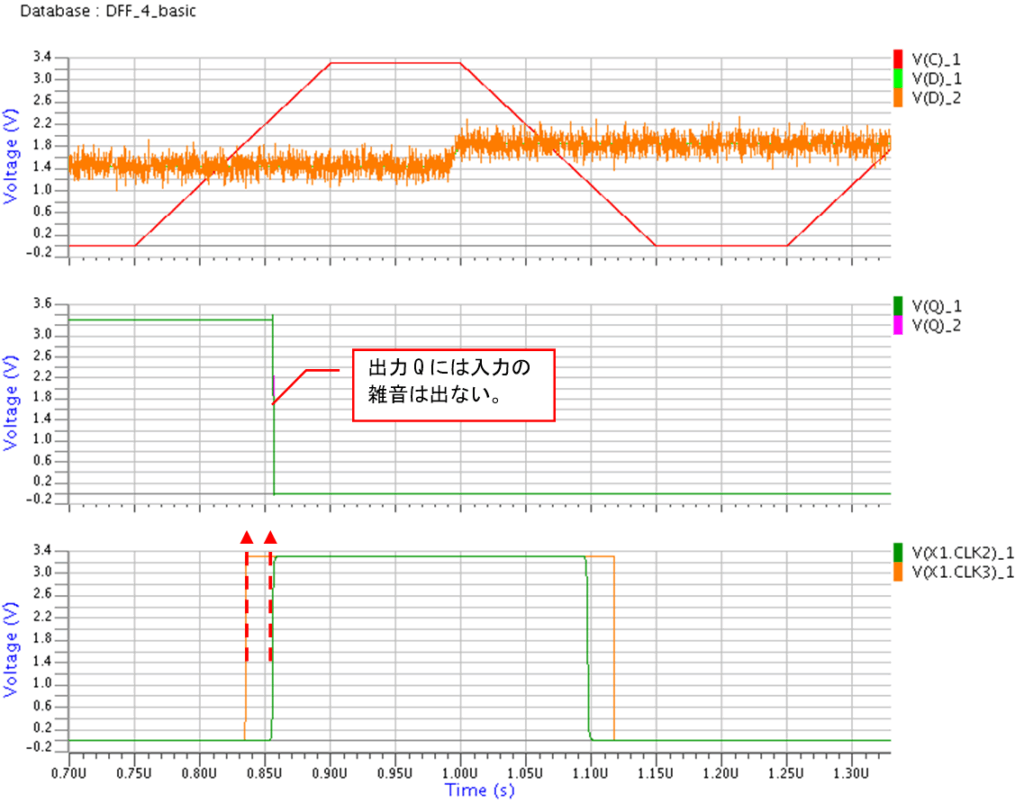

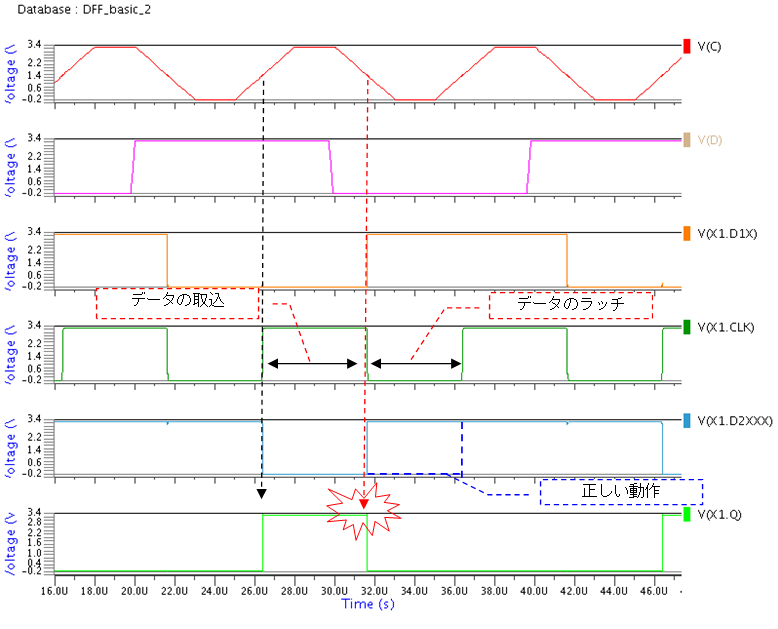

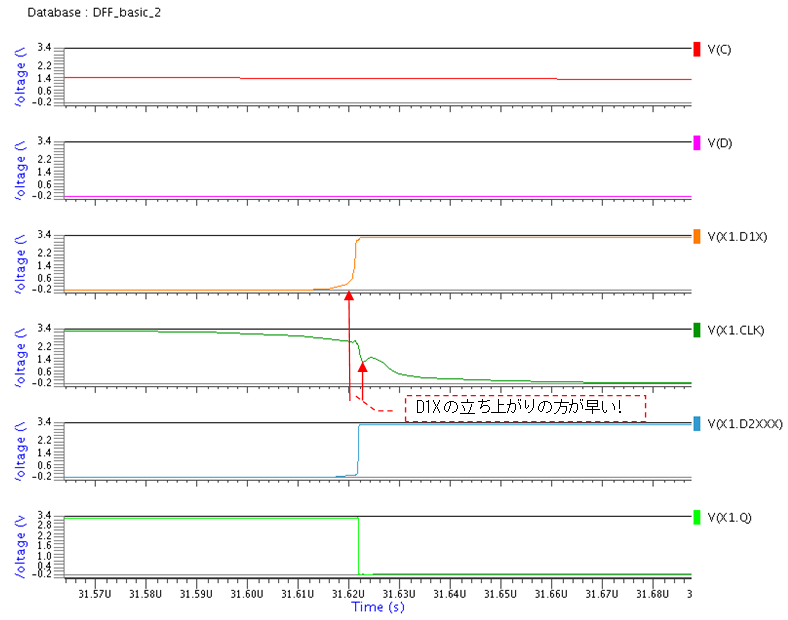

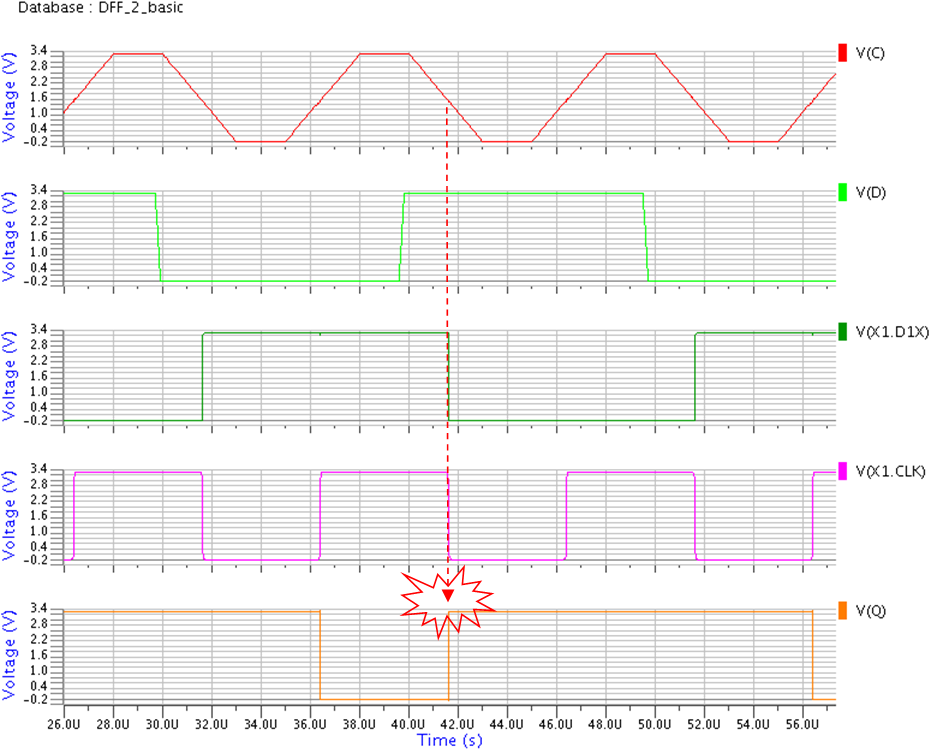

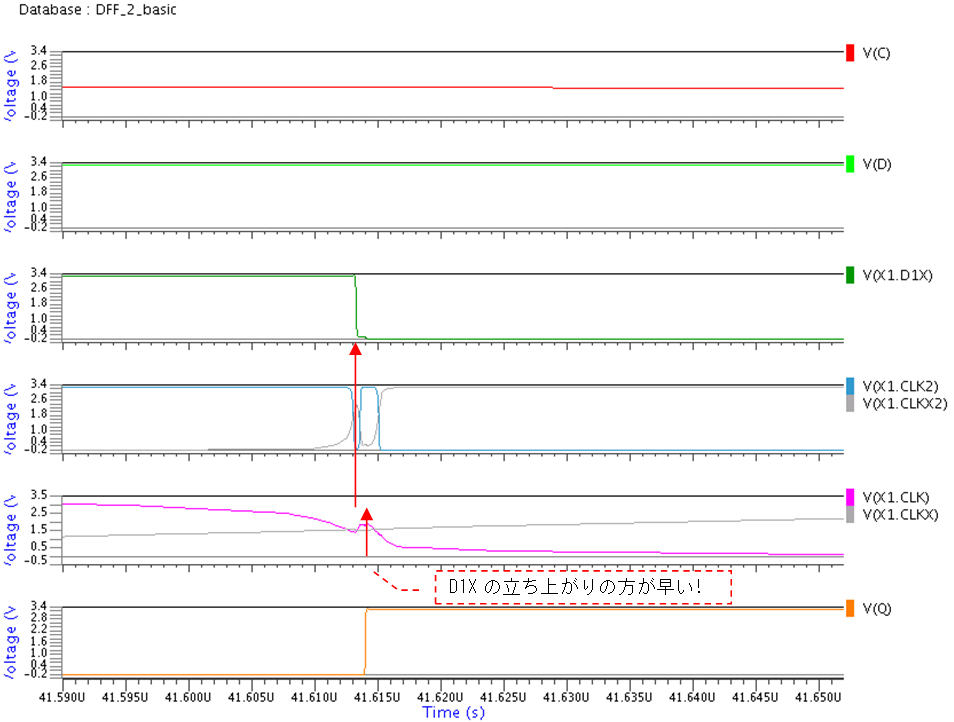

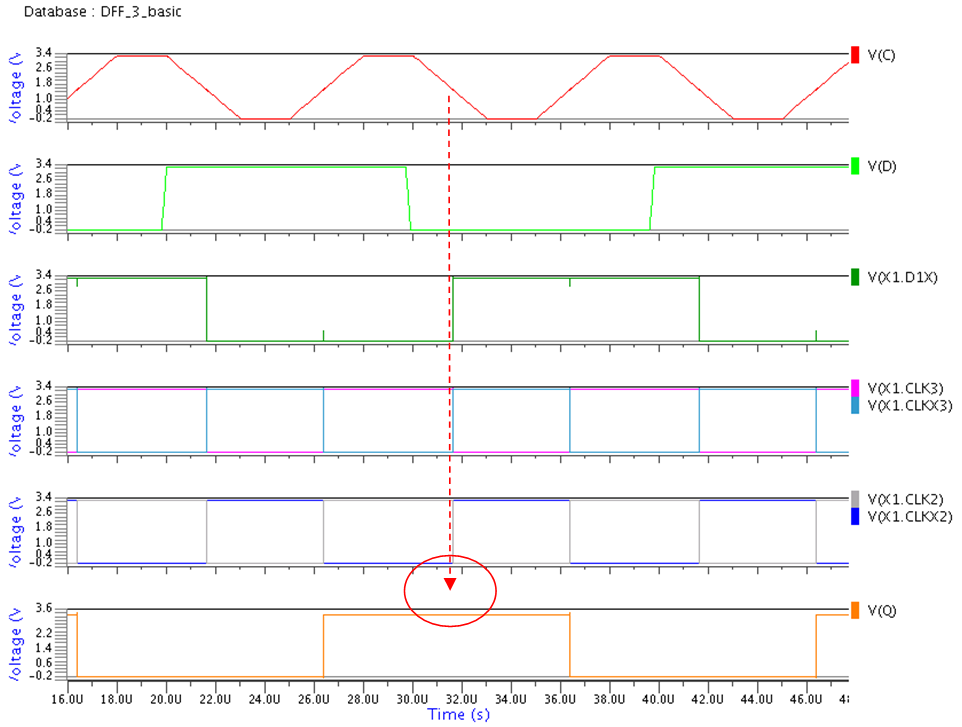

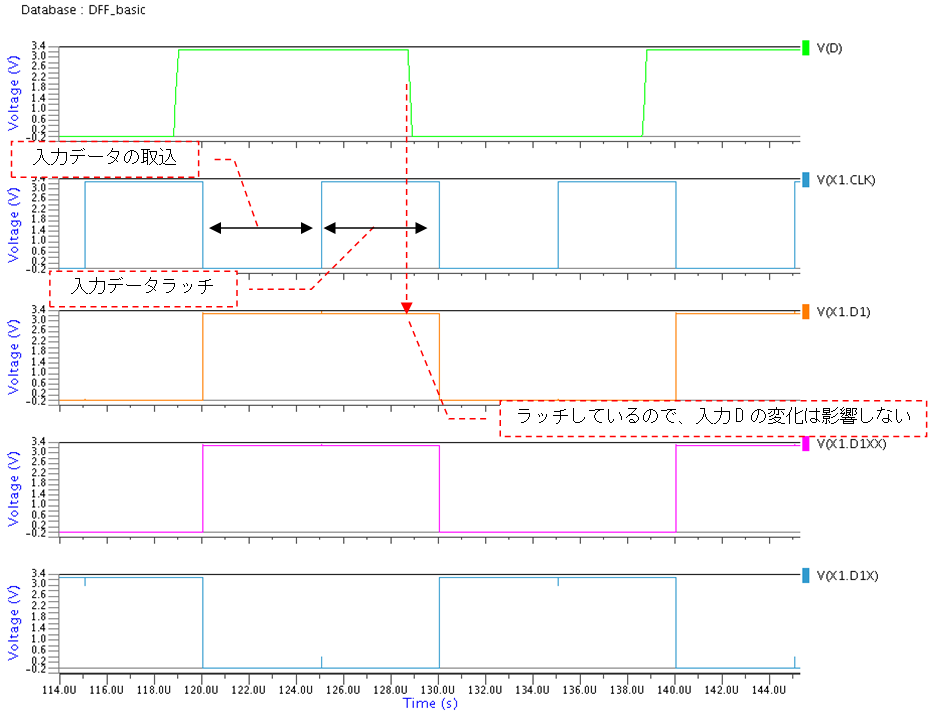

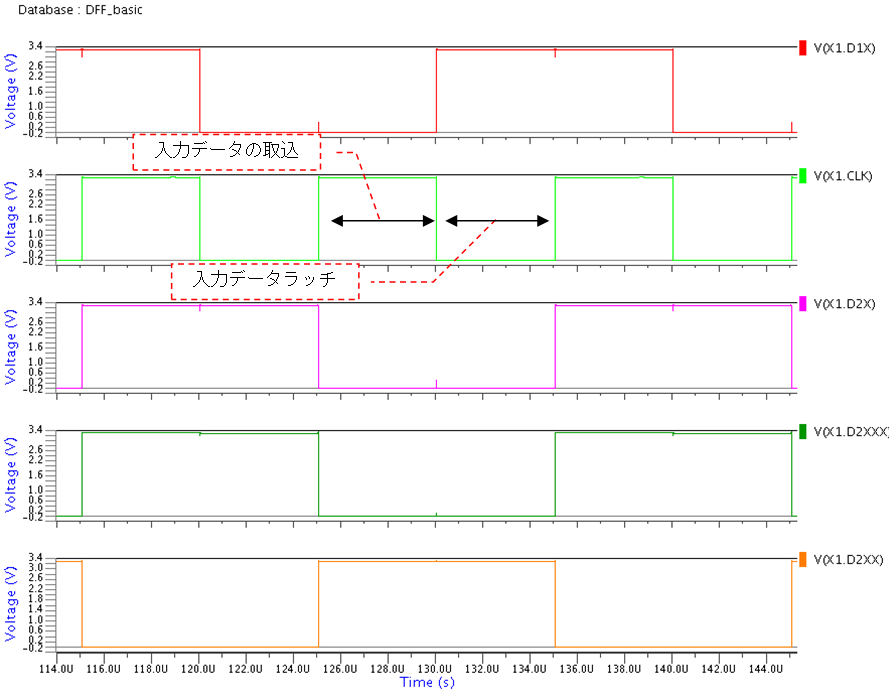

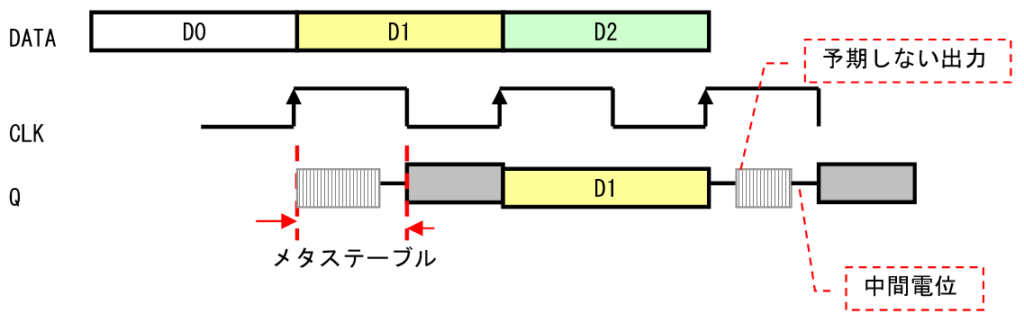

メタステーブルは、マスターラッチがラッチ出来ず中間電位でウロウロする。また、入力データとは無関係なデータを出力したりする。こうしたことで発生します。(図 7参照)しかし、普通のDFFではなかなか再現できません。

普通のラッチは上図のように正帰還ループを使うため、簡単に中途半端な電圧にとめる事ができません。例えば、インバータI2の入力電圧D1と帰還出力D1XXがピッタリ同じ中間電圧にあったとしても、CLK3が‘H’になってSWが切り替った影響で’H’か‘L’のどちらかに飛んでしまいます。つまり、メタステーブルはめったに発生しない現象なのです。

また、メタステーブルに入って中間電位が出ていたとしても、それは非常に不安定な状態なので何らかの外乱(CLKの立下りなど)で中間電位から脱し、次のCLKでは正常に戻ることがほとんどです。

メタステーブルが問題視される理由と非同期信号への対応策

それでもメタステーブルが問題とされているのは、次の理由からです。

- 予期しない出力が出るので、後段のデジタル回路が誤動作する。

- 中間電位が出力されると、後段のデジタル回路にも貫通電流が流れる。

- シミュレーションで再現できないので、設計で気がつかないことがある。

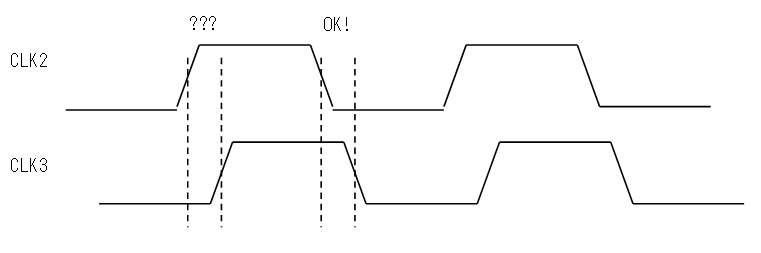

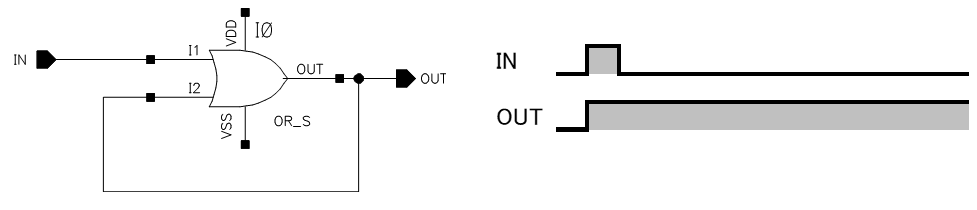

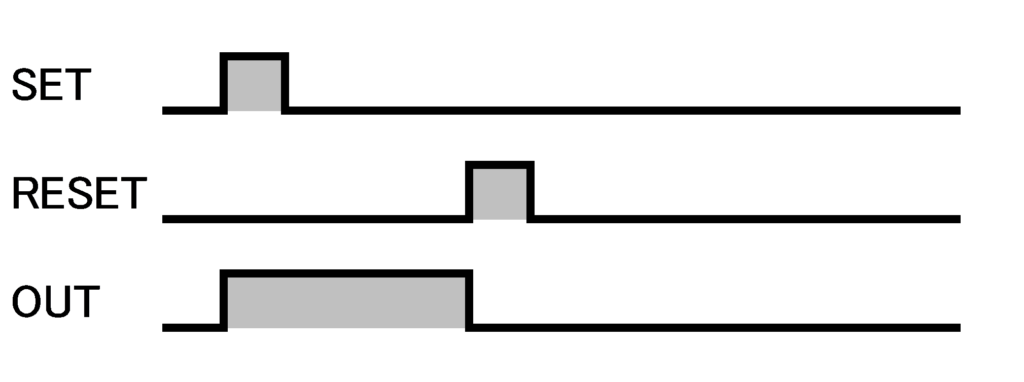

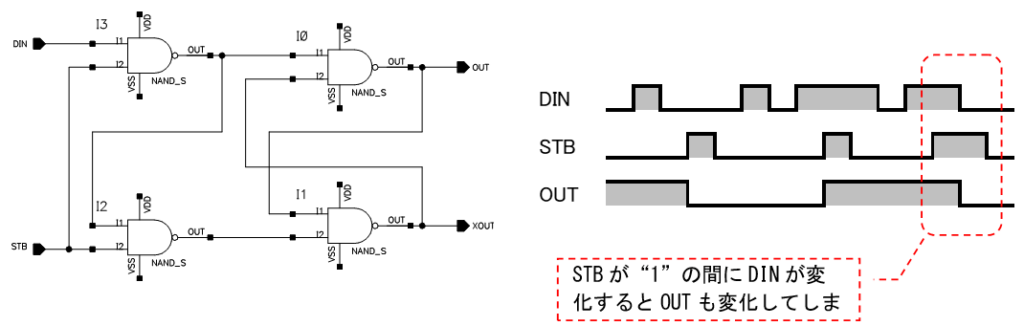

メタステーブルを防止するには、セットアップ・ホールド時間をきちんと確保した同期設計をする事が一番確実なのです。しかし、リセット回路など非同期の信号を扱う場合は、セットアップ・ホールドなどと言えません。このような非同期の場合は、下記のように対策します。

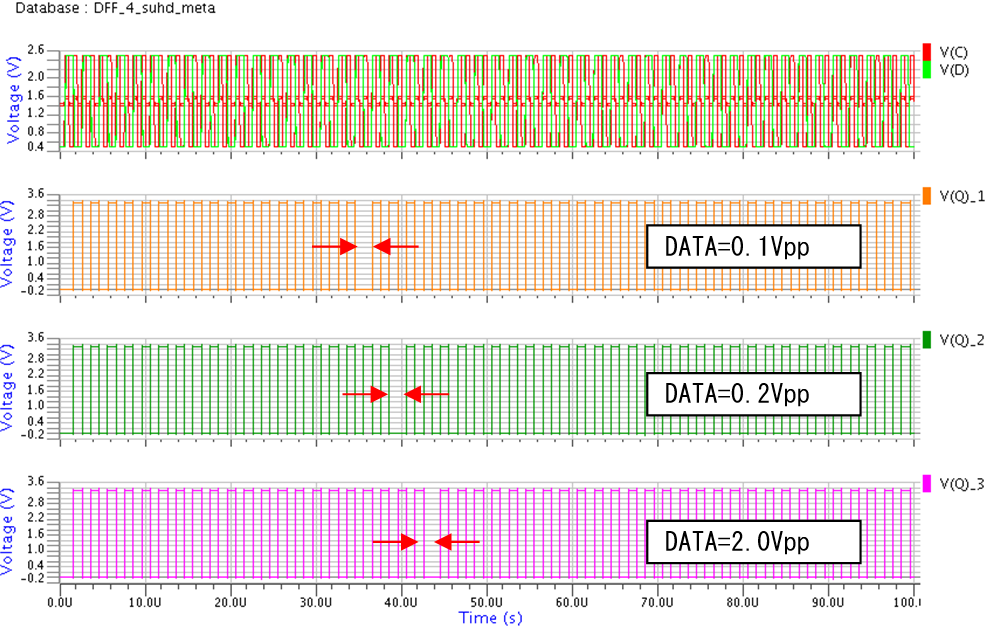

このように、DFFを一段追加する事で、メタステーブルの影響を後段に伝える事を防止しています。

さすがに2段連続してメタステーブルに入る事は無いだろうという事ですが、確率の問題で絶対無いとはいえません。そこで、回路規模や消費電流に余裕がある場合は更にDFFを追加してより確実にするのが一般的です。

次回は、時間軸と周波数軸を行ったり来たりする”フーリエ変換”について触れたいと思います。