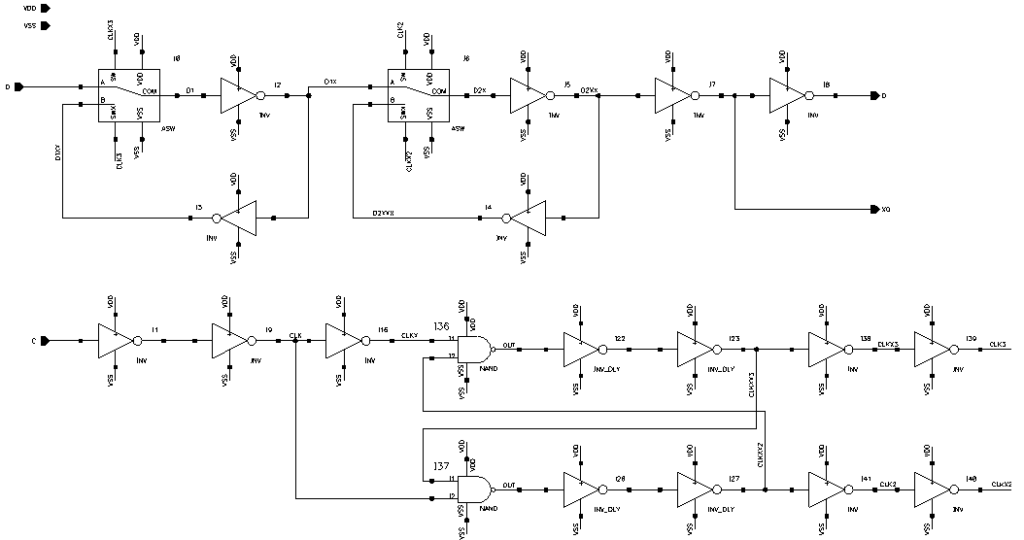

高速IF(高速伝送)設計のその②です。今回は前回の基本ステップに続く、伝送波形とその評価方法(アイパターン)について解説します。前回の記事はこちら

伝送波形とその評価方法

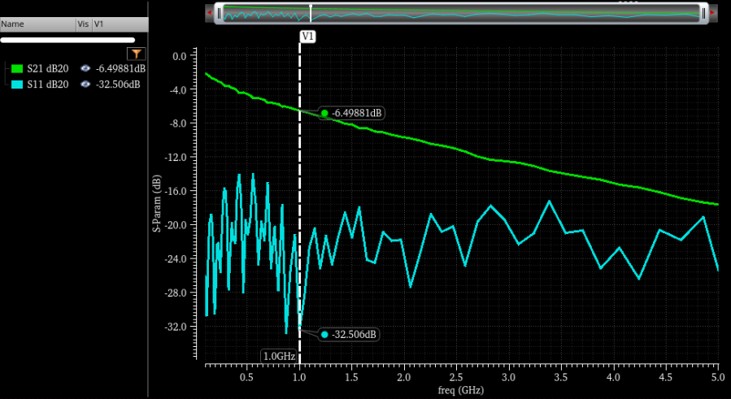

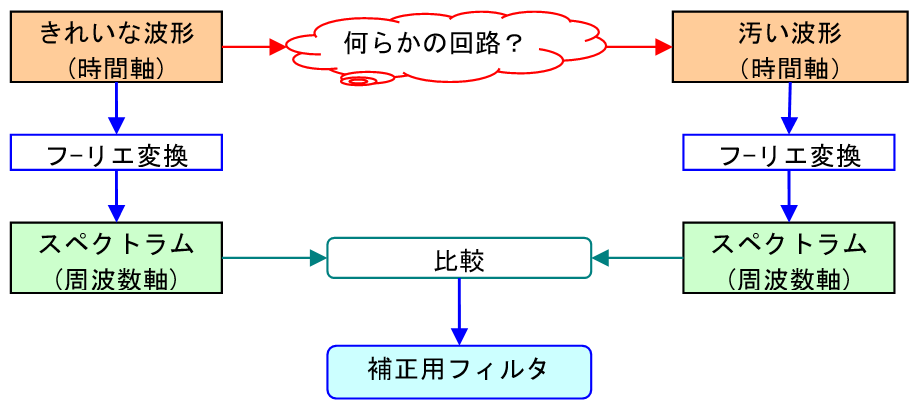

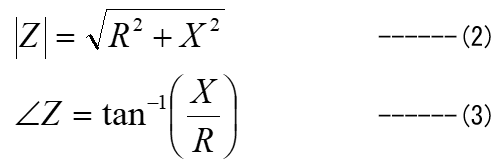

次ステップで重要なのが「周波数特性の評価」です。

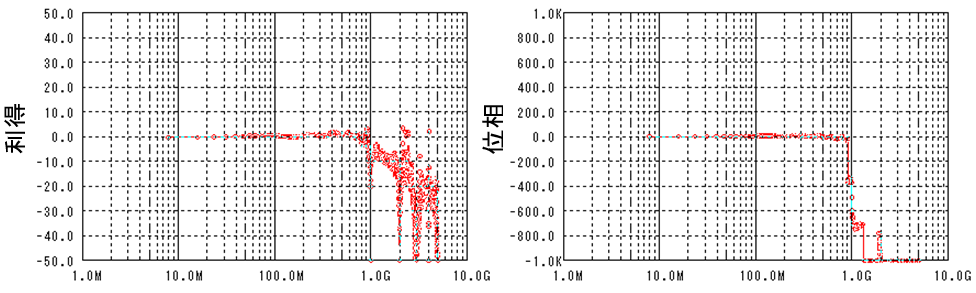

2Gbps NRZ信号なら、1GHz帯のS21特性が波形品質に直接効いてきますので、この見極めは重要です。

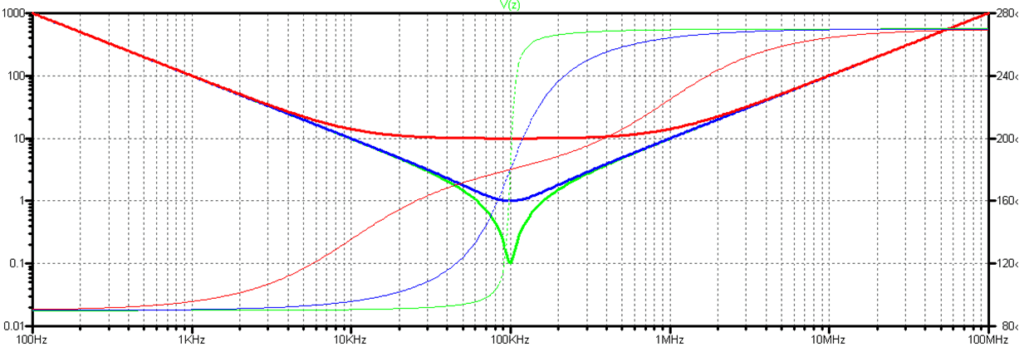

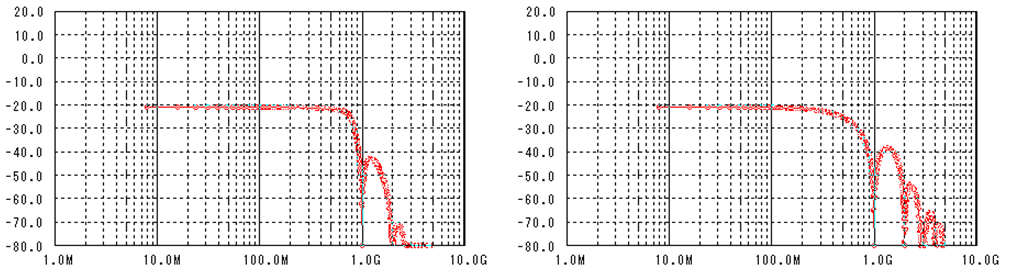

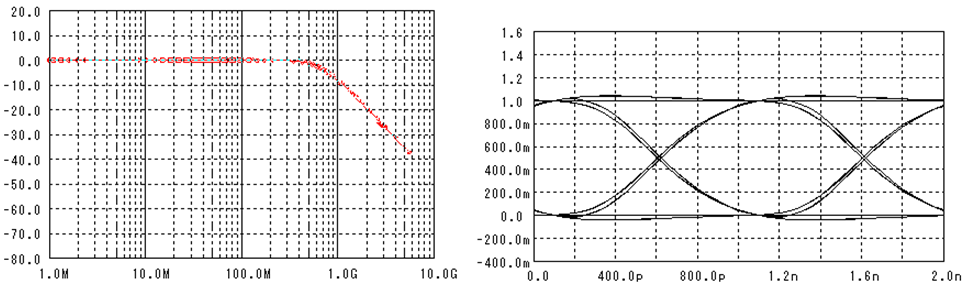

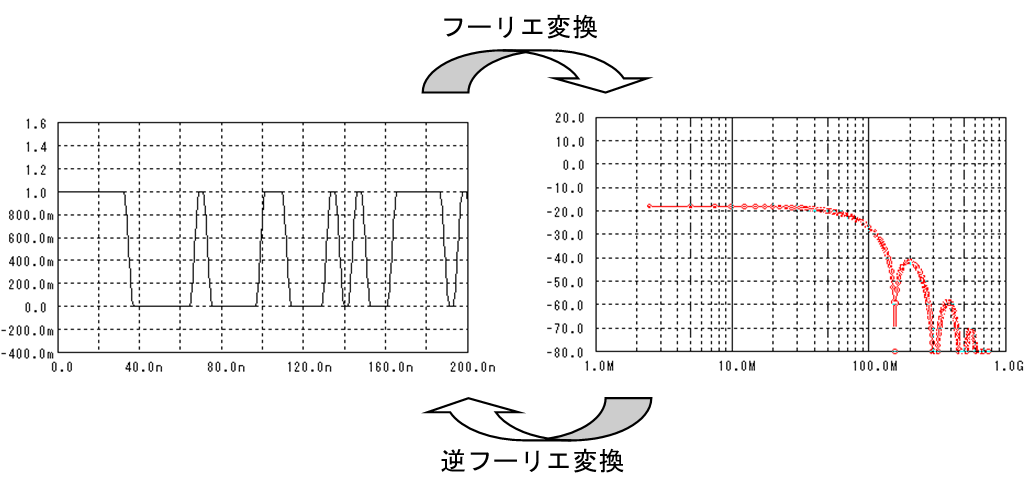

今回の設計では、図のようにS21: -6.5dB@1GHz S11: <-14dB (0-1GHz) となりました。S21の特性から考慮すると、2Gbps伝送のためには何らかの周波数特性補償が必要になると考えられますが、実際の波形にはどのような影響があるでしょうか? それを分かりやすく調べる方法があります。

アイパターン評価と波形品質

アイパターンとは?

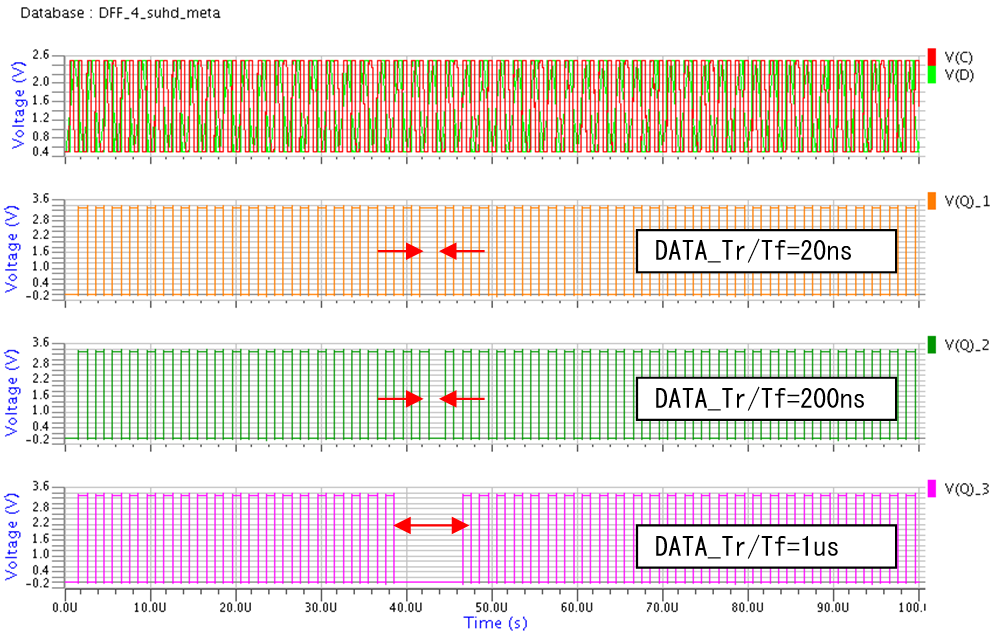

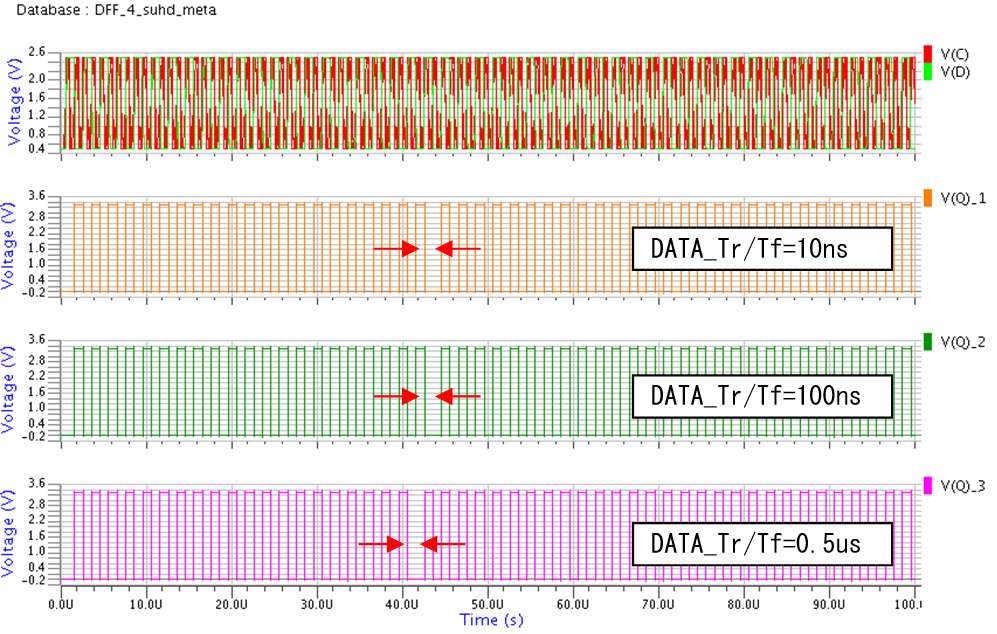

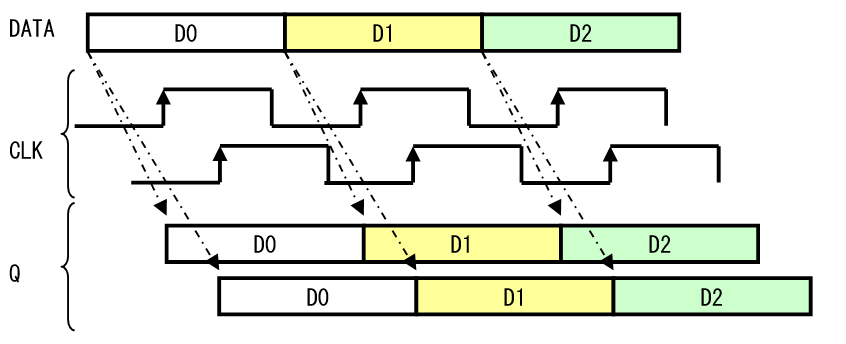

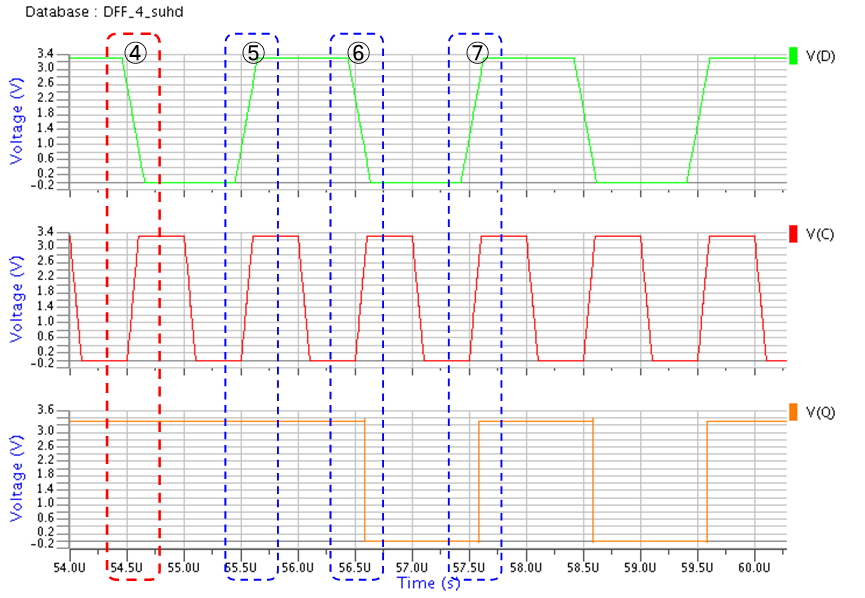

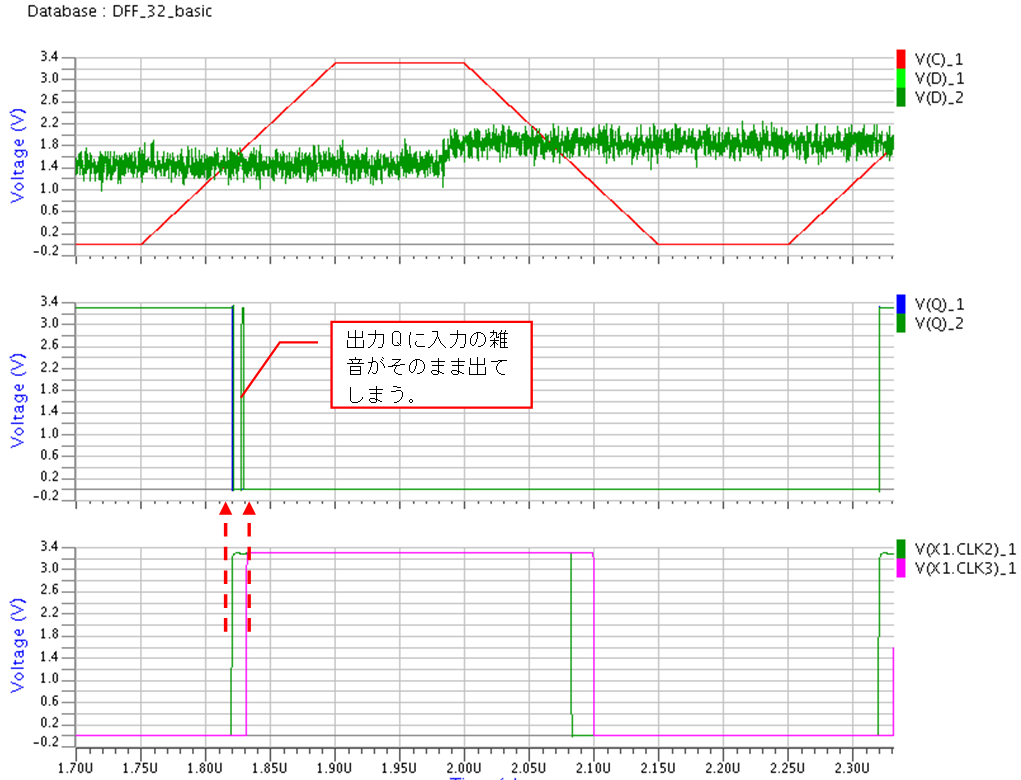

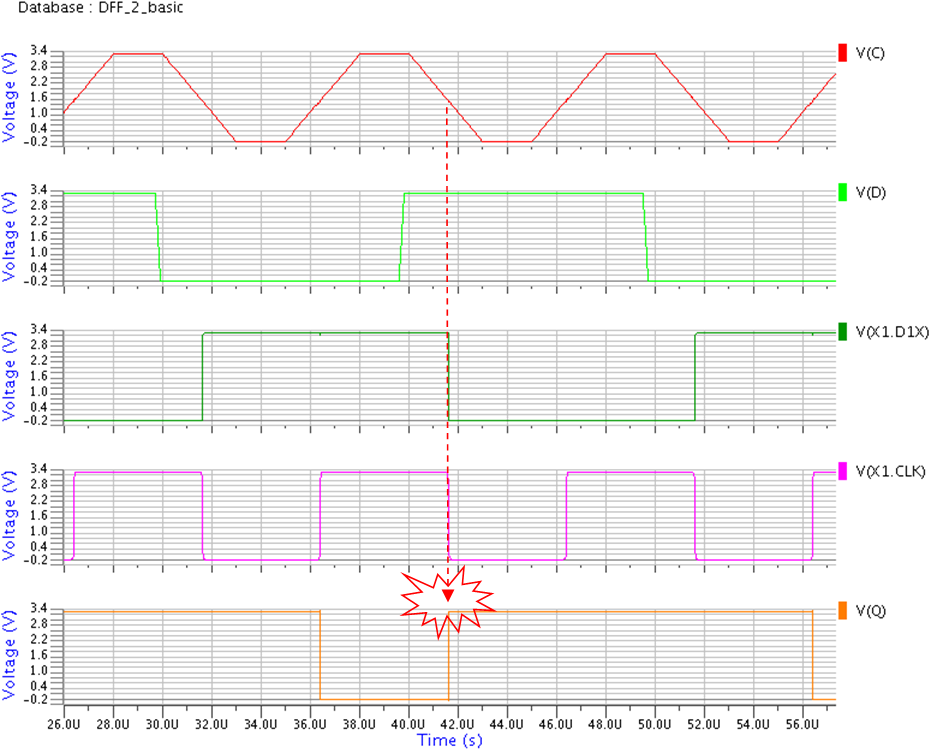

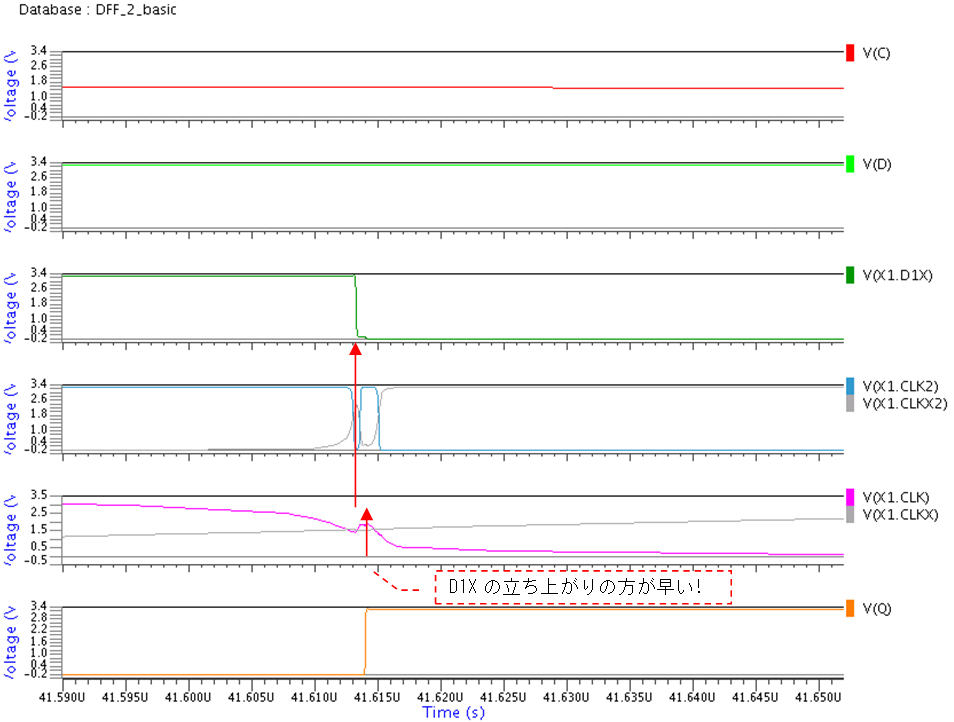

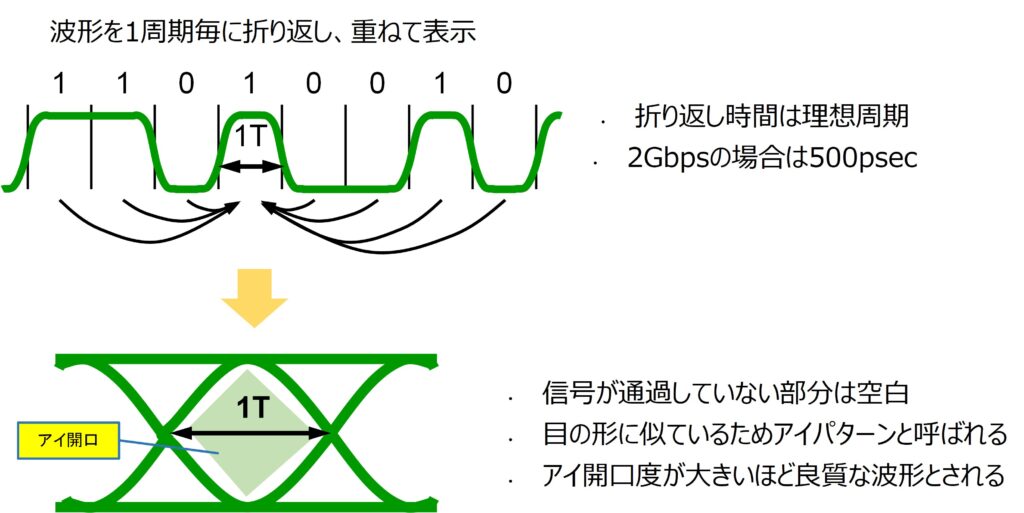

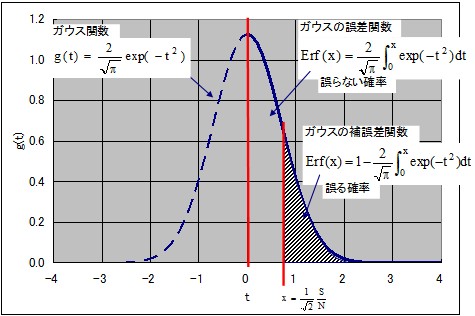

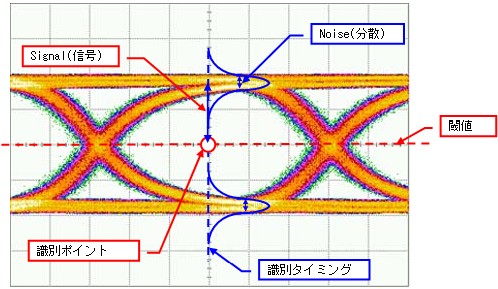

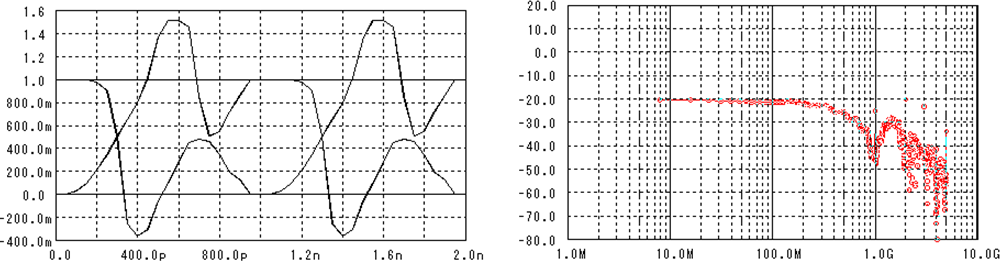

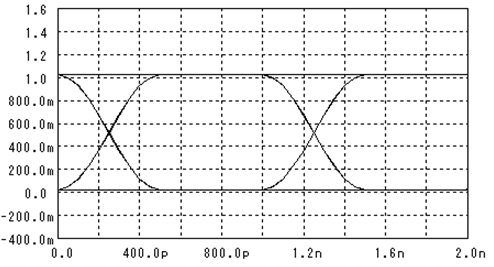

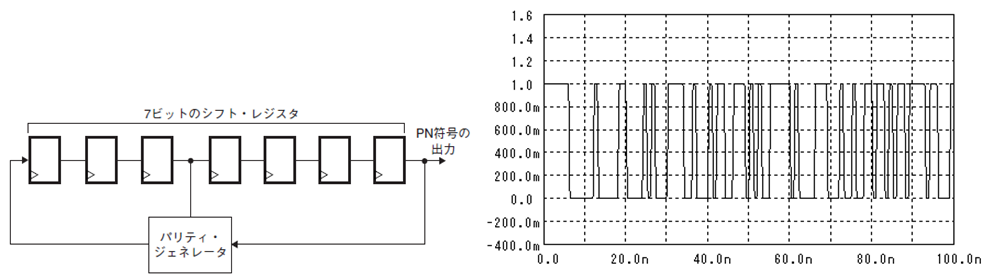

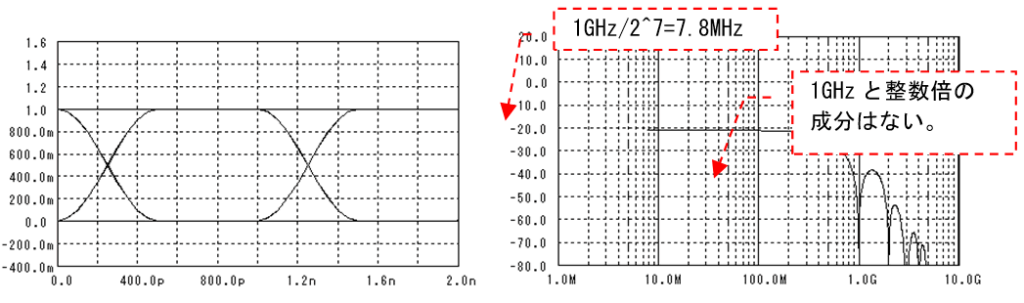

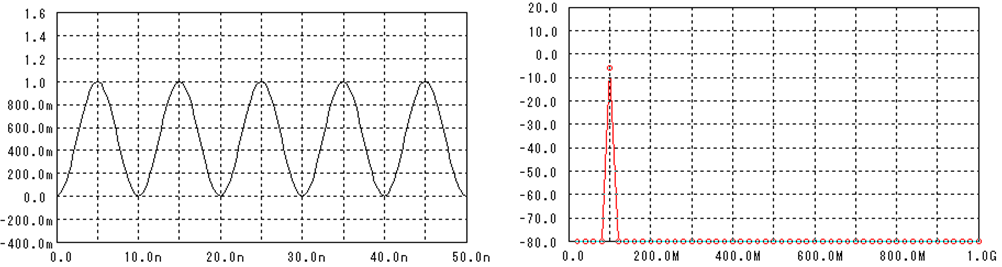

「アイパターン」とは、波形信号をビット周期ごとに折り返して重ねることで、伝送品質を一目で可視化できる評価手法です。これらの波形を重ねた表現がちょうど、目の形に似ているからアイパターンと呼ばれています。2Gbpsの時は、折り返し時間は理想周期で500psecですが、これをビット周期ごとに重ねてみます。すると下図のような絵になります。このときアイパターンの「目の開き」が広いほど信号品質が高く、閉じているとジッタやノイズ、遅延による問題が発生しやすい状態を表します。

アイパターンは、波形の様々な様子が一目でよくわかり、周波数特性補償の有無を考える上でとても便利な指標です。

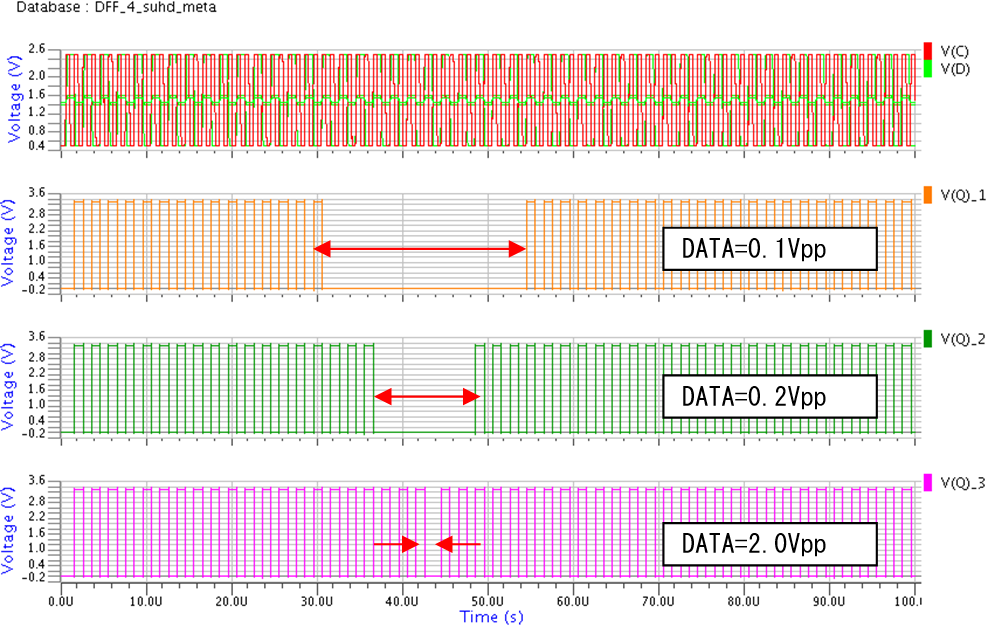

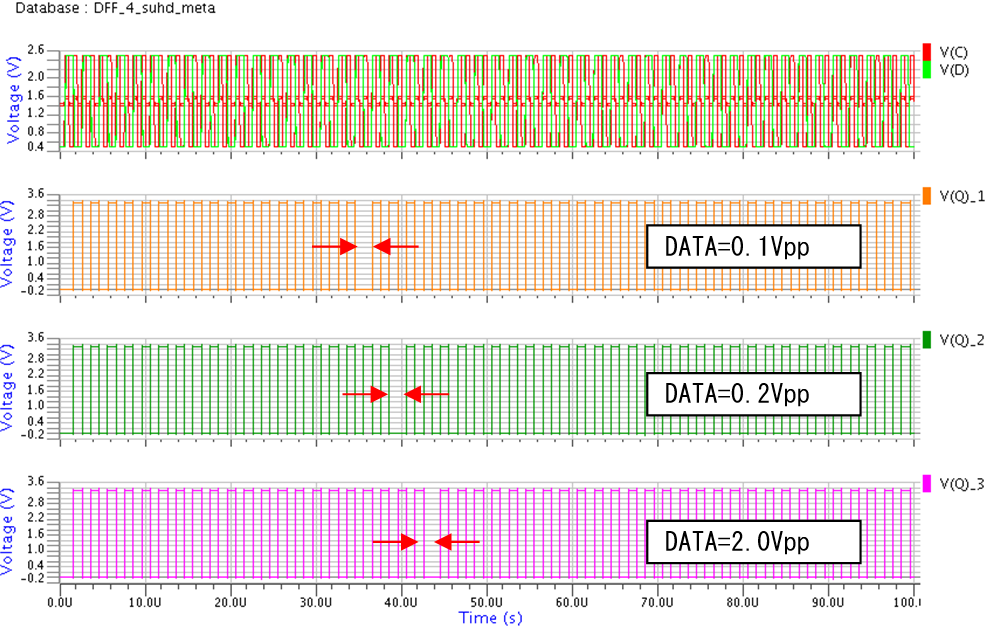

2Gbpsアイ開口 ― アイパターンで見る波形品質の実際

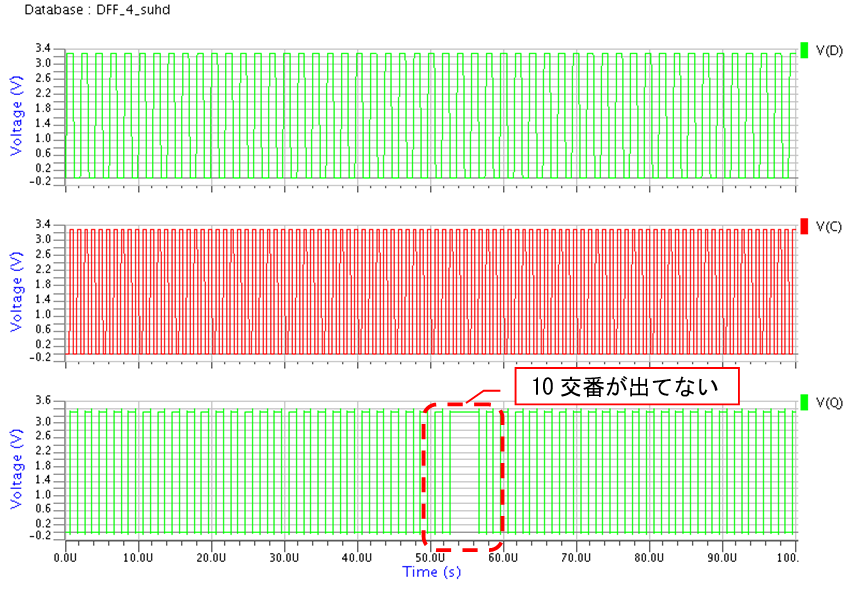

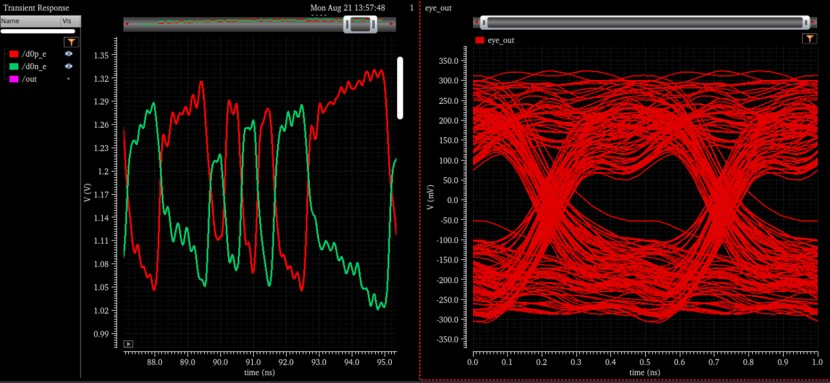

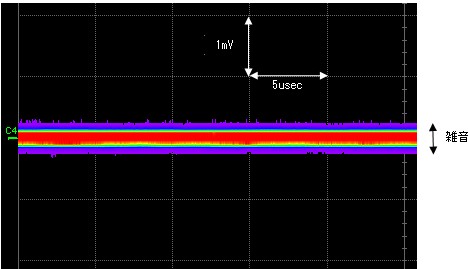

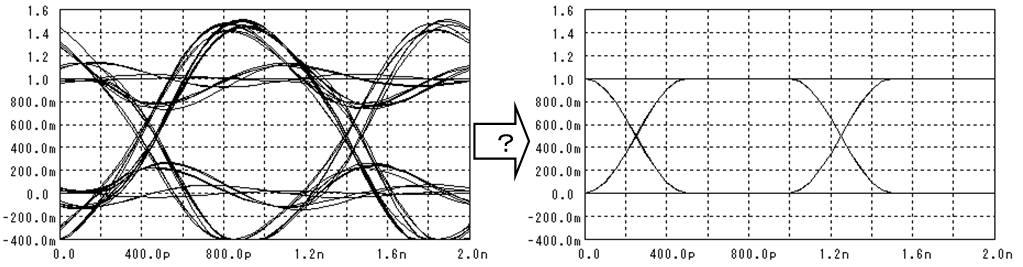

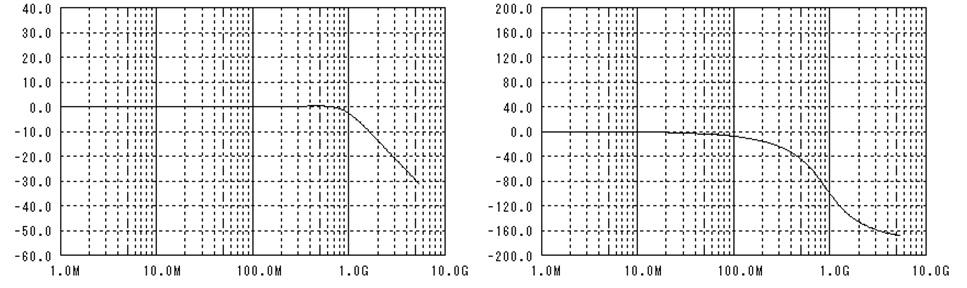

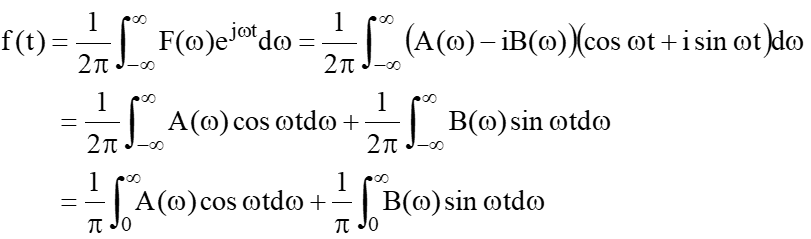

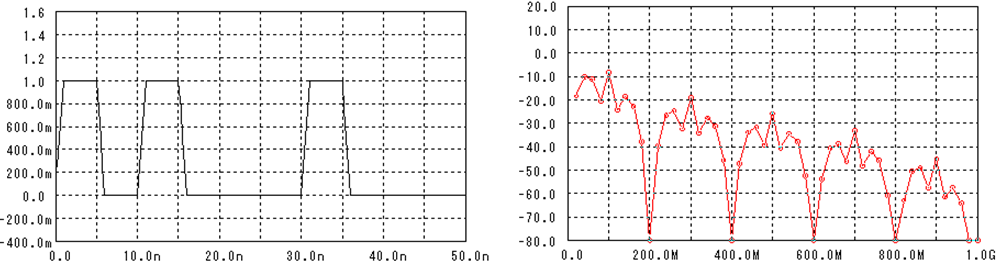

さて、実際の2Gbps伝送のRX(受信側)終端抵抗での波形を評価してみましょう。図の左側は、擬似ランダムパターン(PRBS7)を伝送したときの受信波形です。

この波形を見ると、特に高域成分(高速な立ち上がり・立ち下がり)のデータ振幅が縮小していることが分かります。これは伝送路による周波数特性の影響、すなわち高周波成分の損失が大きく効いてきている証拠です。

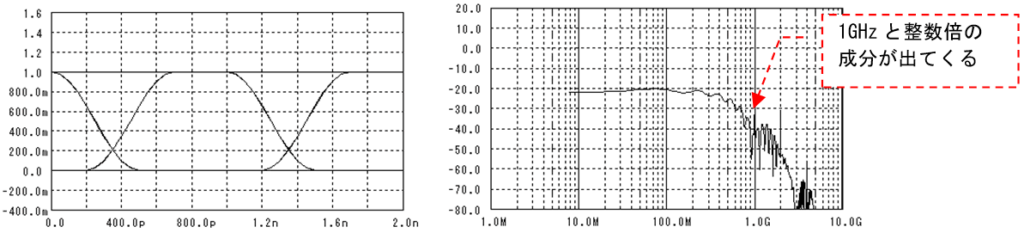

右側の図は、その受信差動信号をアイパターン表示したものです。

本来、アイパターンの開口部(中央の“目”の部分)が大きく広がっていれば波形品質が良好であることを示しますが、2Gbps伝送では、アイ開口が上下・左右方向とも十分なマージンが確保できていない状態が見て取れます。

このように、

- 「伝送路で高域成分が減衰し、波形振幅が縮小」

- 「その結果、アイパターンの開口も狭くなり、データの判別が困難」

という問題が発生します。

結論として、2Gbps伝送ではそのままではアイ開口が不足するため、何らかの波形補償(イコライザやPre-emphasisなど)が必須となるということが分かります。

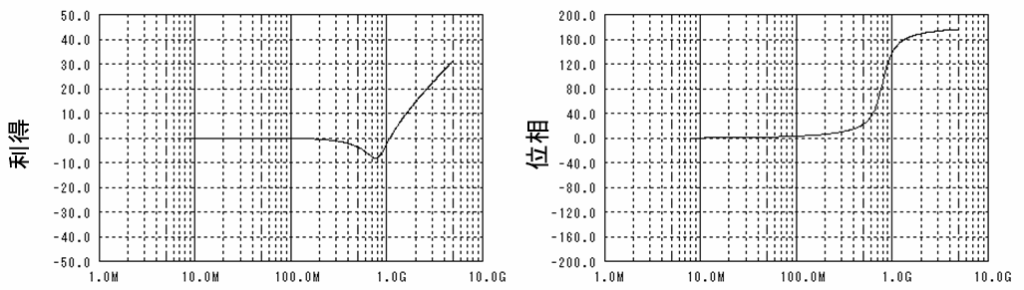

波形補償戦略 ― 良好なアイ開口のために

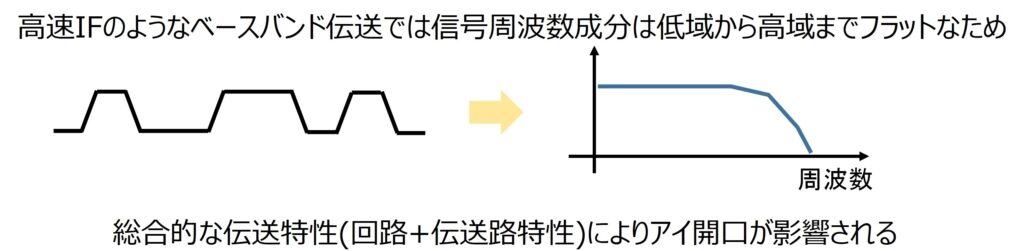

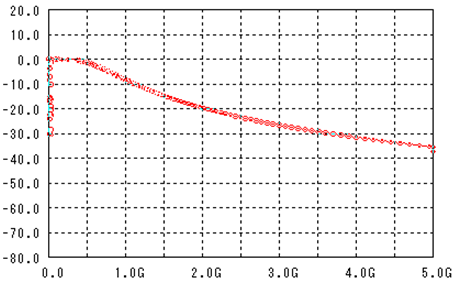

高速インターフェース(高速IF)における波形品質確保のカギは、「アイパターンの開口度」にあります。このアイ開口を十分に確保するには、**システム全体(回路+伝送路)で“フラットな周波数特性”**を持つことが重要です。

高速IFのようなベースバンド伝送の場合、信号の周波数成分は低域から高域まで幅広く含まれています。

したがって、信号帯域にわたって均一(フラット)な周波数応答が得られないと、アイパターンが大きく劣化してしまいます。

伝送系全体の特性による波形品質の違い

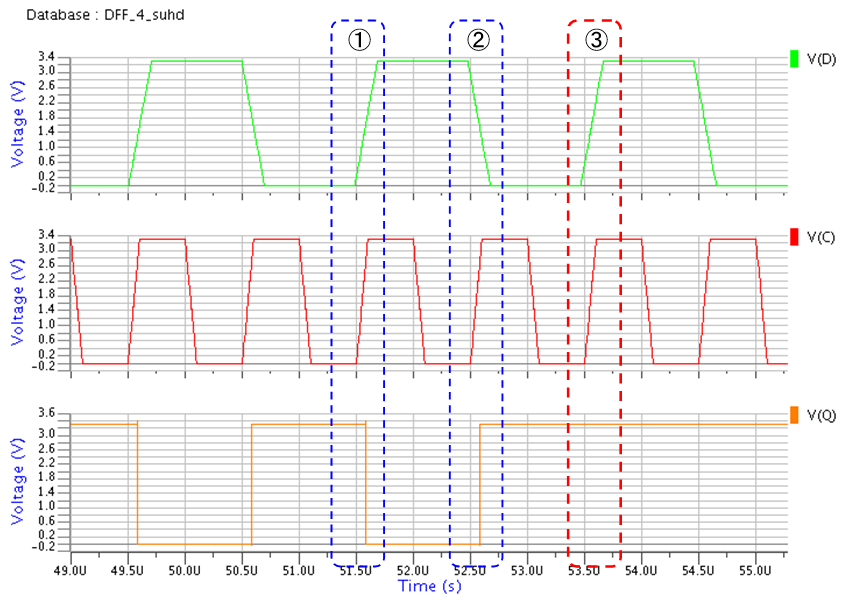

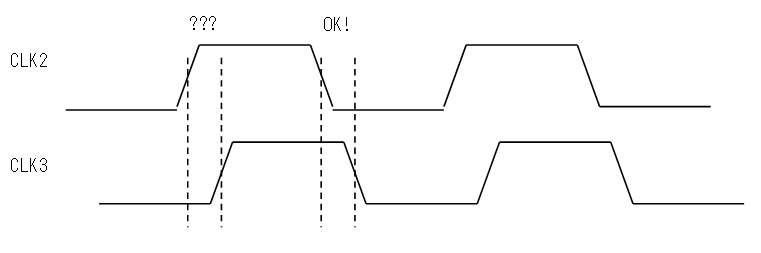

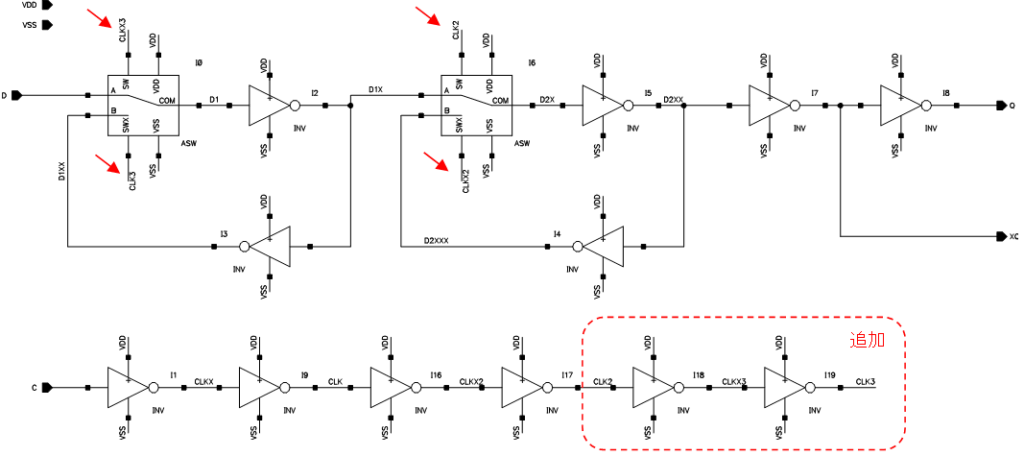

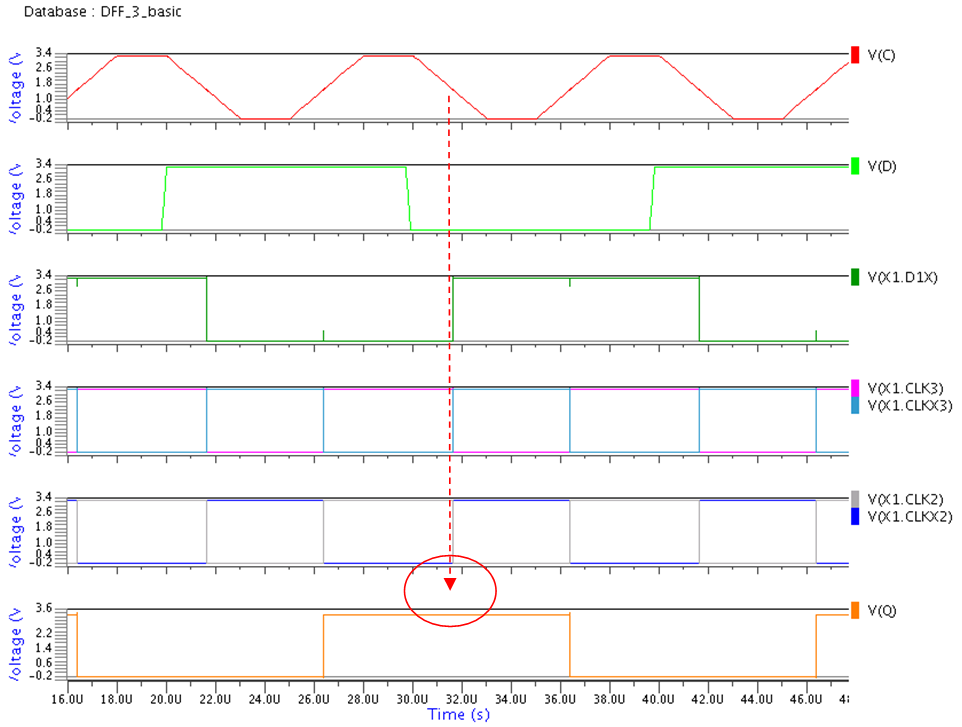

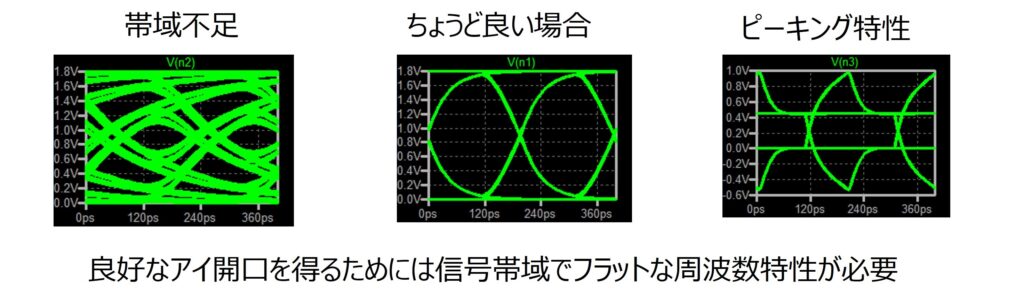

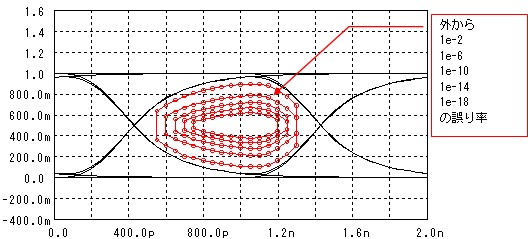

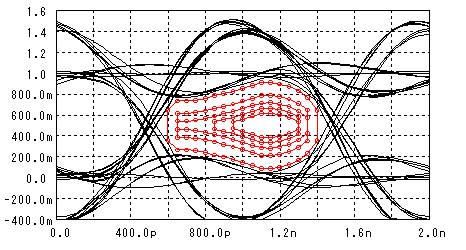

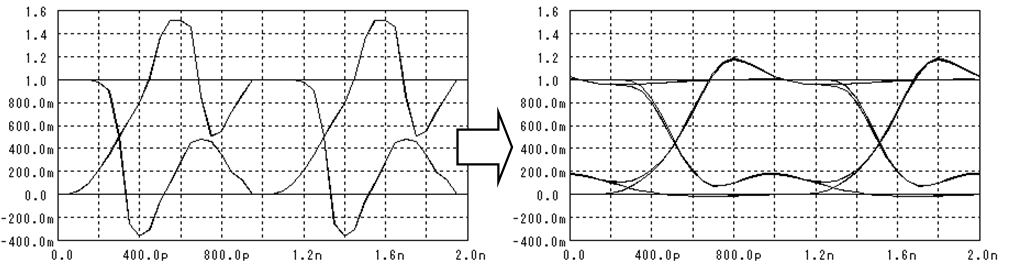

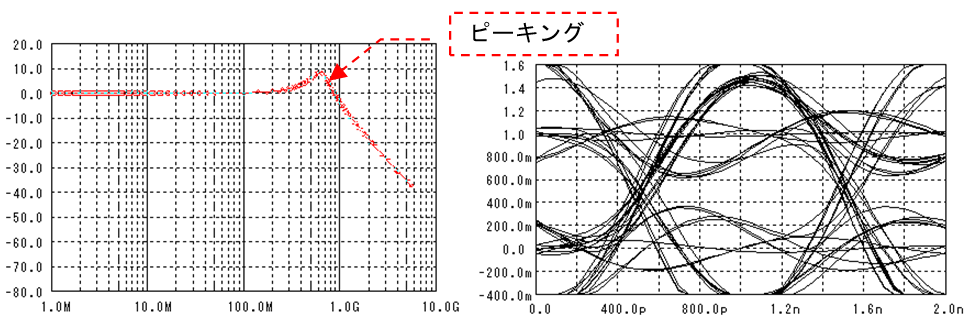

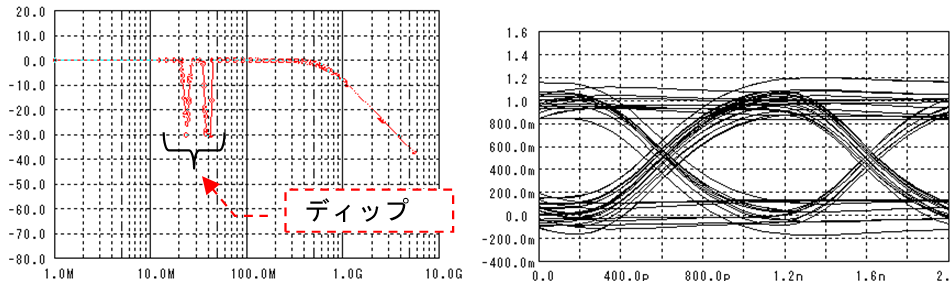

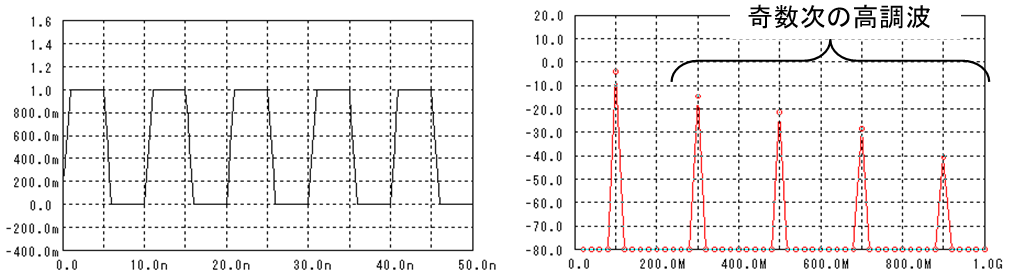

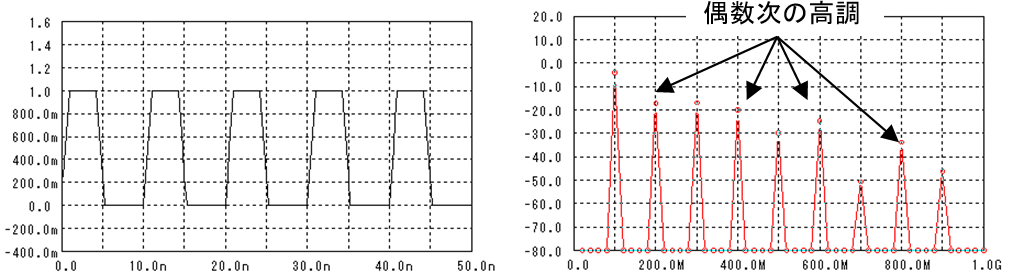

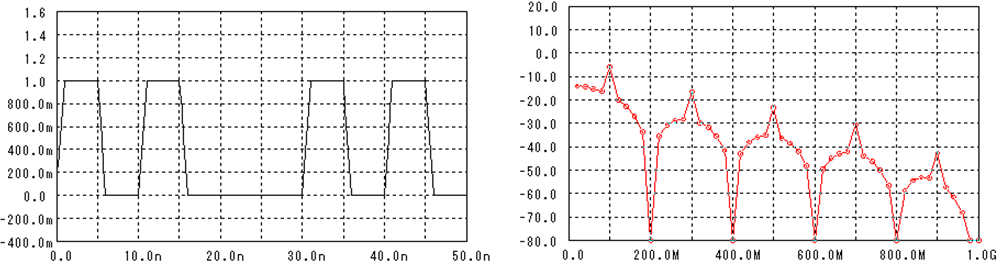

実際の設計現場では、伝送路の帯域特性や、回路と伝送路の総合的な応答がアイパターンに与える影響は大きく分けて次の3パターンに現れます。

- 帯域不足の例:

伝送路や回路の帯域幅が狭いと、高域成分が削られ、アイ開口が狭くなります。

データの判別余裕がほとんどなくなり、ノイズやジッタの影響も受けやすくなります。 - ちょうど良い場合:

必要な帯域幅がしっかり確保できていれば、アイパターンは中央の開口部が大きく、波形品質も良好です。 - ピーキング特性(過補償)の例:

帯域特性を補償しすぎてピーキング(特定周波数帯でゲインが過大)になると、波形が歪んだり、アイパターンの上下幅が不均一になります。

波形補償の必然性と対策

このように「伝送系全体の帯域不足」や「バランスの悪い補償」は、アイ開口の悪化や信号品質の劣化を招きます。

良好なアイ開口を得るためには、“フラットな帯域応答”を目指して、伝送系の総合特性を調整することが重要です。

現場で伝送路の帯域特性が不足している場合、回路側で工夫する=イコライザ(等化器)の導入が必要となります。こうした補償技術を適切に選択・設計することで、“波形品質”と“データの信頼性”を大きく向上させることができるのです。

次回は、イコライザ機能についてご紹介する予定です。

は、

は、

は、

は、