こんにちは。今日はDVFS機能搭載プロセッサとDVFSの動作原理についてお伝えします。

前回の記事はこちら

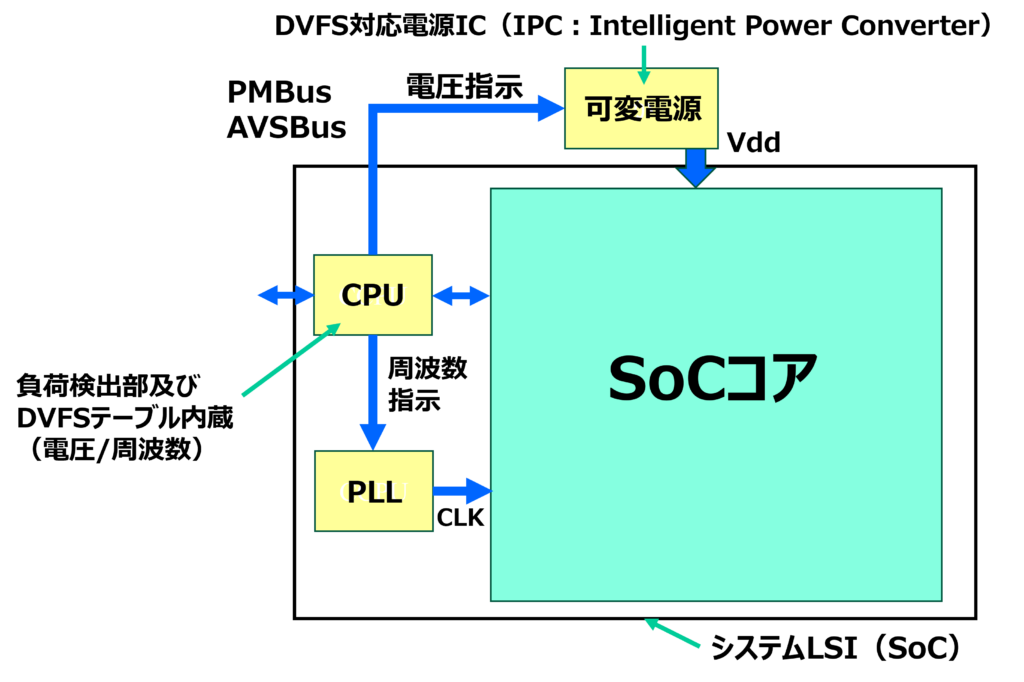

DVFS機能搭載プロセッサのブロック図

まず、DVFS機能搭載プロセッサについてです。図1に弊社が電源ICで用いているDVFS機能搭載プロセッサのブロック図を事例として示します。

CPU内にクロック周波数/電源テーブルが配置され、負荷の大きさに対応するクロック周波数及び電源電圧Vddの指示情報をテーブルから出力します。

指示情報に基づきPLL及び可変電源を制御し、DVFSを実行します。すなわち、負荷の大きさに適合したクロック周波数、電源電圧を用いてDVFSが最適な値を選択実行することになります。

半導体企業の可変電源(DVFS対応電源IC)の製品例

半導体企業の可変電源(DVFS対応電源IC)の製品例を以下に示します。

| 半導体企業 | 製品例 |

| 1. TI | LM25066A |

| 2. リニアテクノロジー | LTC3886 |

| 3. ダイアログ・セミコンダクタ | DA9063 |

| 4. ルネサス | ISL69269 |

| 5. オンセミコンダクタ | NCP81022 |

| 6. ADI | LTM4680 |

| 7. ディークルーテクノロジーズ | DCT013C(開発品) |

また、Appleは、iOSなどのソフトウェアとAシリーズチップなどのハードウェアを密接に統合し、DVFSを効果的に活用しています。

Apple Mobile Processor における動的電圧スケーリング技術(DVFS)(2024年9月 弊社調べ)

- プロセッサの負荷監視: プロセッサ内部のセンサーやモニタリング機能が、プロセッサの負荷状況を定期的に監視する。これには、タスクの実行中の処理負荷や電力消費の推定が含まれる。

- 電圧と周波数の調整: 負荷の高い場面では、プロセッサの動作周波数を上げ、同時に電圧も増加させることで性能を最大限に引き出す。一方、負荷が低いときには、動作周波数を下げ、電圧を低く保ちながらも十分な処理能力を維持する。

- スケーリングアルゴリズム: モバイルプロセッサには、動的電圧スケーリングを行う専用のアルゴリズムが組み込まれている。これらのアルゴリズムは、プロセッサの状態を評価し、最適な電圧と周波数の組み合わせを決定する。

- バッテリー管理: バッテリーの残量や充電状態なども考慮に入れながら、電圧と周波数を調整する。

DVFSの動作原理

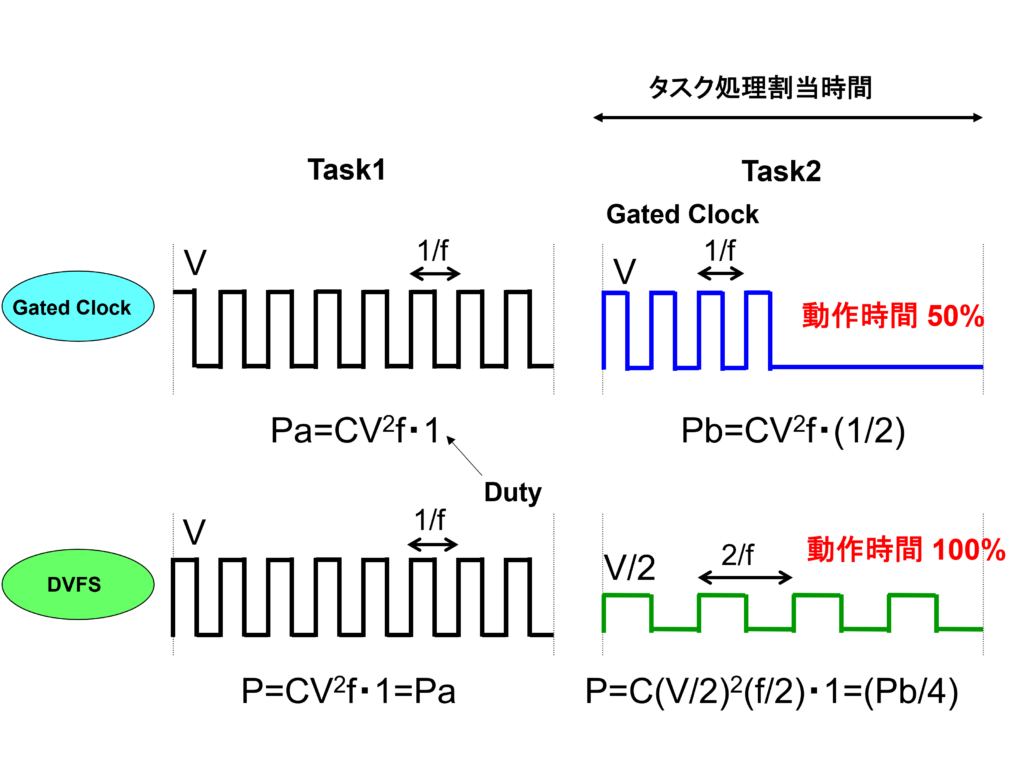

図2にDVFSの原理を示します。

まず上段の説明です。一般に低消費電力化を図るため、SoCではゲーテッドクロックが用いられます。Gated Clockは負荷が軽い場合、所要の処理が終了するとクロックを止めます。これで、タスク処理割当時間後半にはクロックを止めるので、1動作時間を半分=消費電力1/2を図れます。

次に下段の説明です。DVFSではタスク処理割当時間丁度で処理が終了する様に、1/2の電源電圧、1/2のクロック周波数でSoCを動作させます。 すなわちDVFSはゲーテッドクロックに比べて、さらに1/4の消費削減を図れます。

なお、CMOSの特性から、クロック周波数に比例して電源電圧を下げる事ができます。

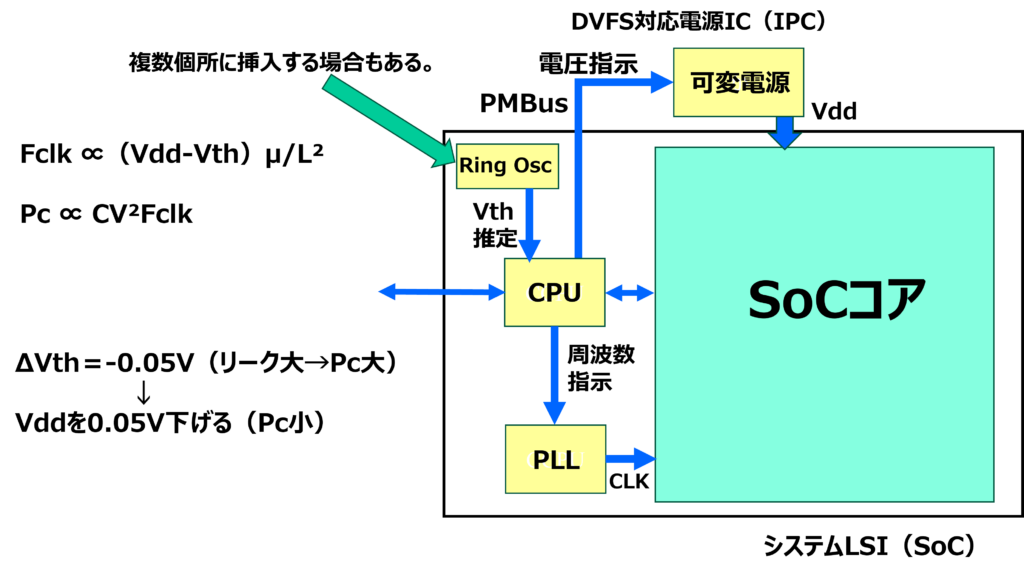

プロセスバラツキを考慮したDVFS機能搭載SoC/MPU/GPU

次に図3にプロセスバラツキを考慮したDVFS機能搭載SoC/MPU/GPUのブロック図を示します。

リングオシレータ(Ring Osc)の発振周波数からMOSトランジスタの閾値(Vth)を推定します。例えばVthが低い方向に0.05Vばらついた場合、回路の動作周波数が上がります。同一周波数で動作させる場合、電源電圧(Vdd)を下げる事ができるので、消費電力を更に低減できます。一般にVthが低下するとトランジスタのリーク電流が増加しますが、Vdd低減による低消費電力化により相殺できます。こうした工夫によりプロセスバラツキを考慮した設計ができます。

なお、SoCの作りに応じて、リングオシレータは複数個所に挿入されることがあります。

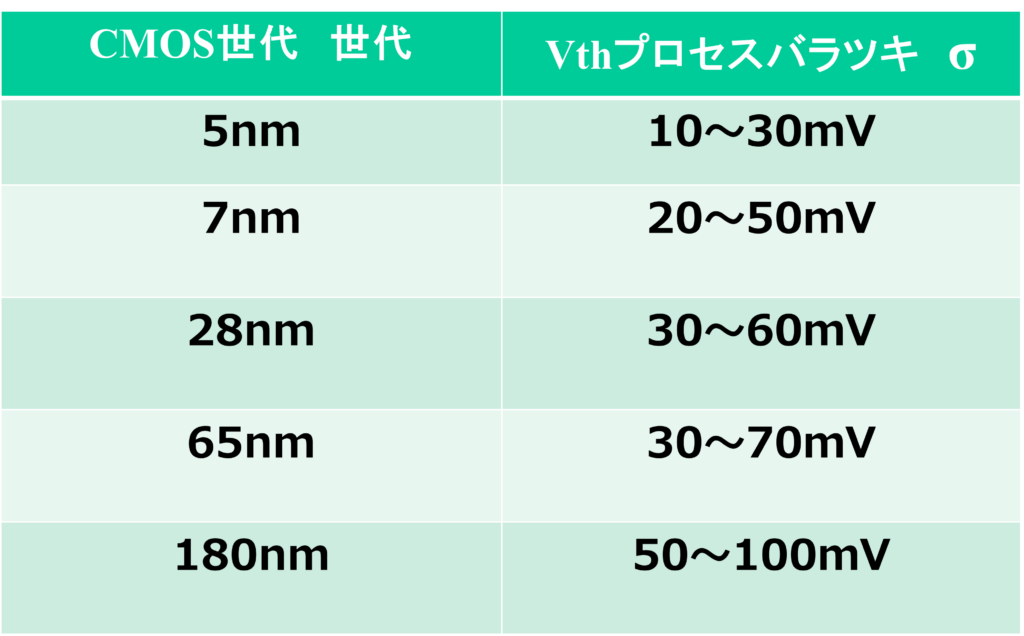

参考までに各CMOS世代におけるVthのプロセスバラツキを示します。

いかがでしょうか。

次は、動的電圧スケーリング(DVS)開発の背景をお伝えしようと思います。

コメント

この記事へのコメントの受付は締め切りました。