前回はとトランジスタのオフセット電圧が引き起こす問題について紹介しました。

今日は、その対策について触れたいと思います。

トランジスタのオフセット電圧対策

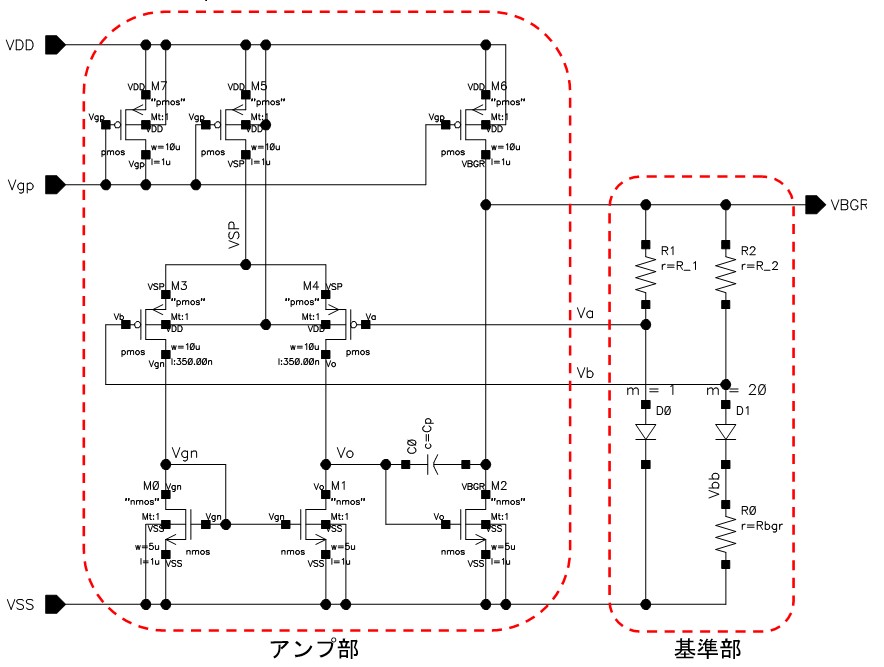

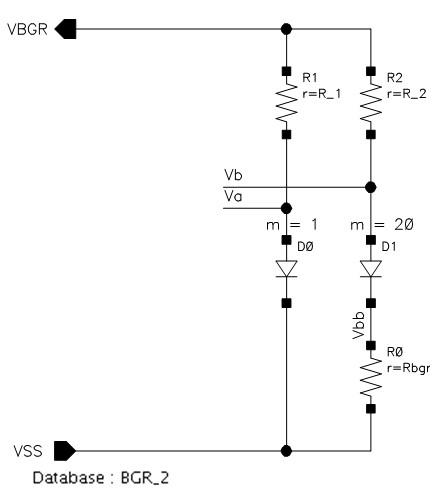

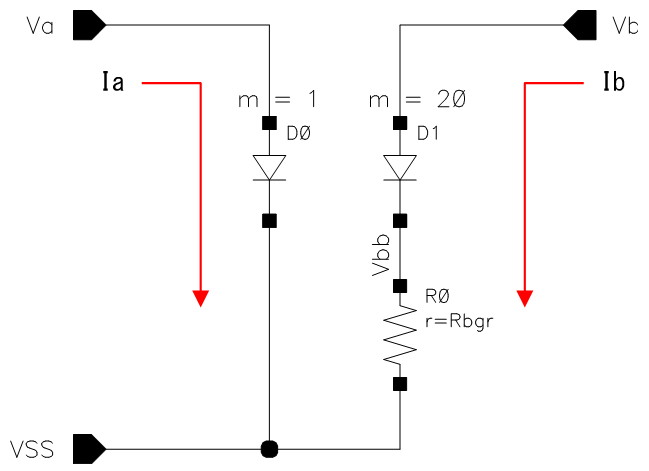

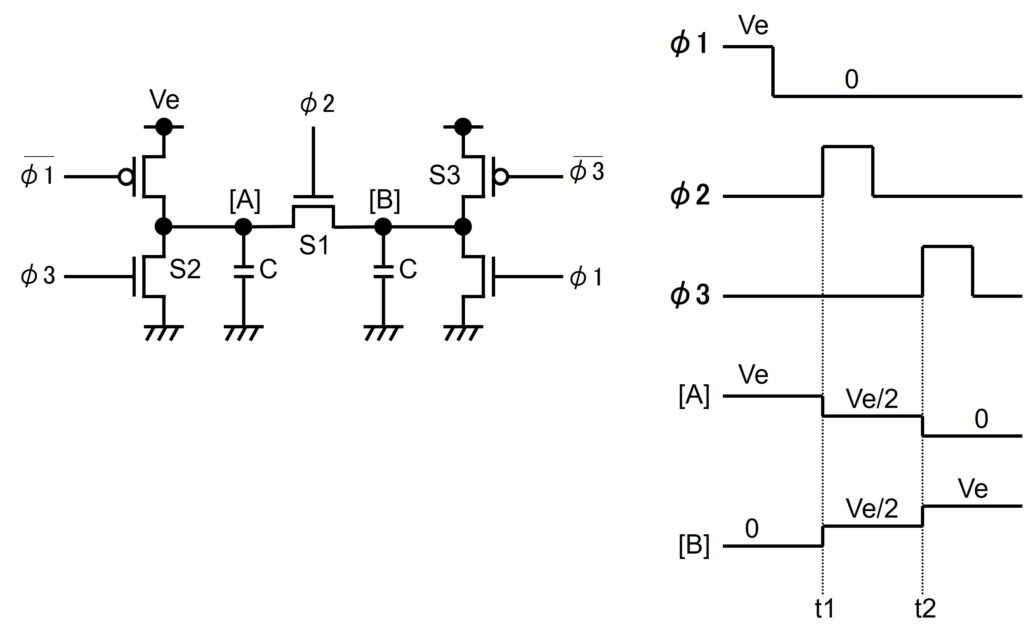

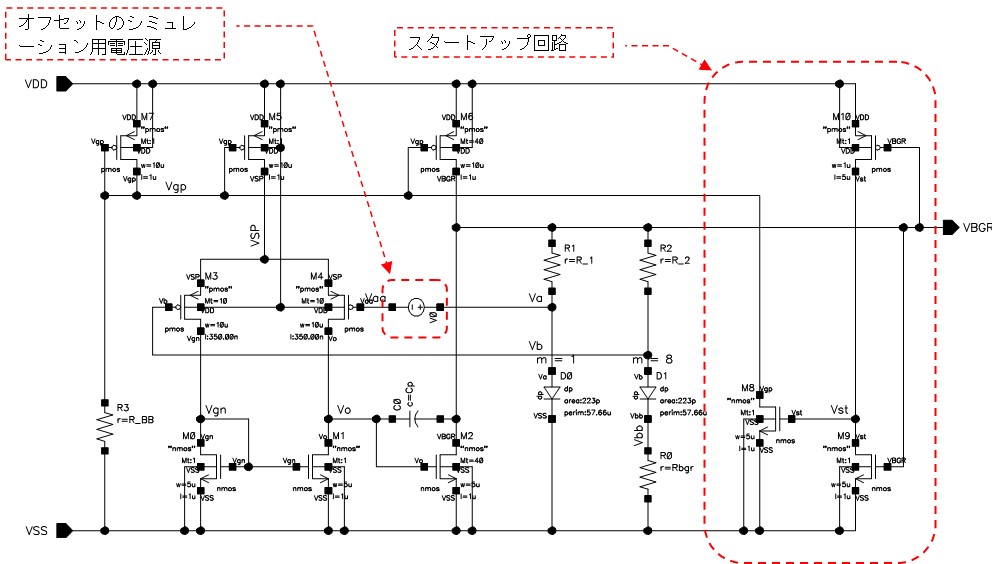

オフセット電圧のためループが誤った動作点に収束し、BGR電圧が起動できなくなることを防止するためには、スタートアップ回路が必要になります。

スタートアップ回路はBGR電圧(VBGR)を監視していて、電圧が低いと(つまり、起動できていないと)何らかの方法で、ループが誤った動作点に収束しないようにする回路です。

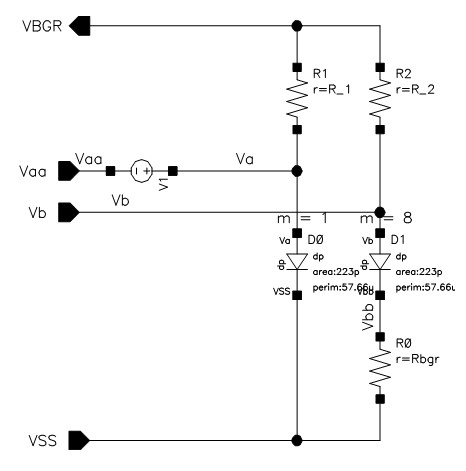

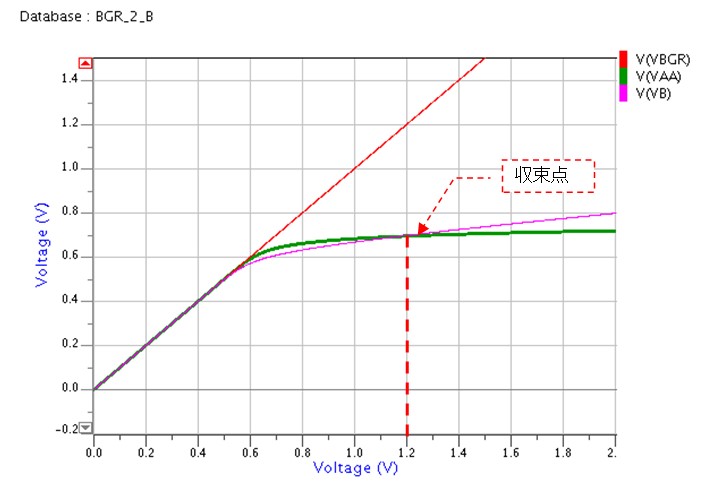

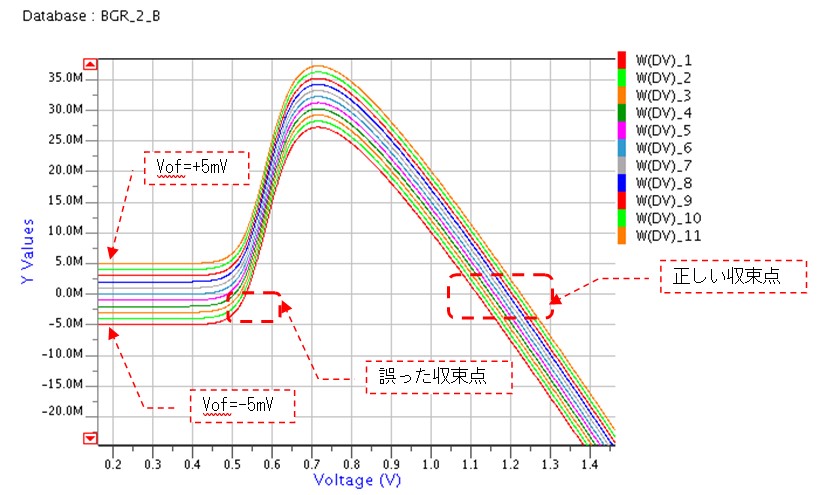

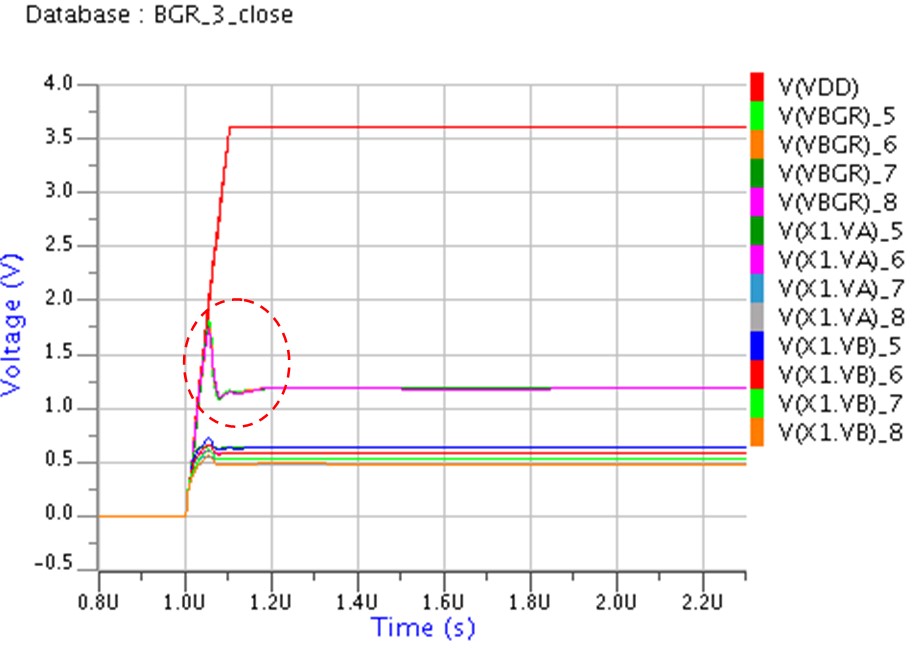

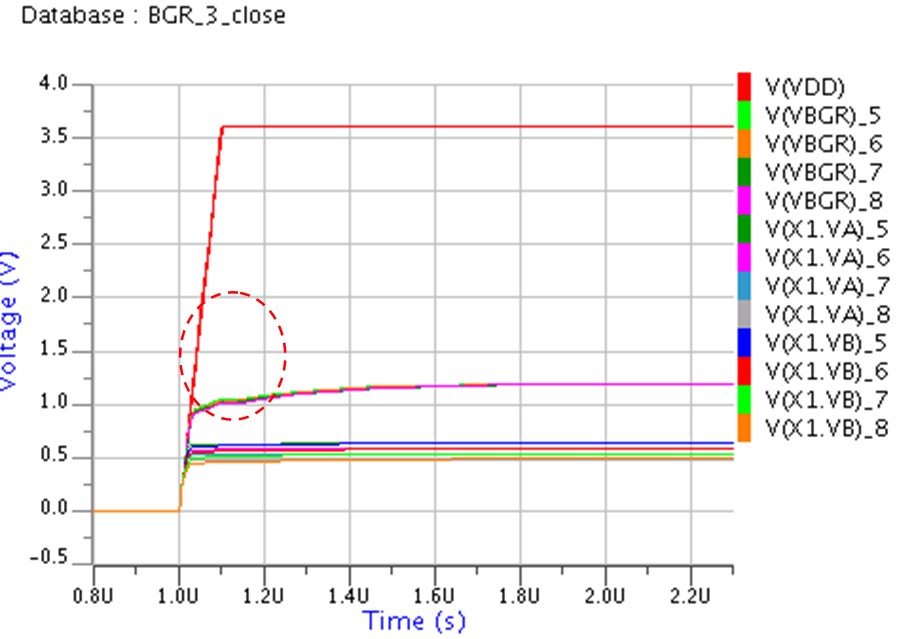

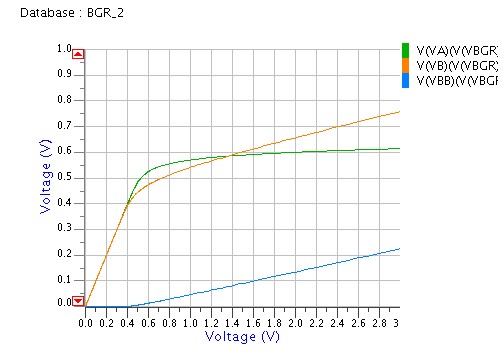

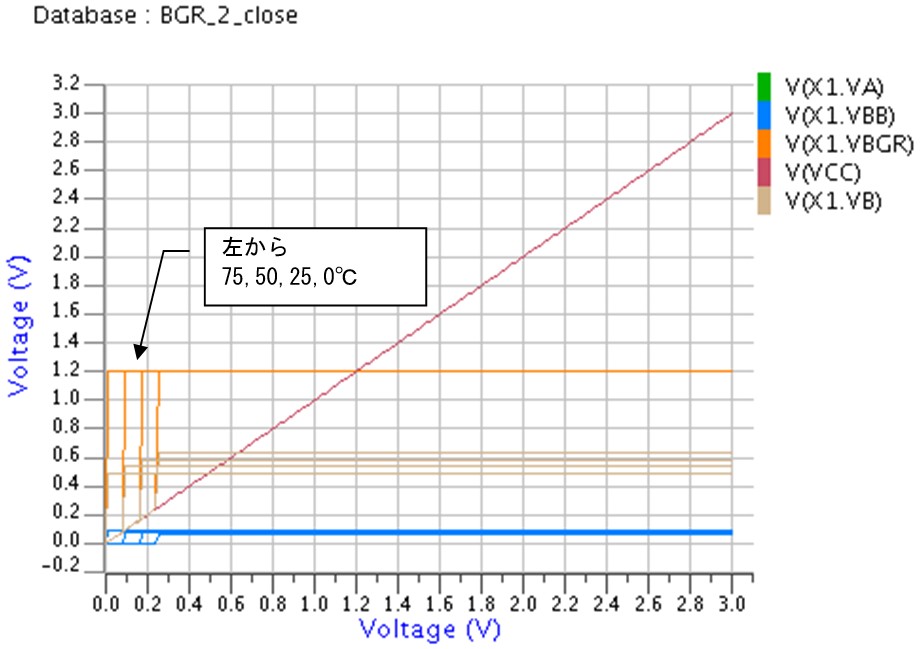

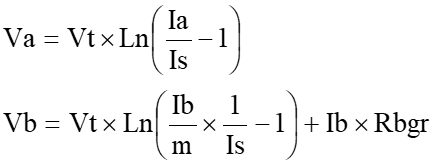

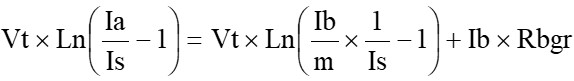

誤った収束点ではBGR電圧は0.5V程度の非常に低い値となります(前回BLOG参照)。ここに収束しないように強制的に電流を流してやり、オフセット電圧を打ち消せるだけの差電圧がVaとVbに発生するようにしてやります。

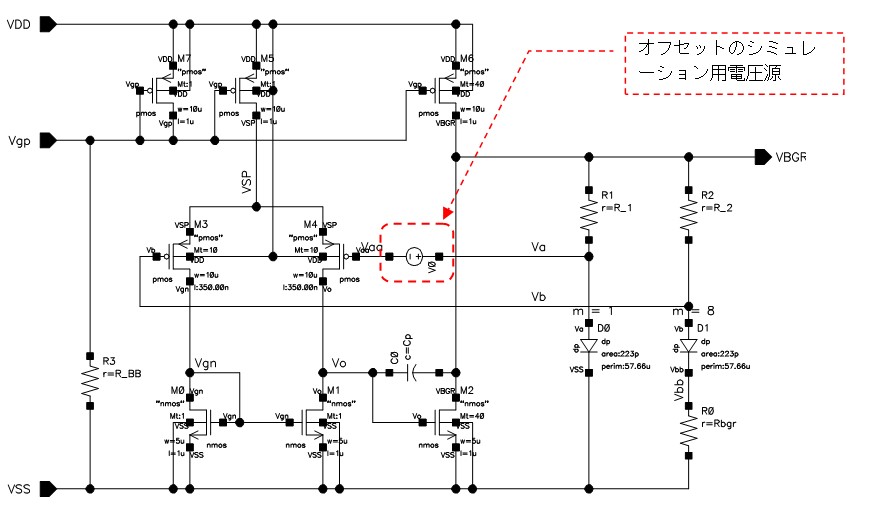

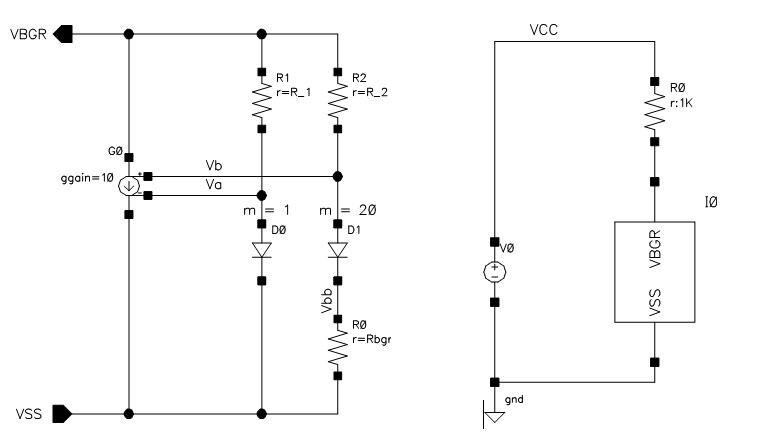

図 1ではM9とM10で構成するインバータがBGR電圧を監視していて、閾値(M9とM10のL/Wで調整しています)以下の時はインバータ出力電圧Vstが高くなり、M8に電流が流れます。この電流はPchのゲート電圧を下げ、M6の吐き出し電流を増やし、BGR基準部に流れる電流を増やします。

ここまでくれば、後は圧縮アンプが自動的に正しい収束点まで導いてくれます。

きちんとBGR電圧が起動できた後は、強制的に流していた電流は不要となるので、オフさせます。

図 1でM9とM10で構成するインバータの閾値よりBGR電圧が高くなると、インバータ出力電圧Vstが低くなり、M8に流れていた電流がオフします。

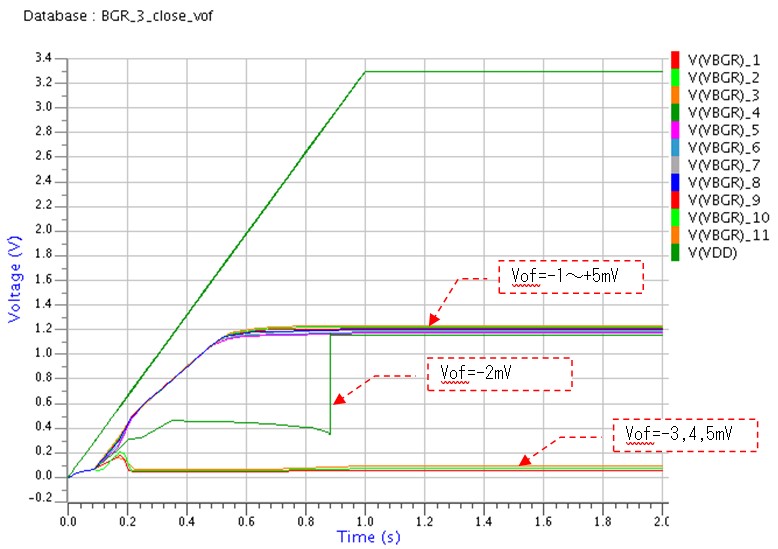

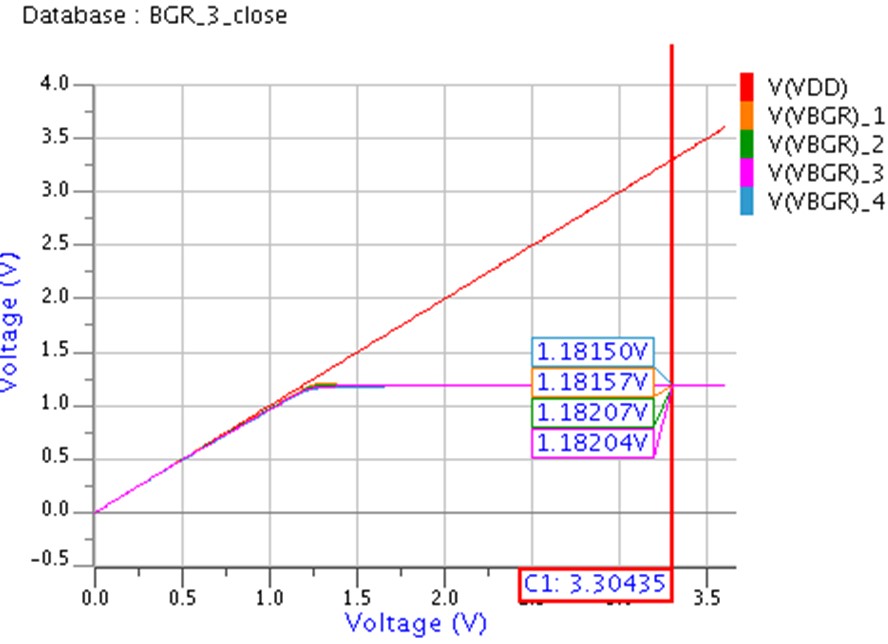

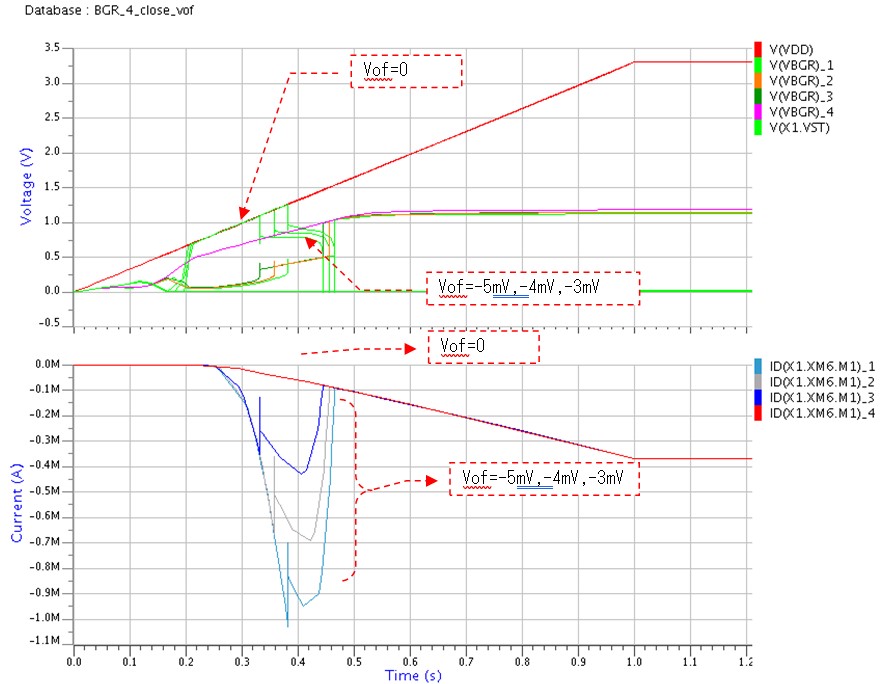

スタートアップ回路に依って、前回のBLOGではBGR電圧が起動できなかった、-5mV、-4mV、-3mVもきちんと起動できるようになりました。

スタートアップ回路の設計ポイント

スタートアップ回路には、いくつかの別の方法があります。

BGR電圧を直接監視しないで基準部に流れる電流を監視するものや、強制的に電流を流すのではなく、電圧を強制的に動かすものなど色々あるのですが、

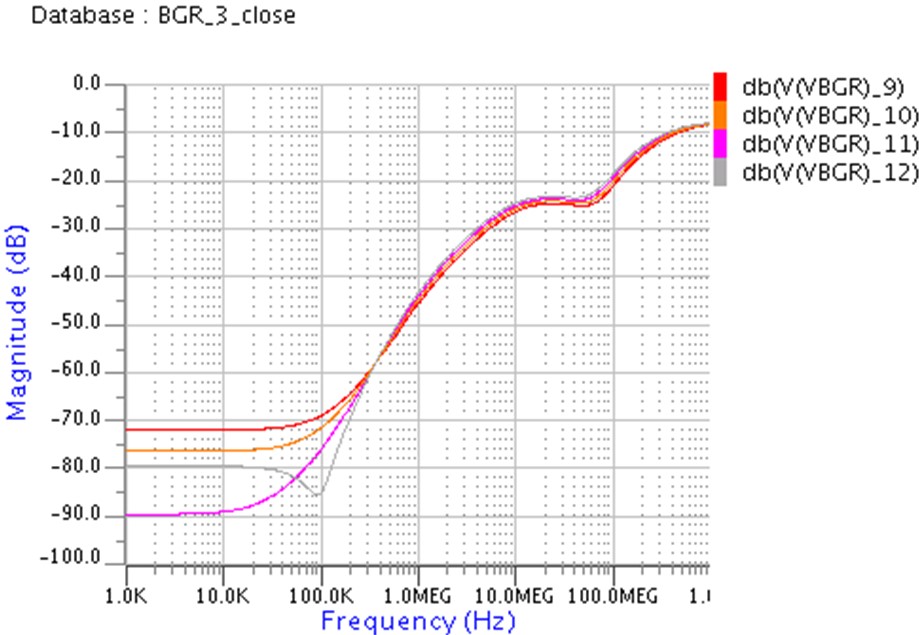

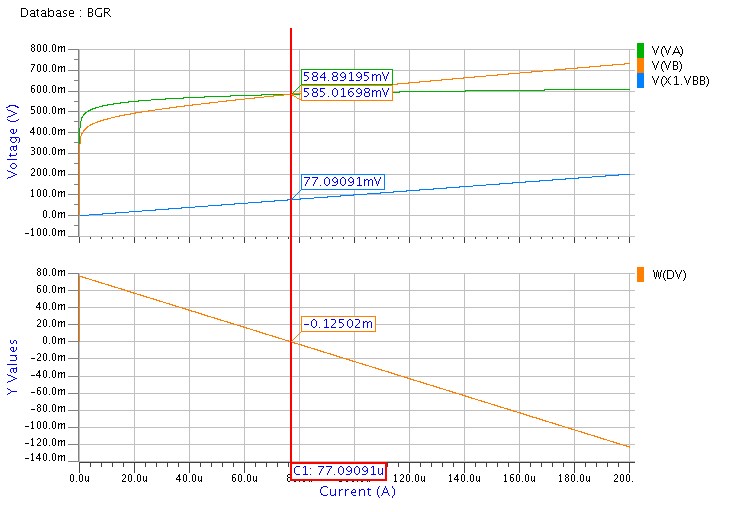

- BGRの起動がきちんと監視できるか

- 強制的に流す電流は十分か(圧縮アンプに負けないか)

- 起動後はオフできているか

がスタートアップ回路設計上のポイントと思います。

BGRに関しては今回でひとまず終わりにしたいと思います。