今回は、DFFを安定して動作させるには、”前の状態をラッチした後、D1Xが変化する”ようにすれば良い事をもう少し詳しく説明したいと思います。

前回の記事はこちらです。

スレーブラッチの動作

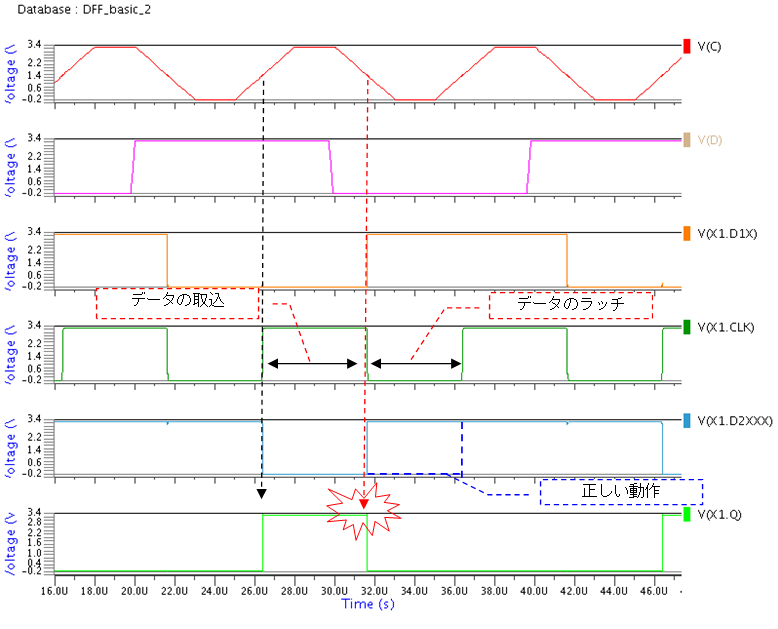

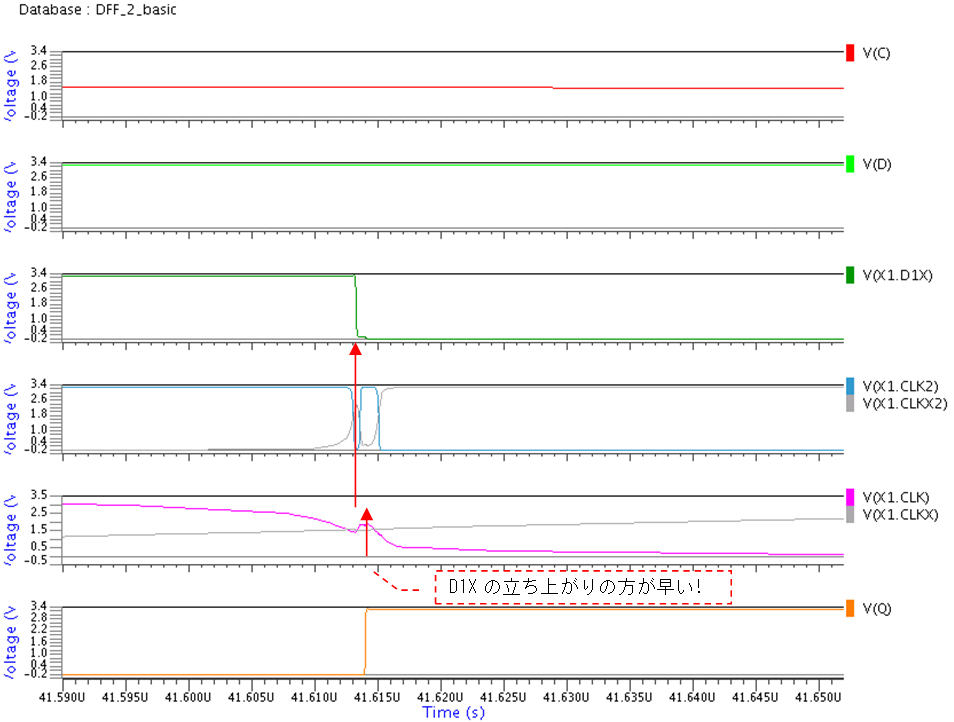

DFFに入れるCLKのTr/Tfを遅くした波形を図 1に示します。

DFFの出力V(Q)の動作がおかしくなっています。クロックV(C)の立上がりだけではなく、立下りでも変化してしまっています。これは、スレーブラッチが正しく動作しなくなっているために起きている現象です。

スレーブがデータを取り込んで(図ではD1Xの“L”を取り込んで)、これをラッチする(32usecのちょっと前のCLKの立下り)事ができず、入力データD1Xの変化がそのまま出力Qに現れてしまっています。

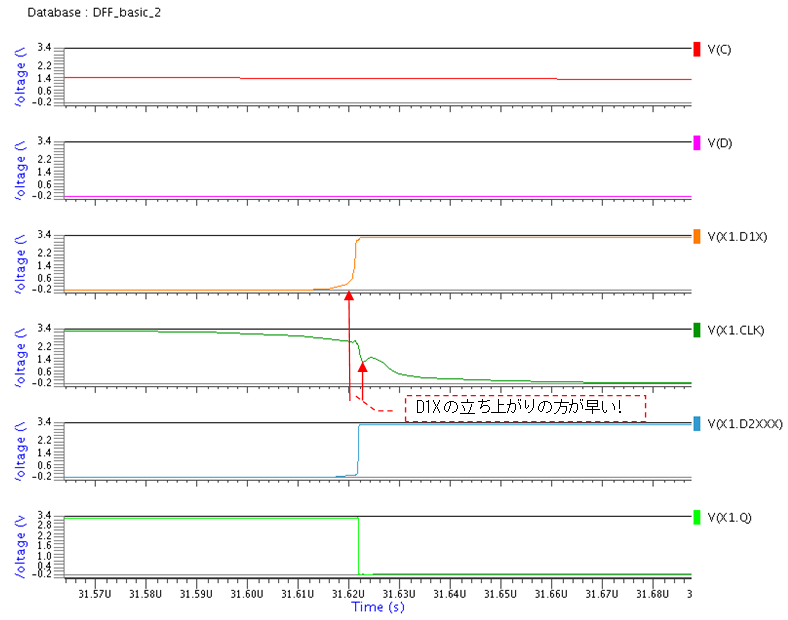

問題の部分を拡大してみると・・・

図 2の拡大図を見ると分かるように、ほんの僅かですがD1Xの立ち上がりのほうが早くなっています。

本来の動作は、CLKの立下りの後、D1Xが変化しないといけないのですが、CLK波形のTr/Tfが遅くなったため順番が逆になってしまったのです。

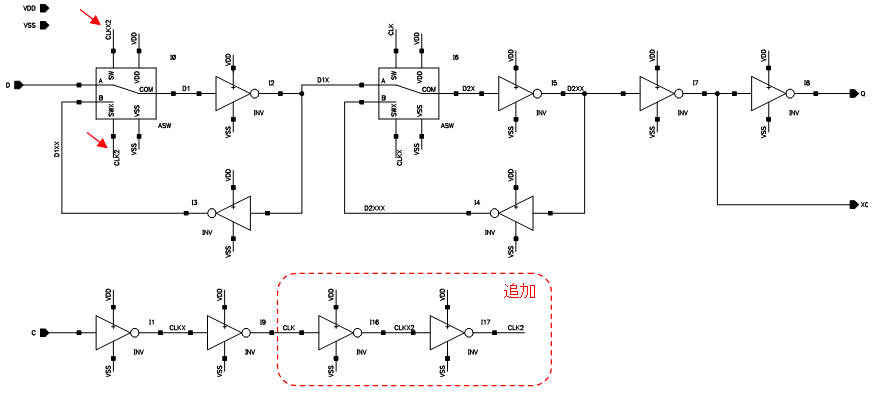

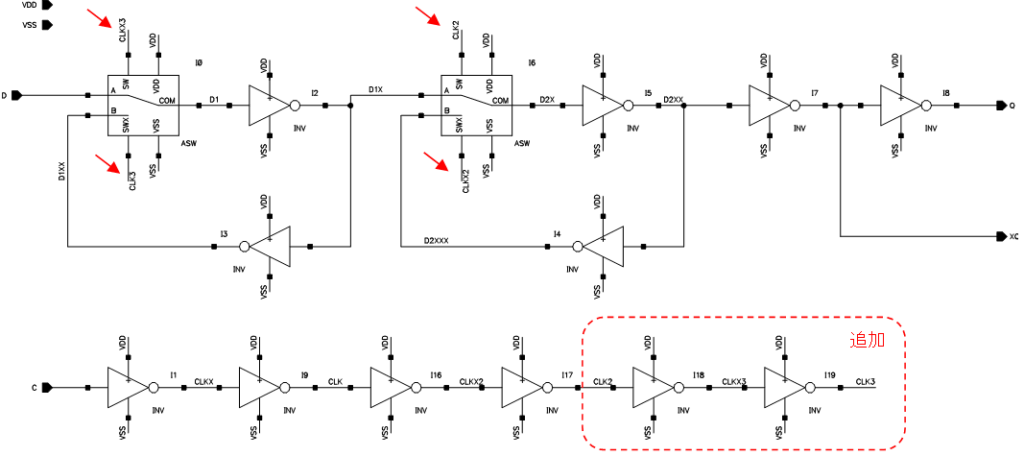

マスターラッチのクロック調整

D1Xの立ち上がりを遅くするためにマスターラッチ用のクロックを遅くしてみました。

これでうまくいくはずだったのですが・・・

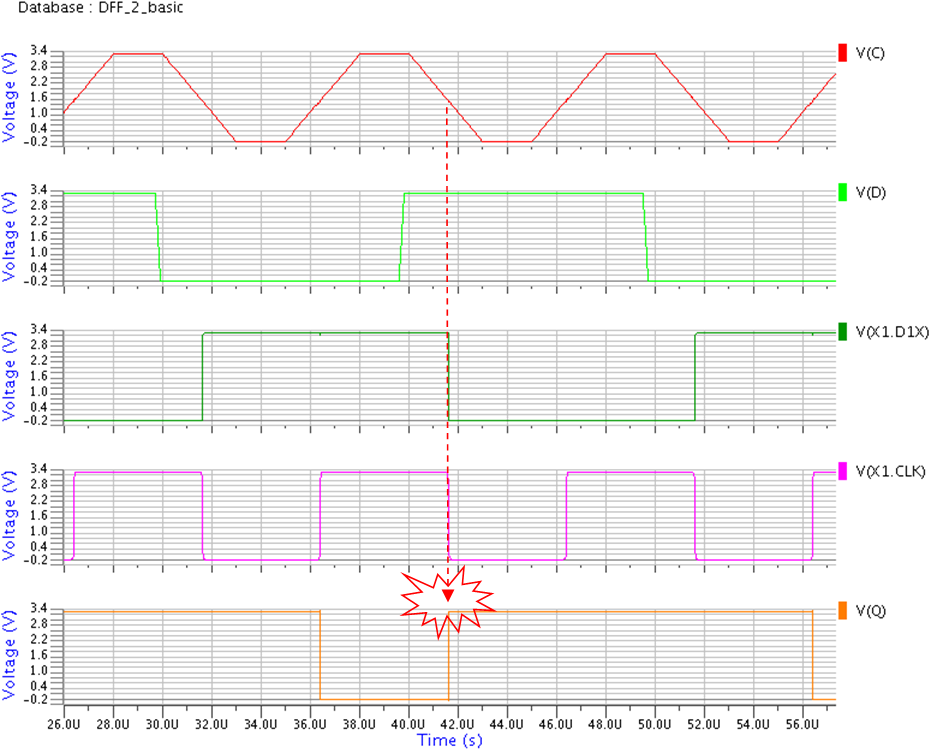

残念ながら直っていません(T_T)。何で?と拡大してみると。。。

まだ、D1Xのほうが早く動いてしまっています。

単純なインバータで遅延を作ったのがまずかったようで、CLK2(遅らせたいCLK)の方が後ろにあるのですが、利得が高くなっているために先に動作してしまっています。

インバータの追加

それならばという事で、更にインバータを追加してみます。

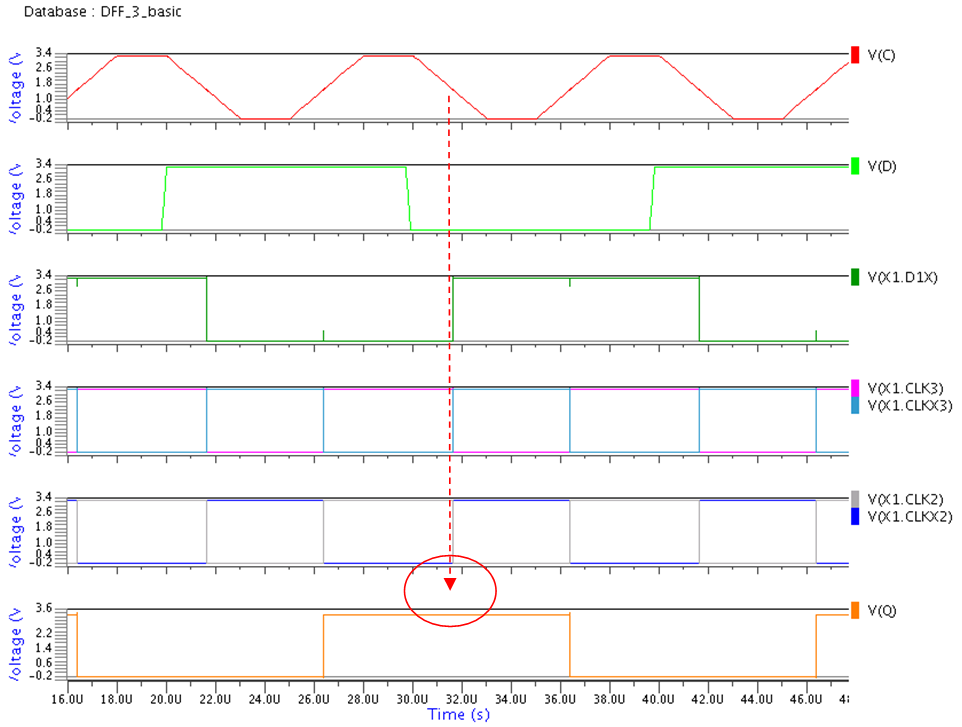

確かに、D1Xの方が遅くなっています。。。しかし、その差は500psec以下!!

実際の回路では寄生容量など回路図にはないデバイスの影響もあるので、このくらいの差はひっくり返ってしまうこともあります。

以上の様に入力CLKのTr/Tfが遅くなるとDFFは誤動作を起こしてしまうので、Tr/Tfに制限をつける必要があります。

次回は、入力データとクロックの位相関係について触れたいと思います。