今回は、ΔΣ ADCシリーズの最終回。ノイズ伝達関数と、モデル化についてご紹介します。

前回の記事はこちら。

第8章 ノイズ伝達関数(NTF)計算

前章ではオーバーサンプリング比(OSR)と変調器の次数を決めました。

次に行うべき工程が ノイズ伝達関数(NTF:Noise Transfer Function)の設計です。

NTFは、ΔΣ変調器の「ノイズをどう通し、どう抑えるか」を数学的に表したものです。言い換えると、量子化ノイズをどの周波数帯へ押し出すか を直接決めるのが NTF です。

◆NTFがなぜ必要か

3章のノイズシェーピングの所で少し触れましたが、ΔΣADCでは、量子化ノイズを

- 信号帯域内(低周波):抑圧したい

- 帯域外(高周波):押し出したい

という目的でフィードバック制御を行います。

この「周波数ごとのノイズの通りやすさ」を示すのが NTF です。NTF がうまく設計されていれば、帯域内のノイズ量は非常に小さくなり、SNR が大幅に改善します。

逆に、NTF の形が適切でないと、

- ループが不安定になり発振する

- 理論値通りの SNR が出ない

- 過大な内部信号が発生しオペアンプが飽和する

といった問題が起こります。

つまり、NTF は ΔΣADC の性能と安定性を左右する“要”の1つと言えます。

◆制御理論から導かれる NTF の基本式

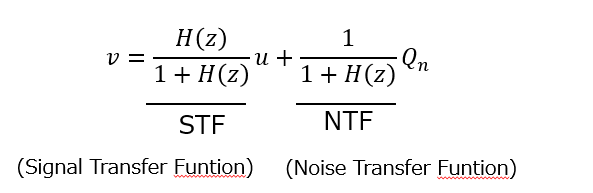

ここで再び3章のノイズシェーピングでご紹介した式の登場です。ΔΣ変調器はフィードバック制御系と同じ構造を持っており、そのオープンループゲインをH(z)とすると、出力は次の形で表されます:

この式の後半部分 が、量子化ノイズへの影響(ノイズ伝達関数)を表した項になります。

STF と NTF

- STF(Signal Transfer Function) = H(z) / (1 + H(z))

→ 入力信号がどれだけ通るか - NTF(Noise Transfer Function) = 1 / (1 + H(z))

→ 量子化ノイズがどれだけ通るか

ΔΣADCでは STFはほぼフラット(=信号はそのまま通す)

NTFは高周波でノイズが通りやすくなる形状 を目指して設計します。

◆NTFの設計方針:次数と形をどう決めるか

前章で決めたように今回の構成は

- 次数:2次

- OSR:500

- 目標SNR:98 dB

ですので、必要なNTFの性質は次の通りです。

① 2次のノイズシェーピング

2次のΔΣでは、NTFはおおよそ

という形を持ちます。これは、

- 低周波(z ≈ 1)で NTF ≈ 0 → ノイズは強く抑圧

- 高周波では NTF が急激に上昇 → ノイズを帯域外へ押し出すことを意味します。

② OSR=500 に応じたフィルタ形状

OSRが十分大きい場合、帯域内ノイズは NTF の次数でほぼ決まります。

今回の構成(2次・OSR=500)では計算上、98 dB 以上のSNRが得られる NTF を設計可能です。

◆NTF設計時の注意点

NTFは強力なノイズシェーピング効果を生み出しますが、同時にループの安定性にも影響するため注意が必要です。

主な注意点は以下の3つです:

- 内部信号の振幅が大きくなりすぎないこと:次数を上げたり NTF の形を急峻にしすぎると、積分器内部の信号が飽和し、実回路で破綻します。

- 極(Pole)の配置:NTF から逆算される H(z) の極配置が不安定領域に入らないようにする必要があります。

- 実回路の素子ばらつきの影響:NTF が理想的でも、アナログ部分のばらつきで想定通りのゲインが確保できない場合、安定性が損なわれるため、係数 a₁, a₂ などの調整が重要です。

次章では、この NTF に基づく ΔΣ変調器モデルを実際に作り、波形シミュレーションで性能を確認する工程について説明します。

第9章 モデル作成および特性検証

前章までで、ΔΣ変調器の構成要素・OSR・次数・NTF設計がすべて整いました。次に行う工程が モデル化(Modeling)と特性検証(Simulation) です。

ΔΣADCはアナログ回路・ディジタル処理・制御理論が混在するため、いきなり回路設計を始めても思った通りの性能が得られないことがほとんどです。そのため、実回路に着手する前に、抽象モデルを作成して特性を確認することが重要です。

今回の設計では、Verilog A等を用いて ΔΣ変調器の2次モデルを構築し、入力信号に対してどのような 1bit 出力が得られるかを確認しています。

◆時間波形で見るΔΣ変調器の振る舞い

青線が入力アナログ信号(例:微小な1kHzの正弦波)、赤線がΔΣ変調器の 1bit 出力 です。

1bit 出力は 0 / 1(または ±1)を高速に切り替えますが、その切り替わりの頻度(=出力デューティ)が入力信号に対応しています。

入力信号が上昇すると1bit出力の “1” の密度が増え、入力信号が下降すると “0” の密度が増えるため、

この密度情報を後段のディジタルフィルタが取りまとめることで、アナログ値相当の情報が得られます。

◆FFT波形で見る量子化ノイズのシェーピング

赤線が1bit出力の周波数スペクトル(FFT)です。図を見ると、次の特徴が確認できます。

■ 信号成分(ピーク)

約1kHz付近に鋭いピークが見えており、入力のサイン波が正しく変調の中で保持されていることがわかります。

■ 量子化ノイズの帯域外への追い出し(ノイズシェーピング)

FFTの低周波側(信号帯域)ではノイズが大きく抑圧され、高周波側に向かってノイズが増加していることが分かります。図の青色で塗られた領域が 量子化ノイズ であり、これは前章で説明した NTF の働きにより帯域外に押し出されていることを示しています。

これは ΔΣADC のもっとも重要な特徴であり、帯域内ノイズの低減 → 高SNR の実現 に直結します。

◆ここまで検証したら、回路設計へ

今回の例では、時間波形・FFT波形から 2次・OSR=500 の構成で設計仕様(98 dB SNR)が達成可能

であることがモデルシミュレーションで確認できています。

モデルシミュレーション検証は、ΔΣADC設計における重要ステップです。時間波形で ΔΣ変調器の動作を、FFTでノイズシェーピング効果を可視化することで、設計したOSR・次数・NTFが妥当であるかを確認できました。

本稿ブログのシリーズも長くなりましたので、回路設計はまた機会があればご紹介したいと思います。では最後に、ΔΣ ADC システム設計でのポイントをまとめます。

◆まとめ

本シリーズでは、ΔΣADC(デルタシグマA/Dコンバータ)について、その「基本概念」と「システム設計の手順」を段階的に解説してきました。

前半で、ΔΣADCが

- 少ないアナログ回路で高精度を得られるA/D変換方式であること

- オーバーサンプリングとノイズシェーピングが性能向上の鍵であること

- 制御理論(フィードバック)の応用として理解できること

を紹介。ΔΣADCがどのような仕組みで高精度を実現しているのかを押さえました。

また後半では、実際の設計に向けて

- 仕様の決め方(分解能・帯域・SNRなど)

- OSRと次数の選定方法

- NTF(ノイズ伝達関数)の考え方

- モデル構築とシミュレーションの重要性

といったシステム設計手順を順に整理しました。

◆ΔΣADCは今後ますます重要になる技術

ΔΣADCは、計測、通信、音響、医療機器、IoT センサーなど、低消費電力で高精度が求められるあらゆる分野で広く活用されています。近年の半導体プロセス微細化が進む中で、「アナログ+デジタル処理で性能を作り込む」という ΔΣADC の思想は、今後さらに価値が高まると考えられます。

もし今まで「ΔΣADCは難しそう」と感じていたとしても、

ここまで読み進めてくださった読者であれば、設計の入口に立てる知識 を身につけています。これを機に、ぜひご自身で“小さな一歩”から始めてみてください。

ΔΣADCは、深く学べば学ぶほど面白い世界です。

本稿がその第一歩となれば幸いです。