前章では、ΔΣADCの振る舞いが「フィードバック制御系」と同じ原理で動いていることを説明しました。

本章では、そのフィードバックループを構成する具体的なハードウェア要素について整理します。

第4章 ΔΣADCの構成要素

ΔΣADCは、「少ないアナログ回路で高精度を実現する」という特徴を持っています。

構成要素は大きく 積分フィルタ(積分器)・コンパレータ・ディジタルフィルタ の3つです。

これらがループを形成し、量子化ノイズを制御的に抑圧する仕組みをつくっています。

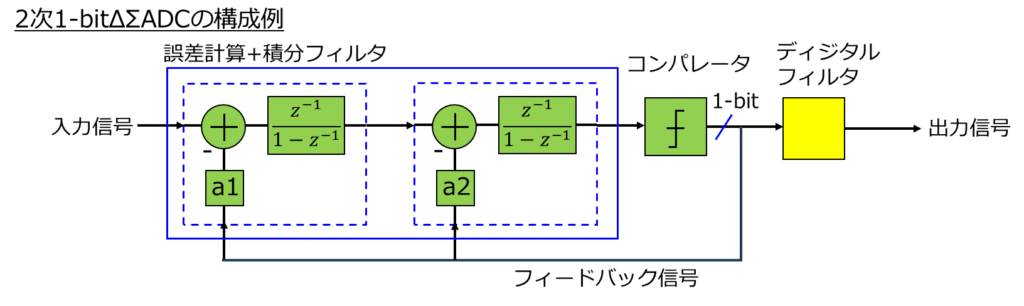

図 2次1-bit ΔΣADCの構成例

(積分器2段+1bit量子化器+ディジタルフィルタで構成される基本モデル)

1. 積分フィルタ(積分器)(Integrator)

積分器は、ΔΣADCのノイズシェーピングを生み出す中心要素です。

入力信号と、安定性を確保するためにa1,a2と重み付けされたフィードバック信号を蓄積し、その結果を次の段へ渡します。

上図にある「z^-1/(1-z^-1)」のブロックが積分器を表しており、ノイズシェーピングを行う次数に応じた数の積分器を搭載します。これが2段構成となると「2次のΔΣ変調器」になります。

積分器の段数(次数)を増やすほど帯域内ノイズは強く抑圧できますが、同時にループ不安定性も増すため、実用範囲は2〜4次が一般的です。

2. コンパレータ(量子化器)

積分器からのアナログ値は、コンパレータ(量子化器)で1bitディジタル値に変換されます。

ΔΣADCにおける量子化器は、

- アナログ値を1bit(0/1、または+1/−1)へ変換

- ここで発生する量子化ノイズをループで整形(ノイズシェーピング)

という2つの役割を担います。

構造が単純でばらつきにも強いため、多くのΔΣADCは1bit量子化を採用しますが、高性能用途では2bit〜3bitの量子化器を使う構成もあります。

3. ディジタルフィルタ

コンパレータ(量子化器)からは高速の1bitデータ列が出力されますが、

このデータは帯域外ノイズを多く含んでおり、そのままでは利用できません。

そこで、ディジタルフィルタが以下の処理を行います:

- LPF(ローパスフィルタ):高周波ノイズを除去

- Decimation(デシメーション):サンプリング周波数を下げ、信号帯域だけを抽出

ディジタルフィルタの形式としては、CICフィルタやCIC + FIRフィルタの組み合わせがよく使われ、

性能とハードウェア効率のバランスが取れる構成になっています。

このように、ΔΣADCは、

- 積分器:ノイズを整形する中心要素

- コンパレータ:アナログを1bit化

- ディジタルフィルタ:帯域外ノイズを除去し高精度データを生成

という3つの要素が一体となって、大きなフィードバックループを持つ制御回路の一種として動作しています。

さて、次はΔΣ ADCのシステム設計についてご紹介します。

第5章 ΔΣADCのシステム設計

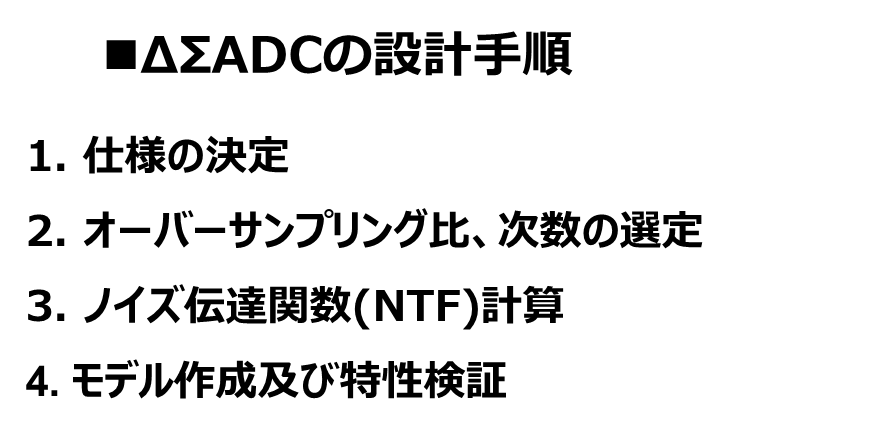

◆設計は“手順”がすべて

ΔΣADCの設計では、いきなり回路を作り始めると必ず行き詰まります。その理由は、ΔΣADCが「アナログ回路」「ディジタル処理」「制御理論」が混ざったシステム設計そのものだからです。

したがって最初に、全体構成を決めるための手順をしっかり踏む必要があります。

① 仕様の決定

ΔΣADCの設計で最初に決めるべきは、

最終的に必要となる 分解能、サンプリングレート、SNR、帯域幅(BW) といった基本仕様です。

ここで決まる数値が、後続の

- OSR(オーバーサンプリング比)

- 変調器の次数

- NTF(Noise Transfer Function)の形状 にすべて影響します。

仕様決めは「何bitが必要か?」だけではなく、

何Hz帯域が必要で、どの程度のノイズフロアを許容できるのかを含むため、アプリケーション要求と密接に結びついています。

② オーバーサンプリング比(OSR)・次数の選定

必要な分解能とSNRが決まったら、それを満たすためのOSR(オーバーサンプリング比) と 変調器の積分次数(1次〜4次) を選びます。

一般的には、

- OSRを上げるほどS/N比は改善しやすい

- 積分次数を上げるほど帯域内ノイズを強く抑圧できる(ノイズシェーピングが強くなる)

という関係があります。

ただし、OSRを極端に上げると消費電力やデジタル負荷が増え、次数を上げるとループ安定性が悪化するため、この2つは設計者が慎重にバランスを取る必要があります。(後で詳述します)

③ ノイズ伝達関数(NTF)計算

OSRと次数が決まったら、NTF(Noise Transfer Function:量子化ノイズがどのように通過するか) を設計します。

NTFの形が、ΔΣ変調器の

- 安定性

- 帯域内ノイズ量

- 雑音シェーピングの強さ

を決定づけます。

この段階では、シミュレーションツールや数学的解析を用いて安定で目的の性能を満たすNTFを求めることが重要となります。

④ モデル作成および特性検証(Modeling & Simulation)

NTFまで決まったら、ようやくシミュレータモデルを使い回路を動かす段階に進みます。

- Verilog-A

- MATLAB / Simulink

- Pythonモデリング

- スイッチトキャパシタ回路の抽象モデル

などのシミュレータを使い、ΔΣ変調器のモデルを作成します。

次章では、それぞれの工程(①〜④)を1章ずつ掘り下げて解説していきます。