今日から数回に分けてPLL、特に後半はInteger PLLについて詳しくお話ししたいと思います。

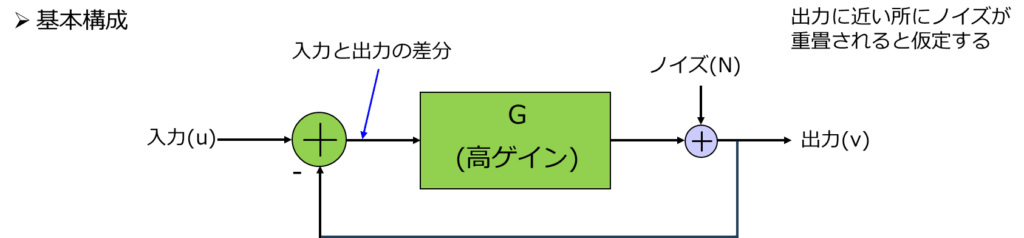

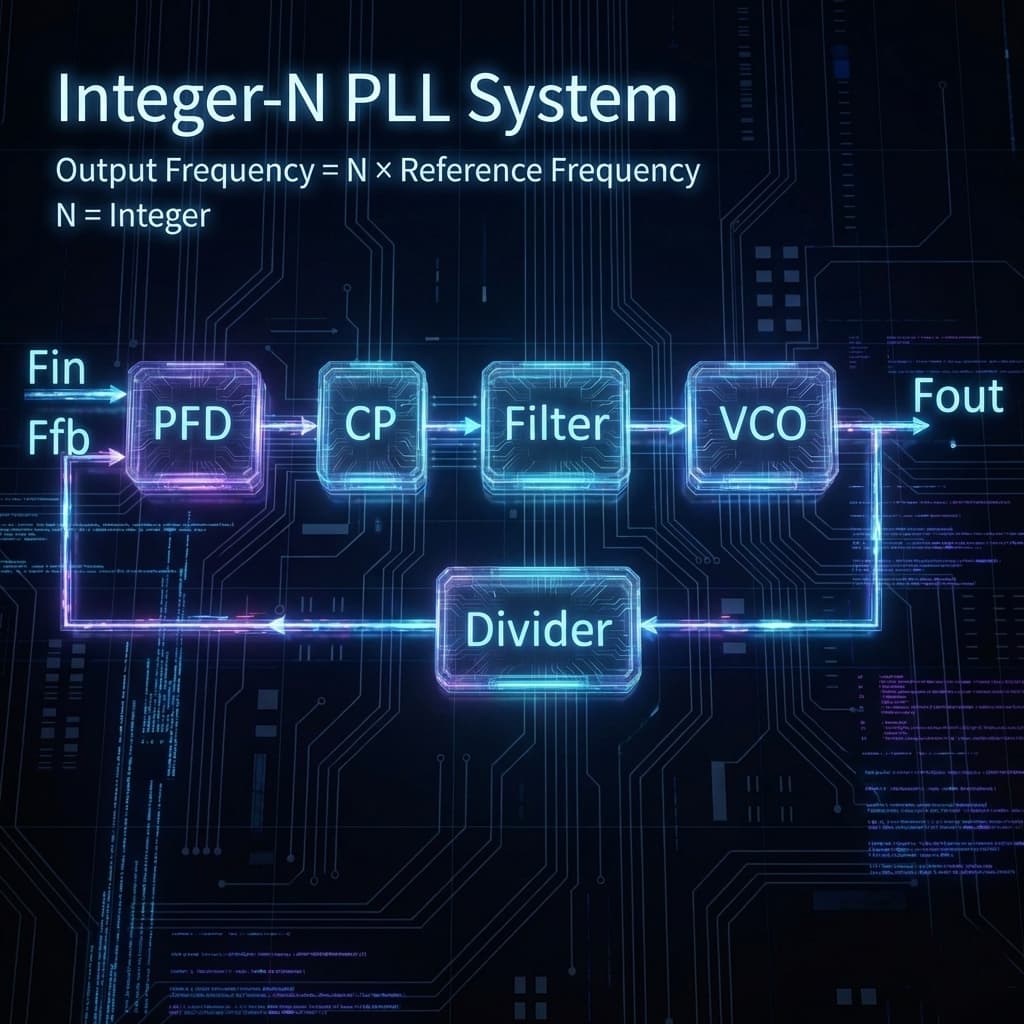

PLLは一言で言うと、基準となる信号の周波数や位相に自分の発振器を強制的に同期させる仕組みです。具体的には、「負帰還(ネガティブフィードバック)」と呼ばれる制御理論を応用したもので、入力信号(リファレンス)と出力信号のズレを検出し、その差分をゼロにするようにフィードバックをかけることで、極めて精度の高い同期を実現します。

言い換えると、「基準信号にぴったり合わせて動くための制御ループ」と言ってもいいかもしれません。つまり、外部からのリファレンス信号に対して、内部の発振器が常に「追従」し続ける「自動調整システム」の役割を担っています。

PLLの自動調整における重要なポイントは、大きく分けて次の3つです。

1. 基準信号の位相を常に監視する

一つ目として、位相(信号のタイミング)の僅かなズレをPFD(位相比較器)で検出し続けます。周波数のズレは位相のズレの積分として現れるため、位相を監視することが精密な制御の起点となります。この「常に目を光らせている」状態が、安定性の第一歩です。

2. 自分の発振器(VCO等)を調整して誤差をゼロに近づける

二つ目に、検出された位相差をチャージポンプやループフィルタを介して電圧信号に変換し、VCO(電圧制御発振器)の入力をコントロールします。この一連のプロセスにより、出力信号を基準信号へと引き込み、誤差を極限まで排除していきます。

3. 結果として安定した周波数・位相を得られる

これら1、2のプロセスを繰り返すことで、最終的には安定した周波数・位相を得ることができます。一度「ロック」状態に入れば、温度変化や電源電圧の変動といった外部からの乱れ(ディスターバンス)に対しても、ループの働きによってその影響を抑え込み、安定した出力を維持し続けることが可能です。

PLLがもたらすメリット

この「安定した周波数・位相を得られる」という結果は、LSIシステム全体にとって何が嬉しいのでしょうか? 具体的には、以下の3つの大きなメリットをもたらします。

1. 周波数を安定化出来る

水晶発振器のような極めて正確な基準信号の安定度を維持したまま、LSI内部で必要な高い周波数へと展開できます。これにより、外部環境に左右されない強固なシステムを構築できます。

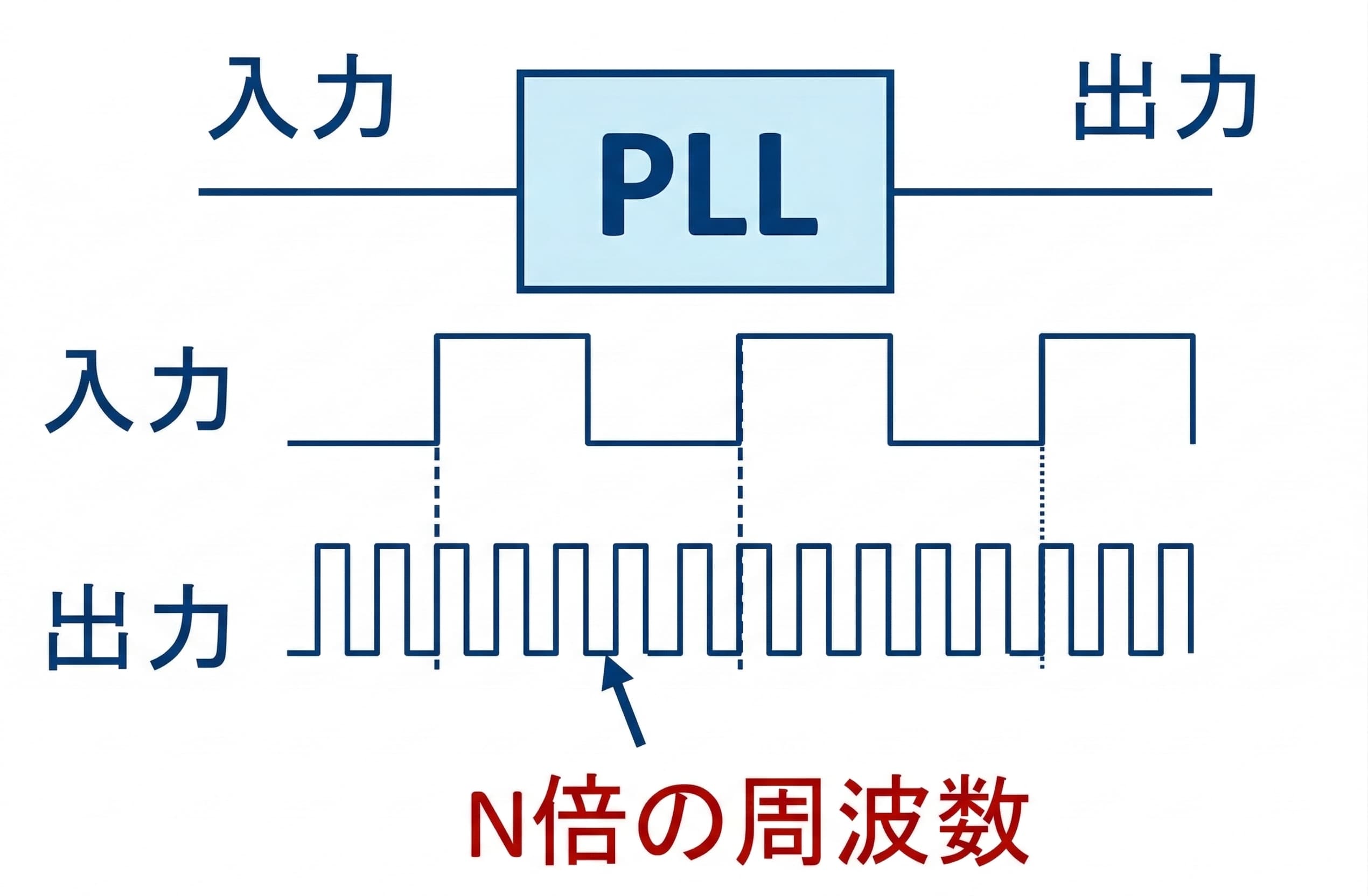

2. 周波数を変換(逓倍、分周)出来る

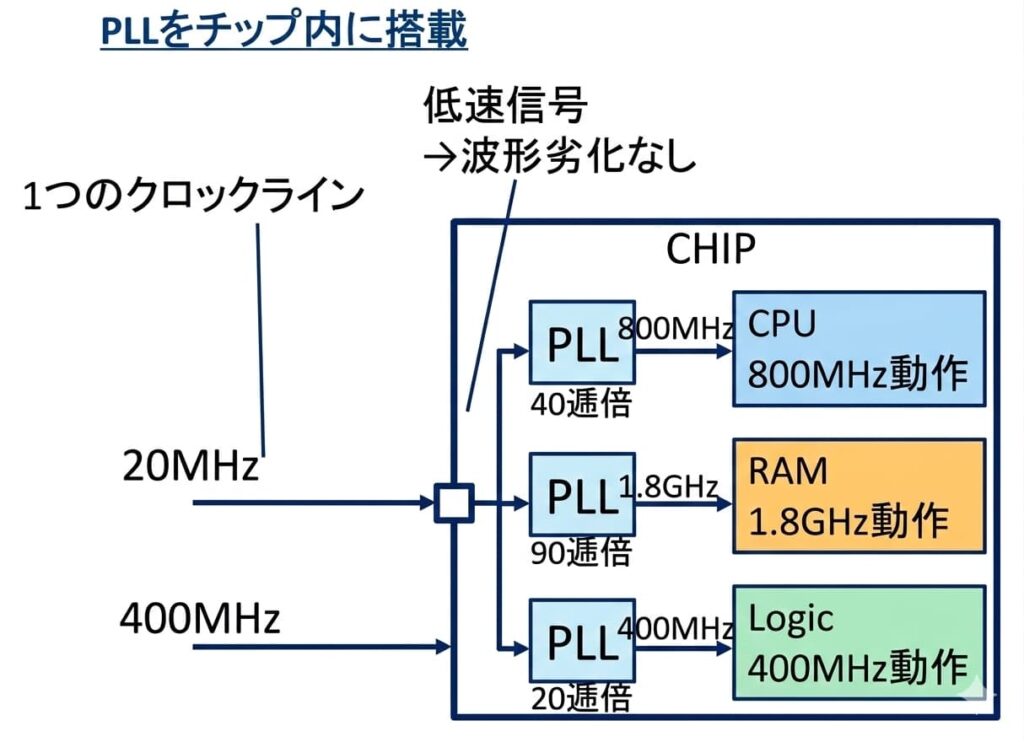

基準となるクロックから、そのN倍の周波数を作り出すことができます。これにより、一つの基準信号からLSI内部の各ブロックが必要とする様々な速度のクロックを自在に供給できる柔軟性が生まれます。

3. 通信で必要な同期(クロック再生等)が出来る

受信したデータ列から、データを取り込むための最適なタイミングを抽出する「クロックデータリカバリ(CDR)」のような役割を果たします。これにより、高速かつ正確なデータのやり取りが可能になります。

PLLは、現代のシステムLSIには必要不可欠な重要機能ブロックです。まさに回路の「心臓部」として、すべての動作の基準を作り出しているのです。

PLLが無い世界を想像してみる

さて、ここまでPLLの基本的な仕組みについてお話ししてきましたが、「もしこの世にPLLが無かったら?」という視点で、その重要性をさらに深掘りしてみましょう。

実は、PLLという技術が確立されていなければ、現代のような便利な社会は実現していなかったと言っても過言ではありません。

スマホ等で自由に遠方と通信出来る時代は来なかった

まず、私たちの生活に欠かせないスマートフォンなどのモバイル通信についてです。PLLが無い世界では、スマホ等で自由に遠方と通信出来る時代は来なかったと考えられます。

具体的には、無線通信において周波数を極めて正確に制御・維持する技術が欠如することになります。周波数の管理が正確に出来ないため、電波のチャンネルを細かく分けることができず、混信が多発したり、そもそも遠くまで安定してデータを飛ばすことが困難になります。

もしPLLが無ければ、無線通信の進歩は子供の頃に遊んだおもちゃのトランシーバぐらいだったかもしれません。私たちが当たり前のように使っている「どこでもつながる高速通信」は、PLLによる精密な周波数同期があって初めて成り立っているのです。

PLLが無いと、コンピュータの進化も止まっていた?

PLLが無いことによる影響は、通信分野だけに留まりません。私たちの仕事や生活を支えるパートナーである「PC(コンピュータ)」も、その姿は今とは全く異なるものになっていたはずです。

結論から申し上げますと、PLLが無ければ、PCも小型化、高速化に出来なかったと考えられます。

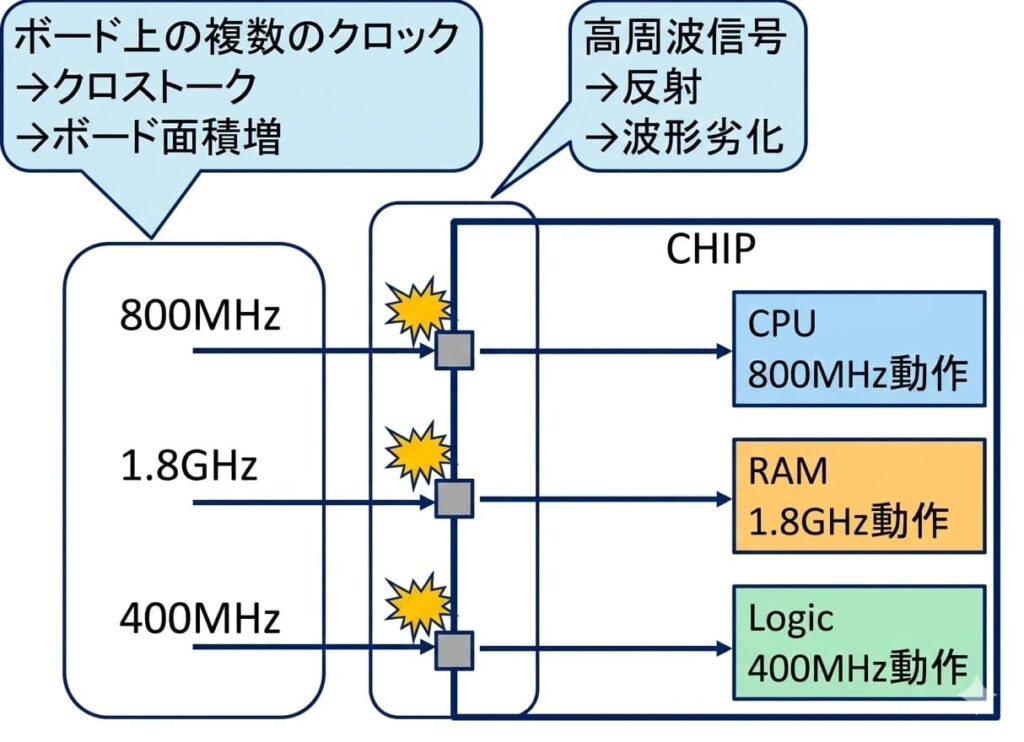

CPU外部に高速クロック源が多数必要になる

現代のコンピュータ、特にその心臓部であるCPUは、GHz(ギガヘルツ)級の極めて高速なクロック信号で動作しています。通常、LSI内部ではPLLを用いることで、低速で安定した基準クロックからこの高速な動作クロックを作り出しています(逓倍機能)。

もしPLLが使えないとなると、どうなるでしょうか。 高い周波数を内部で生成できないため、CPU外部に高速クロック源が多数必要となります。基板上には巨大な水晶発振器や、高速信号を供給するための複雑な配線が溢れかえることになります。

その結果、マザーボードは巨大化し、消費電力も増大、信号の干渉問題も深刻化します。私たちが今手にしている薄型のノートPCや、ポケットに入る高性能なスマートフォンといったデバイスは、物理的に実現不可能だったでしょう。

現在のLSIはPLLの恩恵を多大に受けていると言えます。 普段その存在を意識することはほとんどありませんが、高速通信ができるのも、PCがサクサク動くのも、デバイスが驚くほど小型化されているのも、すべてはPLLという「縁の下の力持ち」が正確なリズムを刻み続けてくれているおかげなのです。

PLLの種類:Integer-NとFractional-N

PLLには、周波数をどのように作り出すかによって、大きく分けて2つの主要な方式があります。それが「整数分周(Integer-N)」と「小数分周(Fractional-N)」です。それぞれの特徴と使い分けについて解説します。

整数分周PLL(Integer-N PLL)

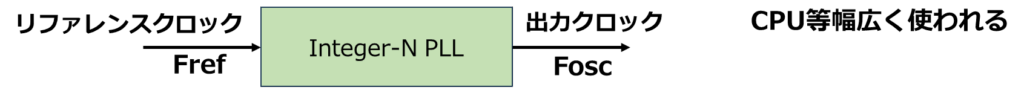

一つ目は、今回のメインテーマである整数分周PLLです。

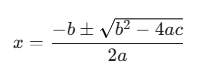

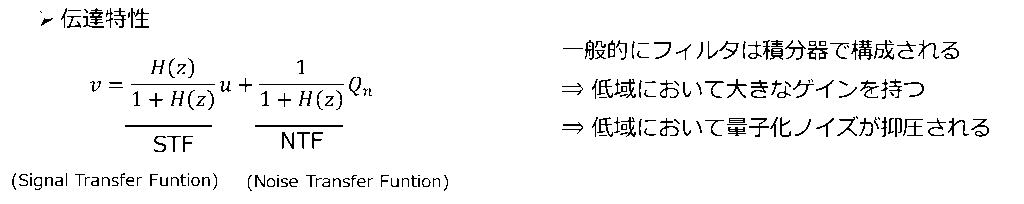

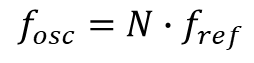

これは、リファレンス信号周波数の「N倍(N:整数)」の周波数を持つクロックを生成する方式です。周波数分解能は数M~数十MHz。クロック周波数の関係は、以下のシンプルな式で表されます。

この方式は、仕組みが単純で安定性が高く、主にCPUやデジタル回路のシステムクロック生成などで幅広く使われています。リファレンスの整数倍という決まったステップで動作するため、信頼性が求められる演算処理の同期に非常に適しています。

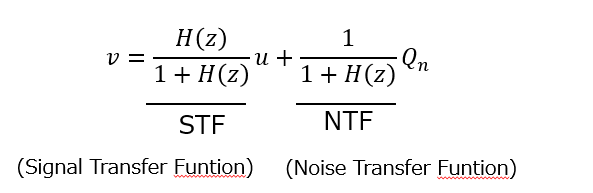

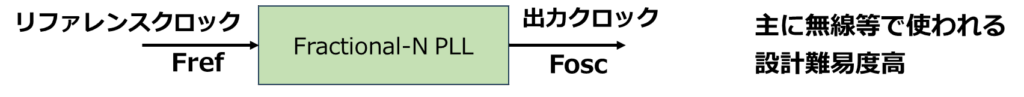

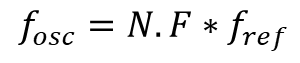

小数分周PLL(Fractional-N PLL)

二つ目は、より高度な制御を行う小数分周PLLです。

こちらは、リファレンス信号の「N.F倍(F:小数)」の周波数を作り出すことができます。周波数分解能は数Hz。関係式は以下のようになります。

この方式は、主に無線通信の分野などで真価を発揮します。無線通信では、限られた電波の帯域の中で極めて細かくチャンネル(周波数)を切り替える必要があるため、整数ステップよりも緻密な周波数設定ができるFractional-N方式が不可欠なのです。

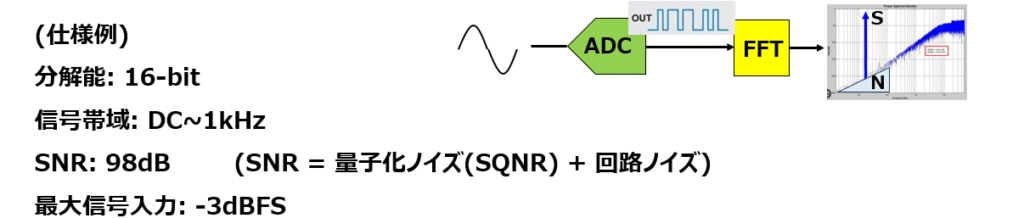

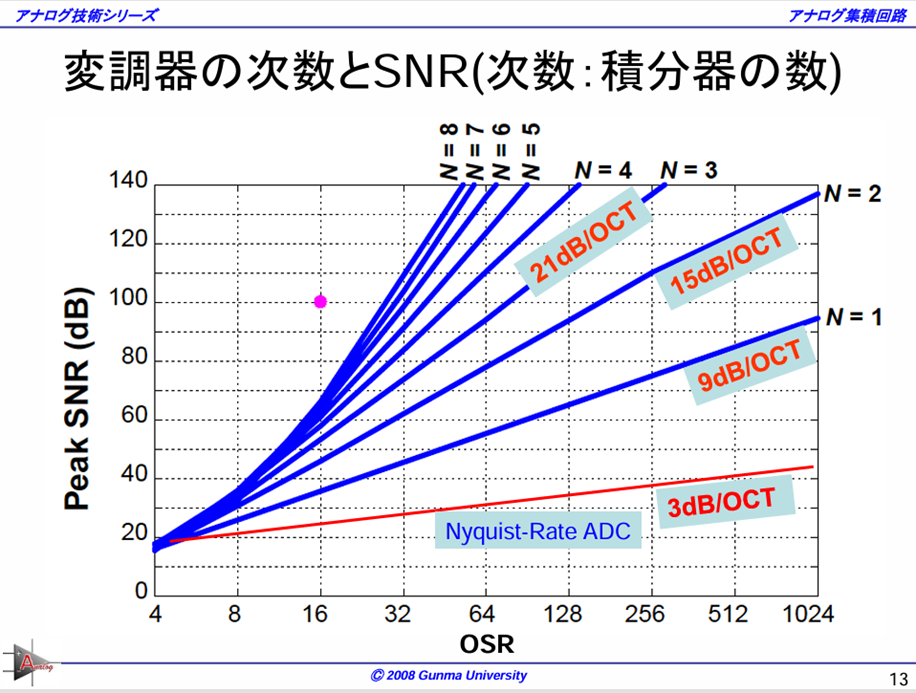

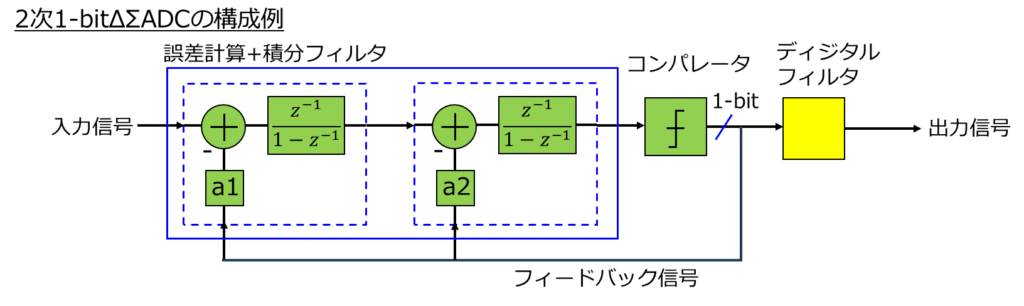

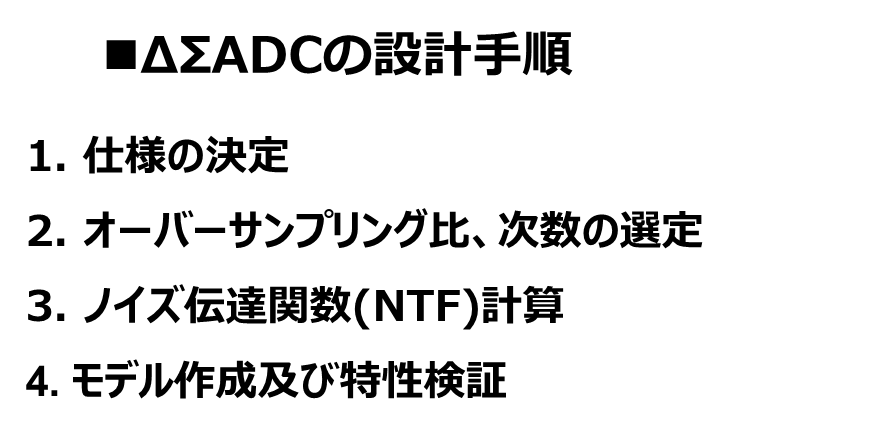

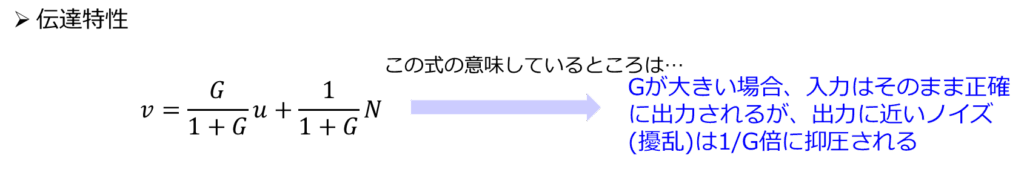

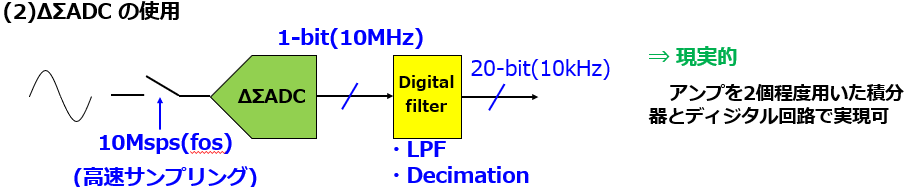

小数分周PLLはInteger-N PLLより設計が難しいとされています。それは、分周比を小数レベルで細かく動かす際に特有のノイズが発生するためです。これを抑え込むためには、ΔΣ(デルタ・シグマ)変調器を用いたデジタル制御や、より緻密なループフィルタの設計が求められます。

少し長くなりましたので、今日はここまでとします。次回は、整数分周PLL(Integer-N PLL)の仕組みについて、もう少し詳しくお話させていただきます。

参考文献:群馬大 元澤 篤史 先生「PLL設計の基礎」 https://kobaweb.ei.st.gunma-u.ac.jp/lecture/20190723_motozawa.pdf