前回は、DAA技術のIPCにおける活用事例について2つご紹介しました。今回は残る3つ目の環境モニタを使った補正についてご紹介します。

Case3:環境モニタを使った補正

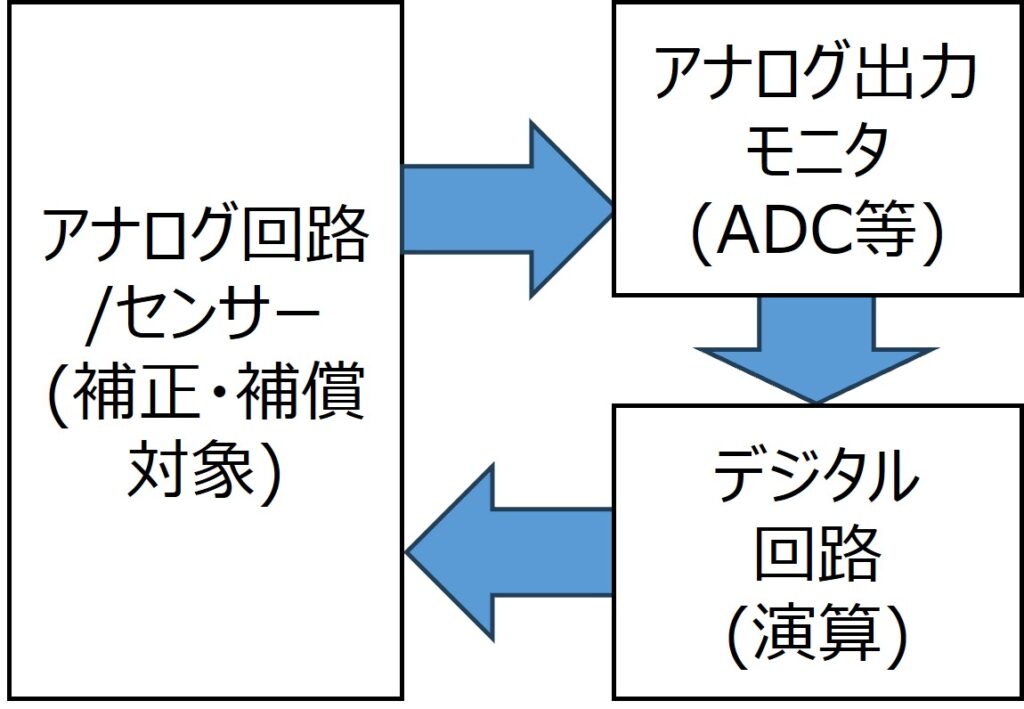

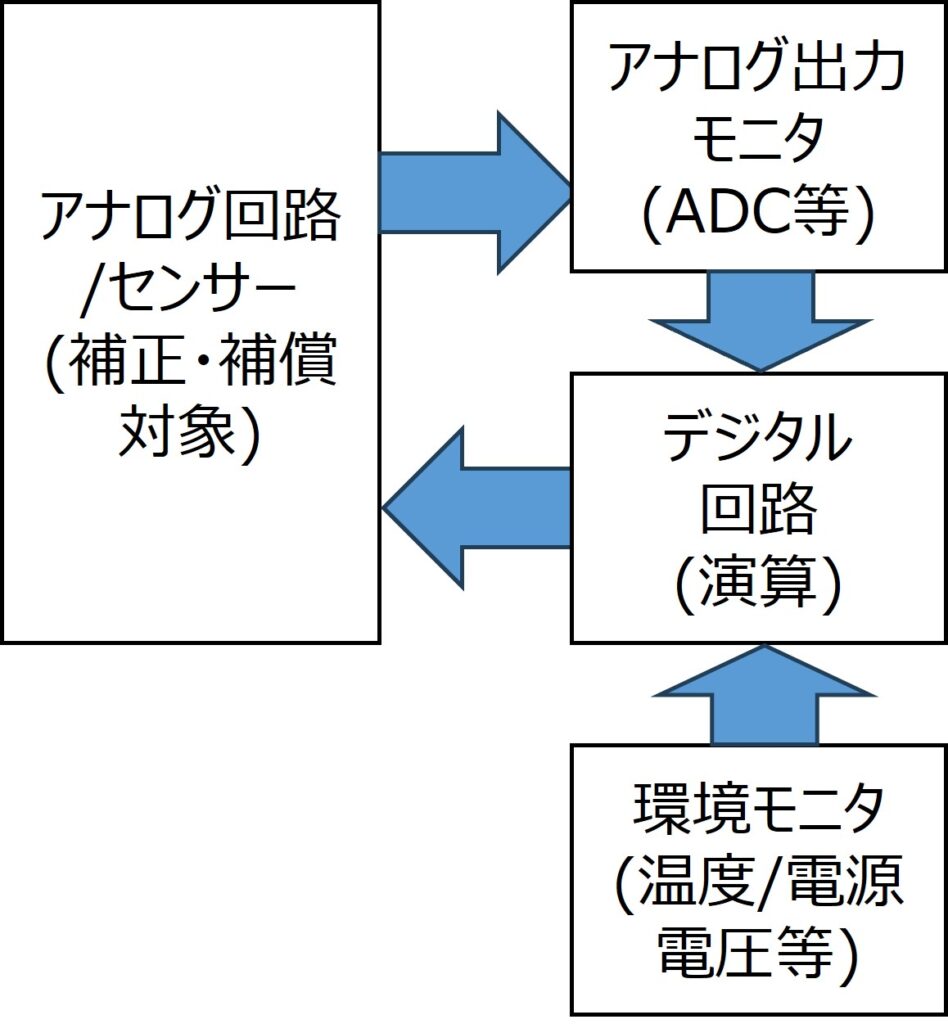

最後は、温度や電源電圧といった外部環境に応じて補正する方式です。温度センサーなどの環境モニタから得られた値をもとに補正演算を行い、アナログ回路に反映させることで、温度や電源条件が変わっても安定した測定や制御が可能になります。

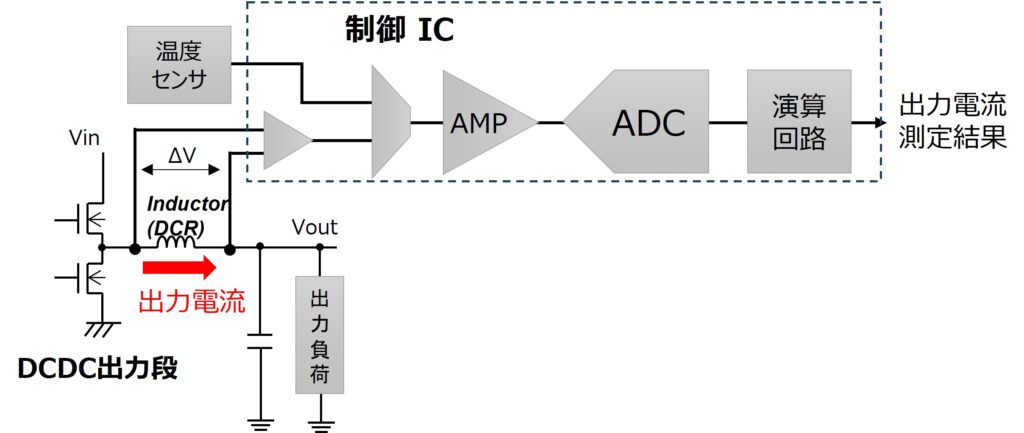

IPCにおける出力電流のセンシング

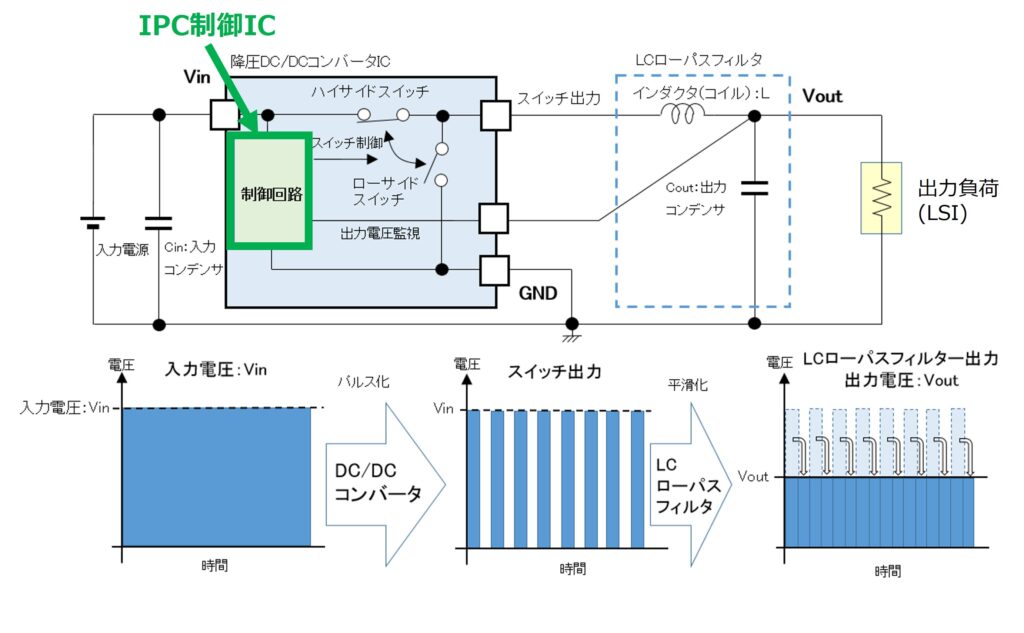

DCDCコンバータにおいて、出力電流を正しく測定することは過電流保護や効率管理のために欠かせません。IPCでは出力電流をインダクタ両端の電圧差(ΔV)を利用して測定する方法を使っています。インダクタには寄生抵抗(DCR)があり、この抵抗値を使って「 出力電流 = ΔV / DCR[Ω] 」を求める仕組みです。

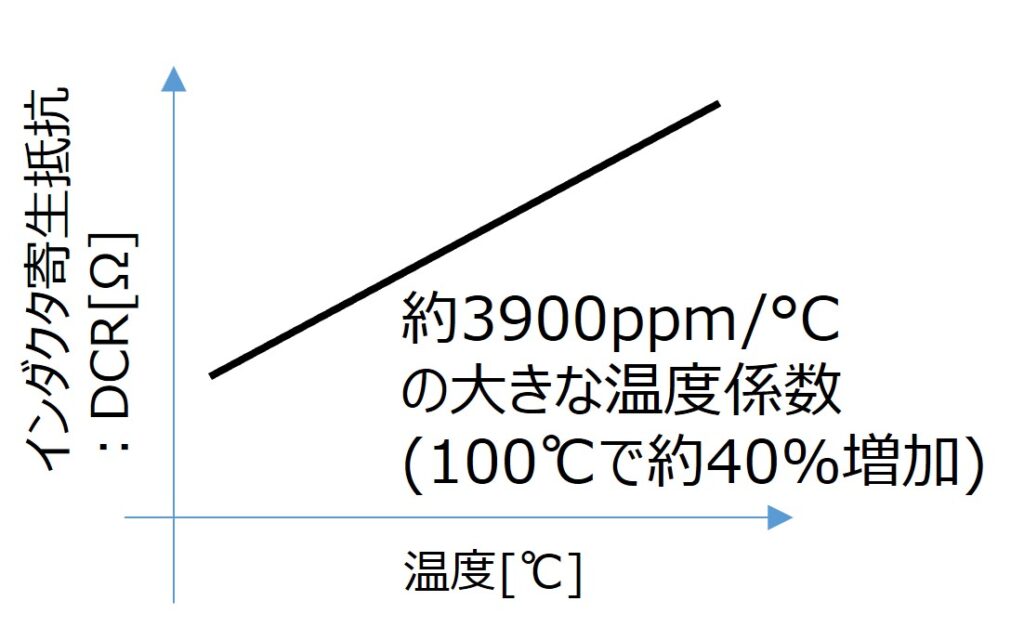

ところが、このDCRには大きな問題があります。温度依存性が非常に大きいのです。およそ3900ppm/℃ という温度係数を持ち、100℃の温度変化に対して、DCRは約40%も値が増加してしまいます。そのため、ΔVだけを使った電流検出では、正確な出力電流を得ることができません。

IPCでは、この課題を解決するために 温度補正機能を組み込んだDAAを採用しています。高温障害の検出用にモニタした温度測定値を使ってDCRを演算補正しその結果を基に電流を再計算します。

DCR(補正後)=DCR(27℃)×(1+3900ppm×(測定温度−27℃))

このインダクタのDCRを用いた方式の大きな利点は、素子追加が不要 である点です。一般的にはDCRの代わりに温度変化が小さい専用の検出抵抗を追加して電流を測定する方法も考えられます。しかしながら検出抵抗で余分な電力が消費されるためDCDCコンバータの変換効率が下がり、さらに部品コストや設置面積も増加してしまいます。IPCはインダクタ自体をセンサーとして活用し、追加素子なしで高精度な測定を実現していることで精度・コスト・変換効率の点でメリットがあります。

まとめ

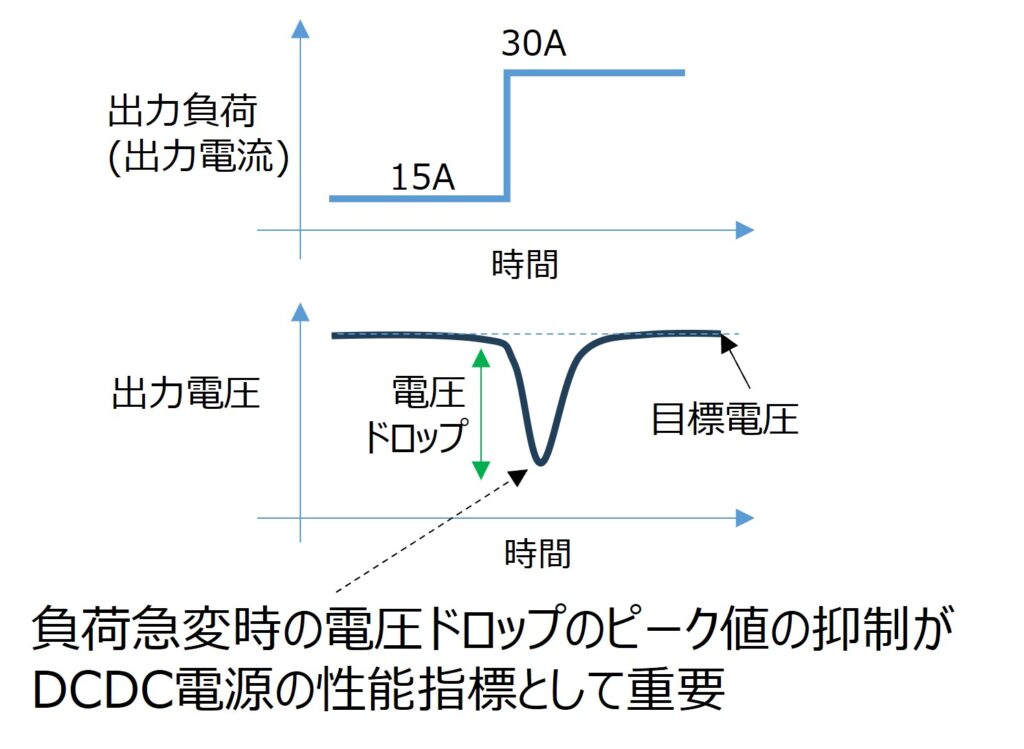

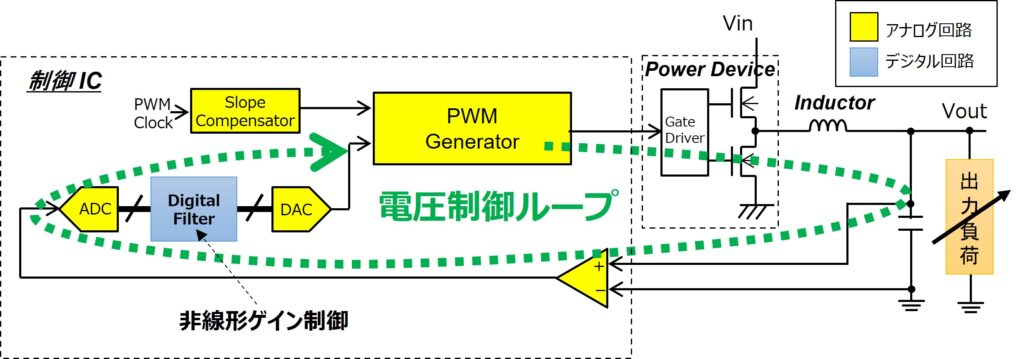

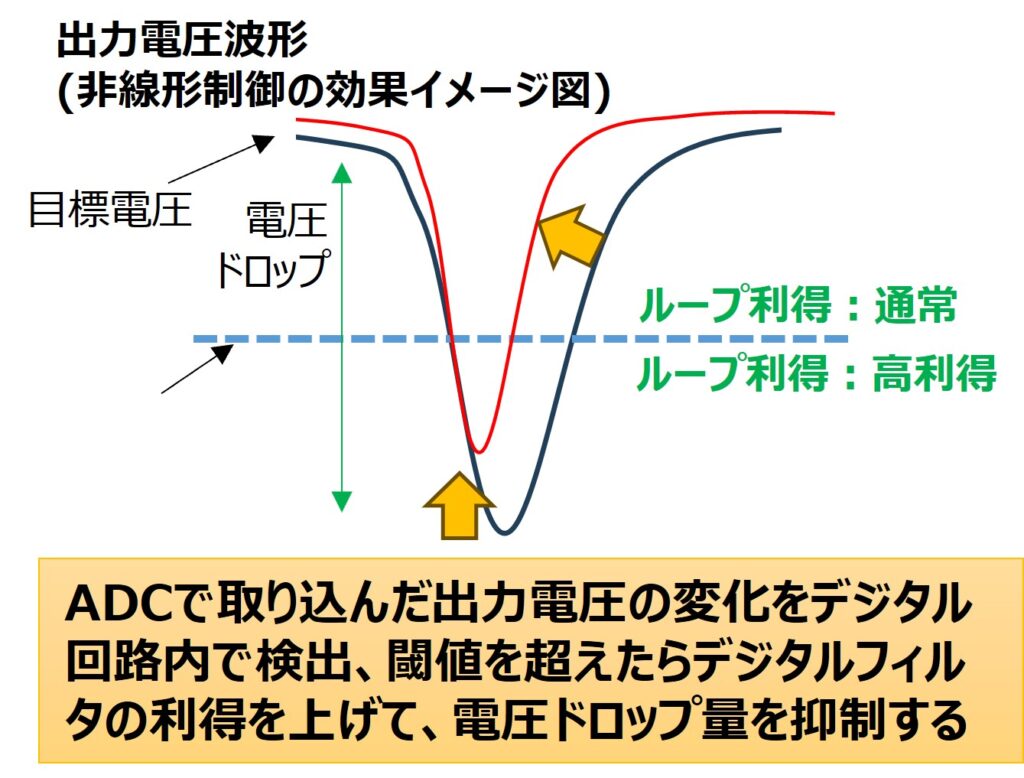

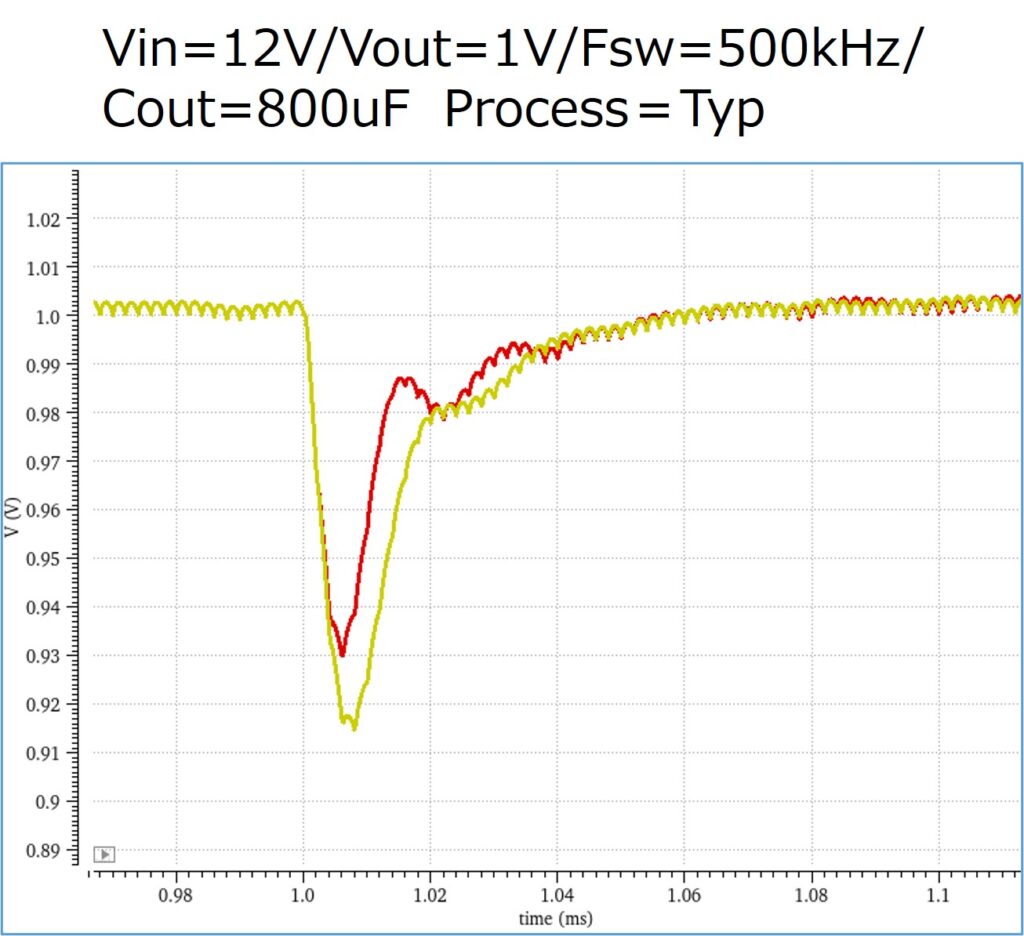

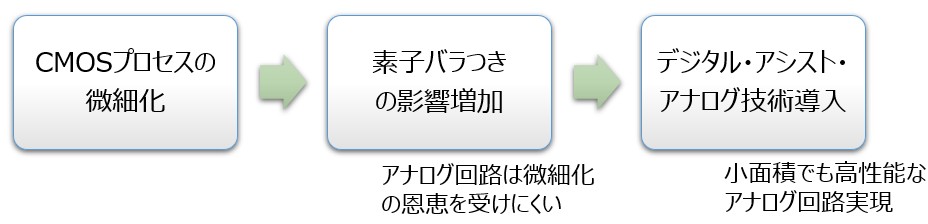

IPCは、DAA技術を活用することで、従来のDCDCコンバータでは難しかった負荷急変への応答性や制御精度を向上させています。さらに、製造ばらつきや温度変化への補正を柔軟に行い、高効率かつ高信頼な電源供給を実現しています。これらの技術は、AIサーバや車載機器など、厳しい電源条件が求められる用途において、電源設計の高度化に貢献するものと考えています。

IPCは「合わせミソ」を生かした取り組み

さて今回は、IPCプロジェクトの取り組みについて紹介し、その中で活用されている デジタル・アシスト・アナログ(DAA)技術 の事例を取り上げました。

新しい発想を生み出していくために、異分野の技術を持ち寄りエンジニア同志がひざを突き合わせて議論する手法を私たちは「合わせミソ」と呼んでいるのですが、こうした経験と工夫を掛け合わせて未来の半導体開発につなげていく姿勢がこのIPCの開発では色濃く表れていると感じます。

今回ご覧いただいたアナログとデジタルの組み合わせには決まった形がなく、過去のやり方に縛られない自由な発想が可能です。だからこそ、用途や課題に応じた最適なアプローチを柔軟に選び取ることができる、そこが醍醐味だと思います。

少しでもみなさんの開発テーマの参考にしていただけたら嬉しく思います。

<参考文献>

◆第13回 デジタル・アシスト・アナログ技術(その1):アナログICの基礎の基礎 – EDN Japan (itmedia.co.jp)