PLLとは「時間を扱う事」

僕はPLLの特徴は”時間を扱う”ことだと思っています。

時間を扱うと言う事は・・・リミッタ(制限)が無いとも言えます。電圧や電流なら普通は電源が供給できる範囲を超えた状態にはならないので、上限/下限があります。しかし、時間には上限も下限もありませんし、制限をかけようも無いのです。

なので、周波数差や時間差などの時間を電圧に変換する位相比較器は、なにかタイムマシーンのような特別な回路の様に思えます。位相比較器の話は別に機会にすることにして、今回は”ジッタ”について触れてみたいと思います。

ジッタ

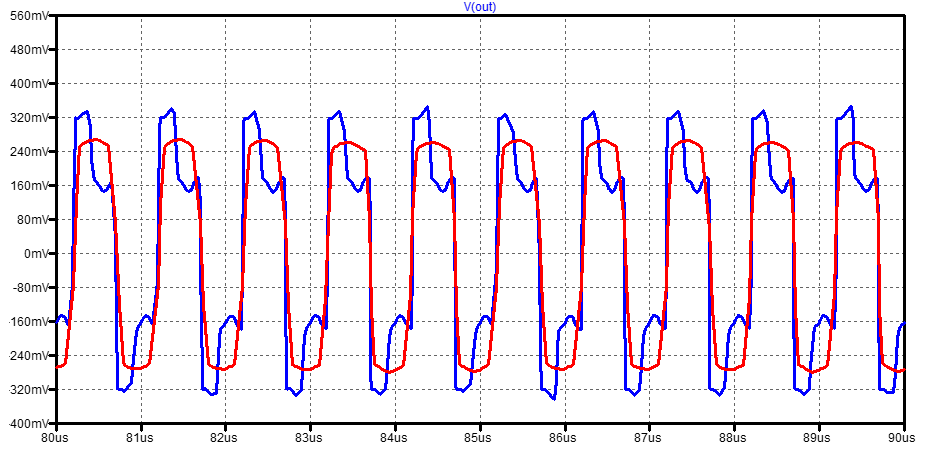

PLLを設計すると”ジッタ(Jitter)”と言う単語を必ず目にします。この単語の英語の意味は・・・”神経質に振る舞う、イライラする”です。ジッタはPLL回路の色々なトラブルの原因になる事が多いので、ジッタと聞くと神経質にもなるし、イライラもしますが、電気用語での意味は”時間軸の雑音”と考えて良いと思います。

例えば、1MHzの発振器は1usec毎に1周期を繰り返し正弦波やパルスを出力しますが、この周期が1.1usecに成ったり、0.95usecになったりと出力するたびに間隔が異なることが、ジッタです。ジッタは雑音なのでジッタが全く無い信号はこの世にはありえません・・・もしあるとすれば、世界標準時を決める原子時計のパルスはジッタが無い(と決めた)と言えます。

雑音が大きくなると問題が起きるのが世の常で、ジッタも大きくなると問題を引き起こします。

S/N設計をするのと同じように、ジッタもきちんと設計しないとトラブルが発生します。

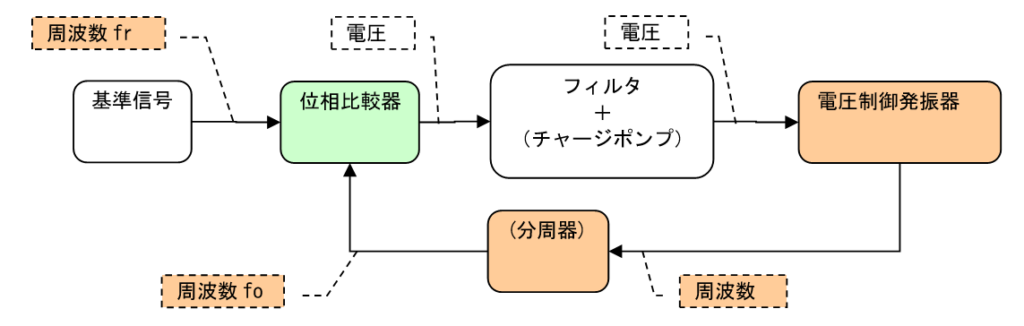

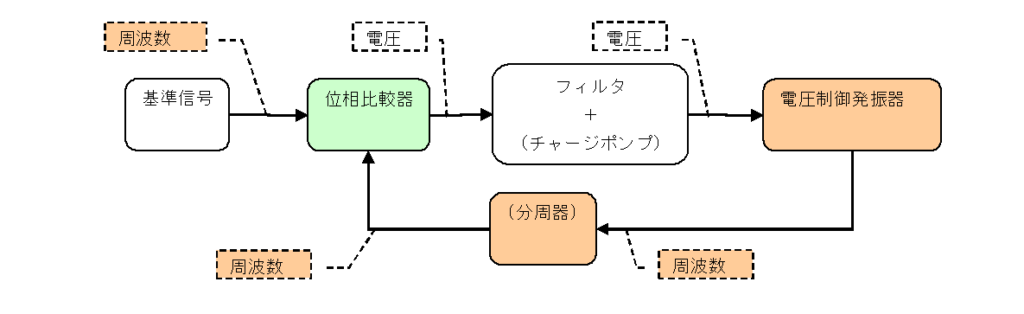

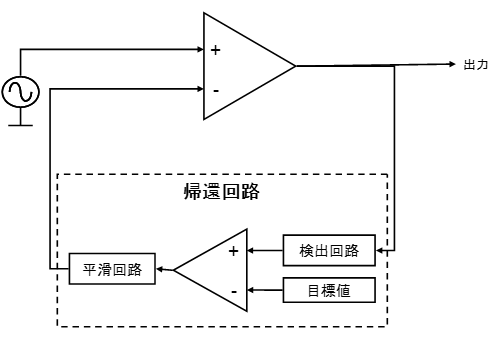

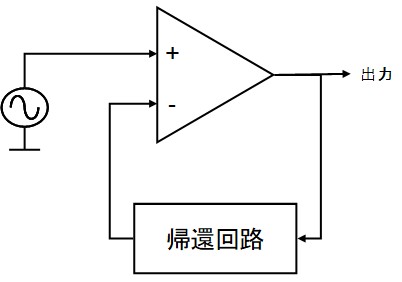

PLLのジッタに関連する機能は、大きく分けて2つに分かれます。それは、

(1)ジッタの少ないクロックを広い周波数帯で出力する事(シンセサイザー)

(2)ジッタだらけのクロックをきれいなクロックにして出力する事(ジッタクリーナー)

の2点だと思います。まずは、(1)についてです。

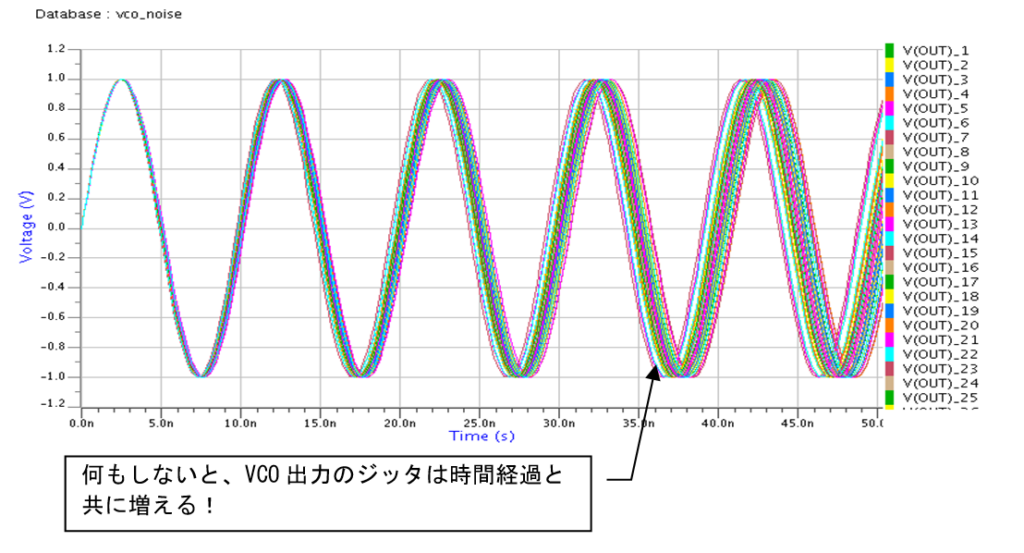

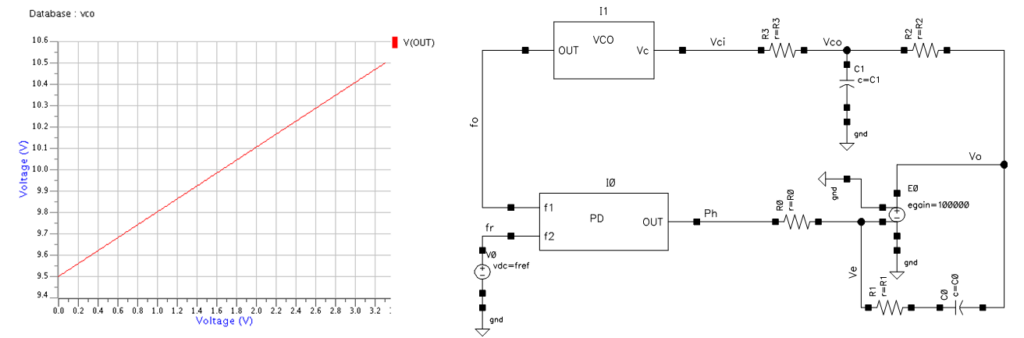

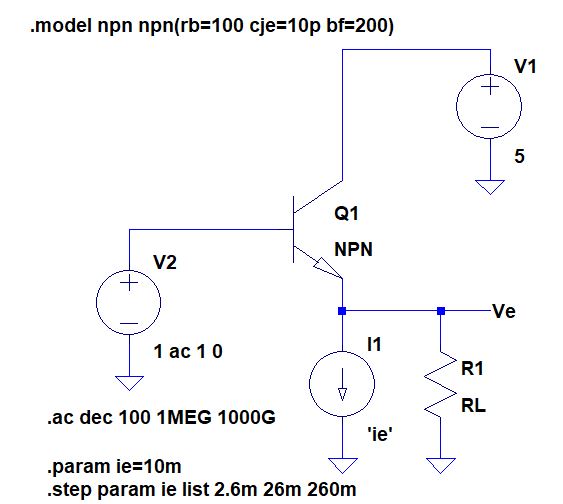

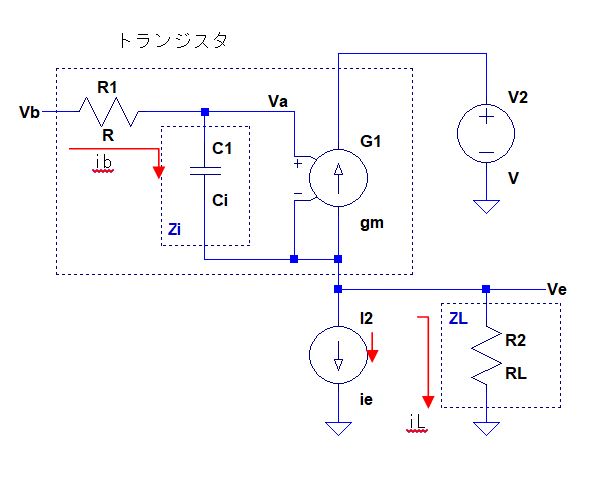

実は、PLLに不可欠な電圧制御発振器(VCO)は大きなジッタ源なのです。

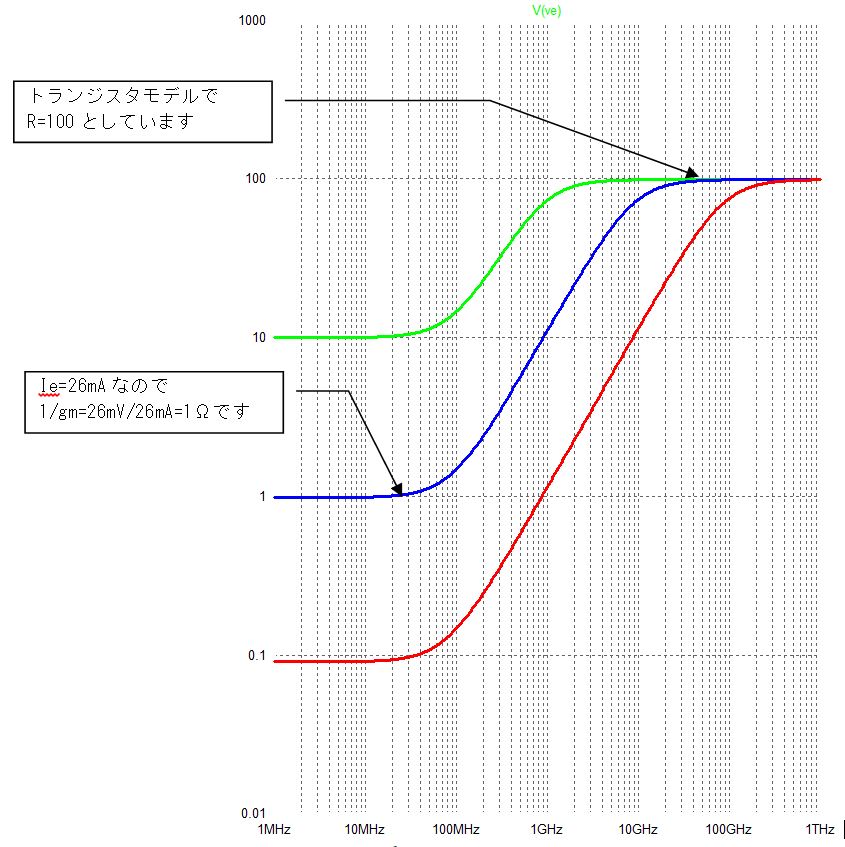

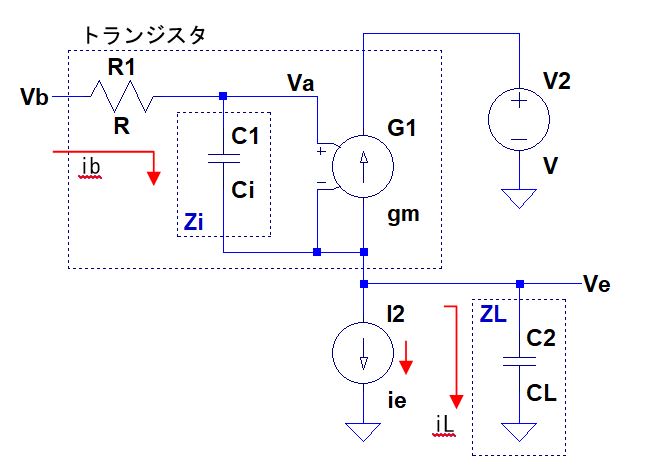

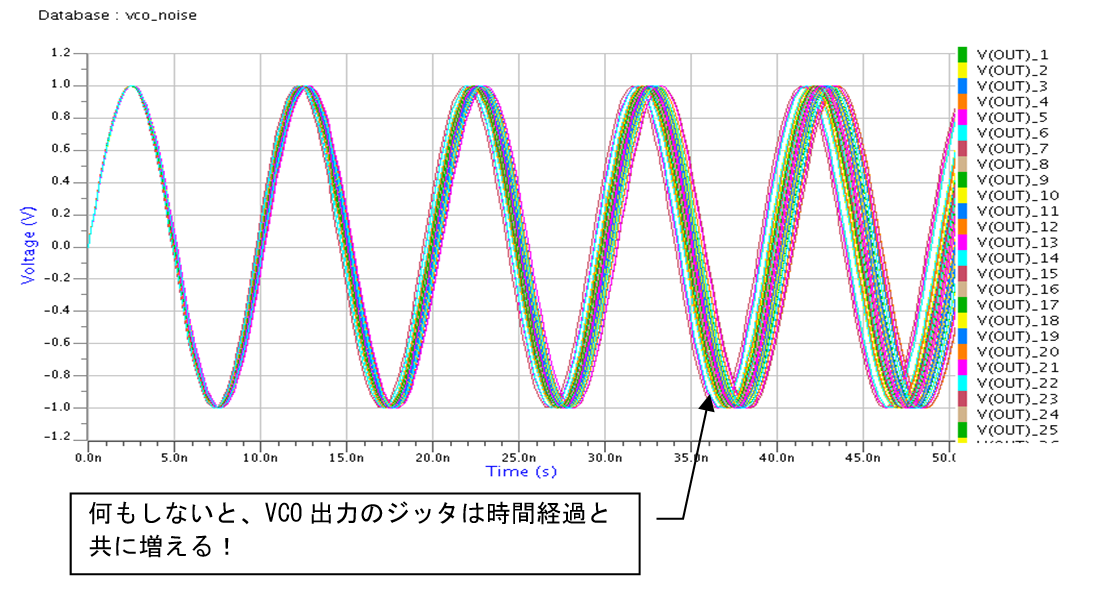

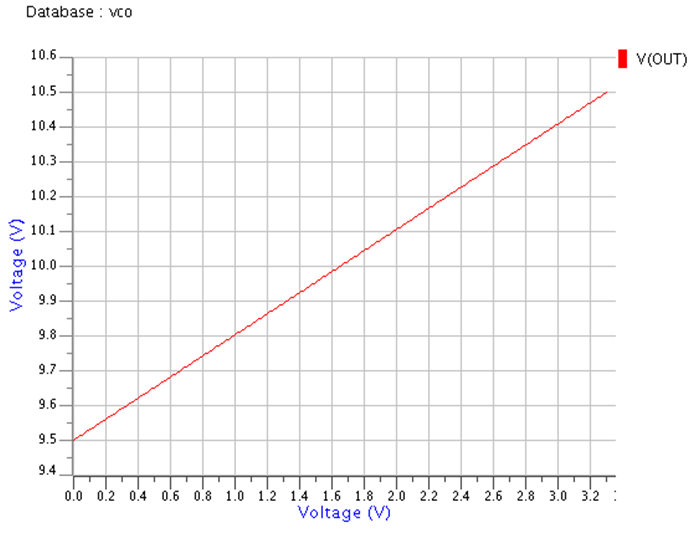

VCOの制御信号に雑音があれば、その雑音に応じて周波数が変化し、周波数が変化するということは周期が変わるのでジッタになります。制御信号に全く雑音が無くても発振器のトランジスタや抵抗などから様々な雑音が出ているので、これらが周波数に変換されてジッタになって出力されます。VCOの感度(電圧 => 周波数の変換効率)が高いほど出てくるジッタも多く、出来るだけ広い周波数範囲を一つのVCOでカバーしようとした時には、ジッタも多くなることを覚悟する必要があります。ジッタの大きな特徴は、ほっておくとどんどん増えるって事です。

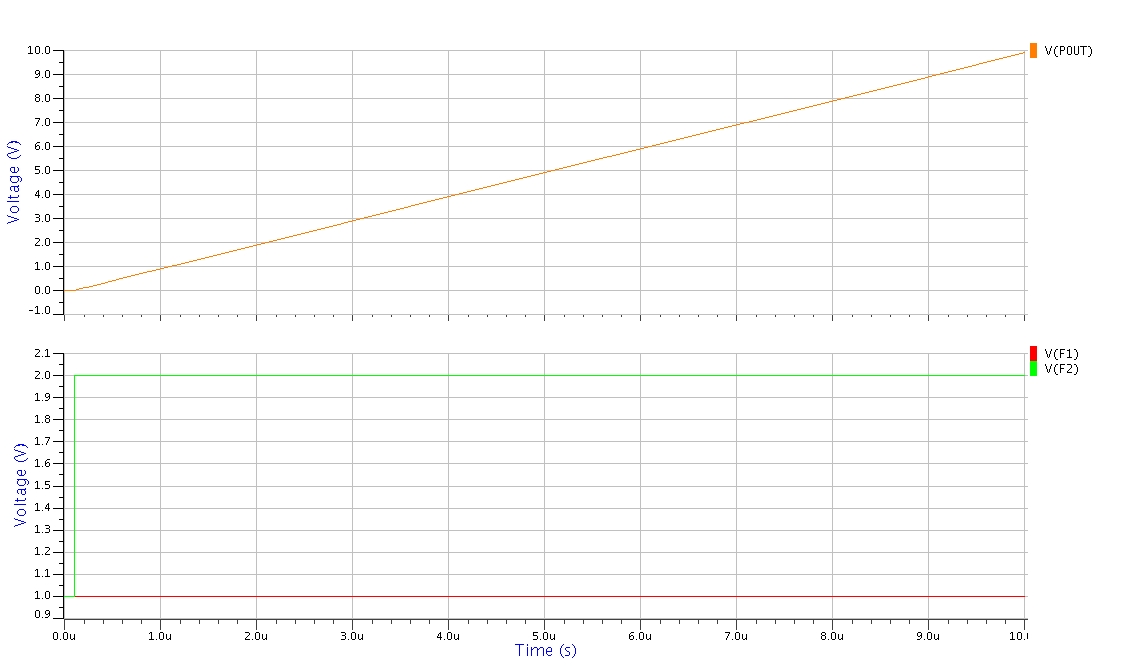

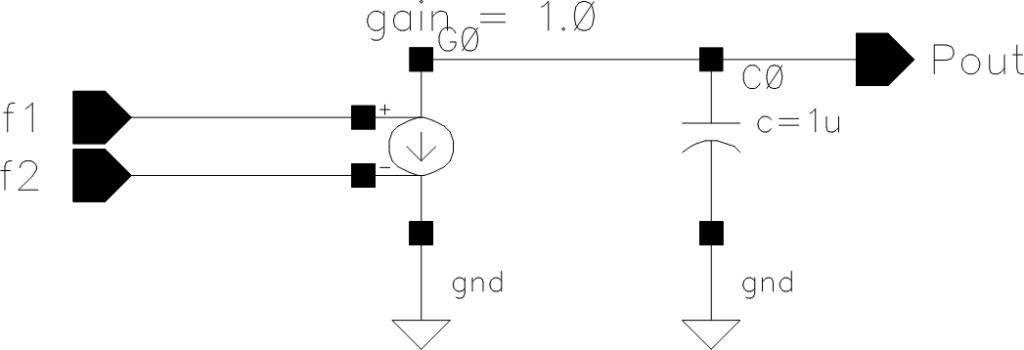

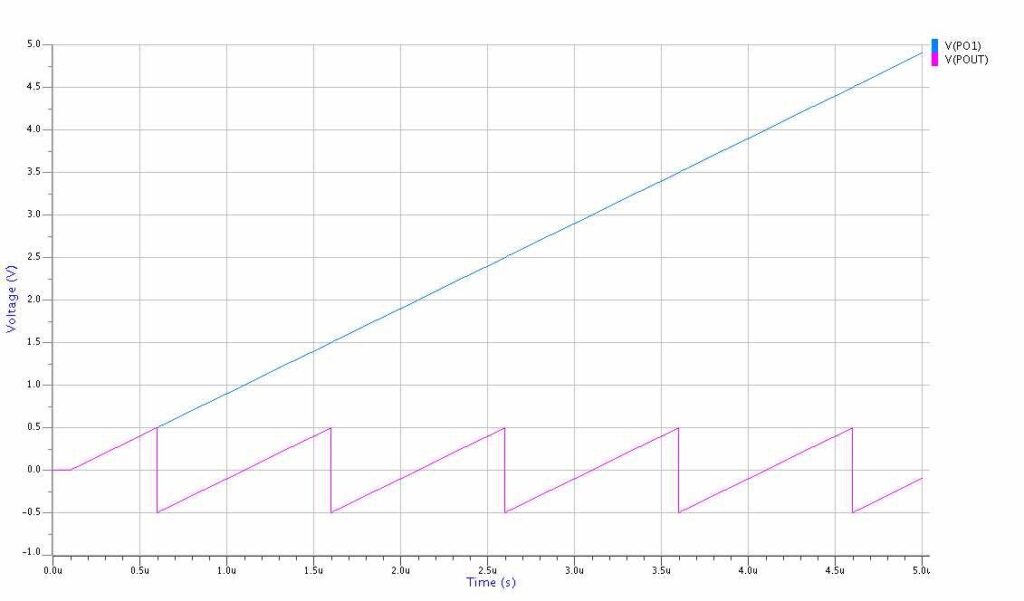

位相ずれ

例えば、周波数が1Hzずれた場合0.1sec後には36°ずれ、0.2sec後には72°位相がずれてしまいます。”周波数(差)を時間で積分すると位相(差)になる”ので、周波数がちょっとでもずれていると、時間経過と共に位相ずれ(つまりジッタ)が増加します。

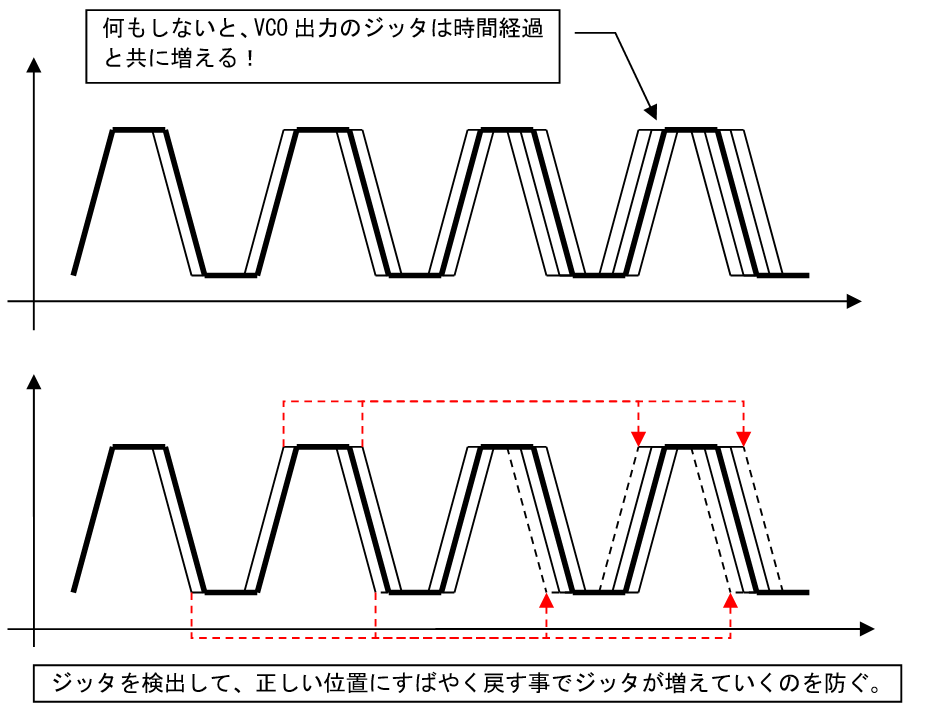

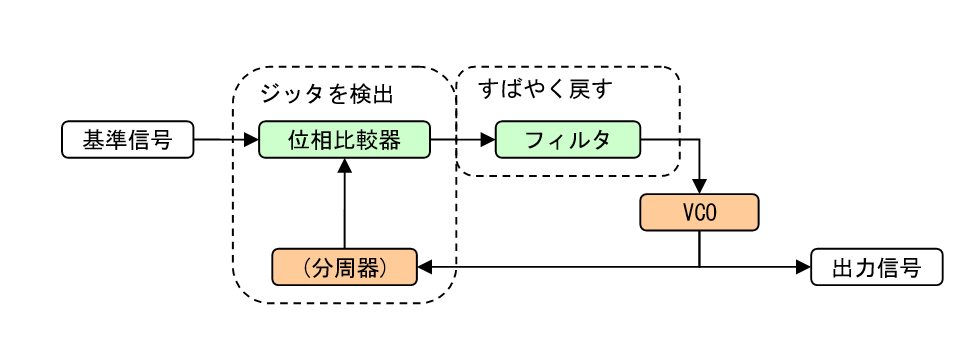

VCOのジッタを減らすには、ジッタを検出して”正しい位置”に”すばやく”戻す必要があります。

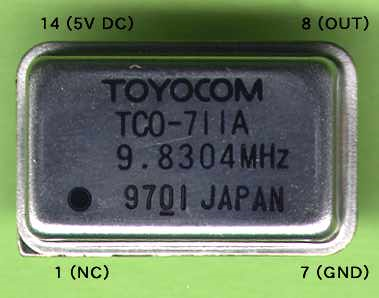

“正しい位置”は基準信号としてPLLに入力されます。これに使うのが水晶を使ったVCXOです。

VCXO

この発振器は水晶に電圧をかけて固有振動数を取り出しているため、非常に周波数が安定していてジッタが少ないです。しかし、周波数の可変範囲が狭いため色んな周波数では使えません。

ジッタの補正

このジッタの少ないVCXOを基準としてPLL回路を構成し、VCOのジッタを補正すれば、広い周波数範囲でジッタの少ない信号を取り出すことが出来るようになります。

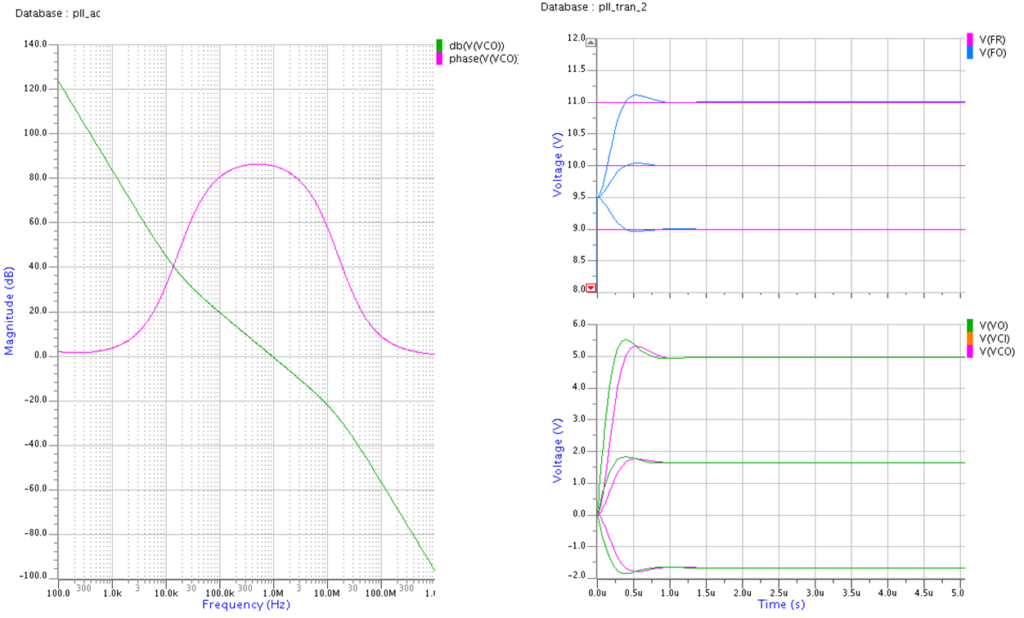

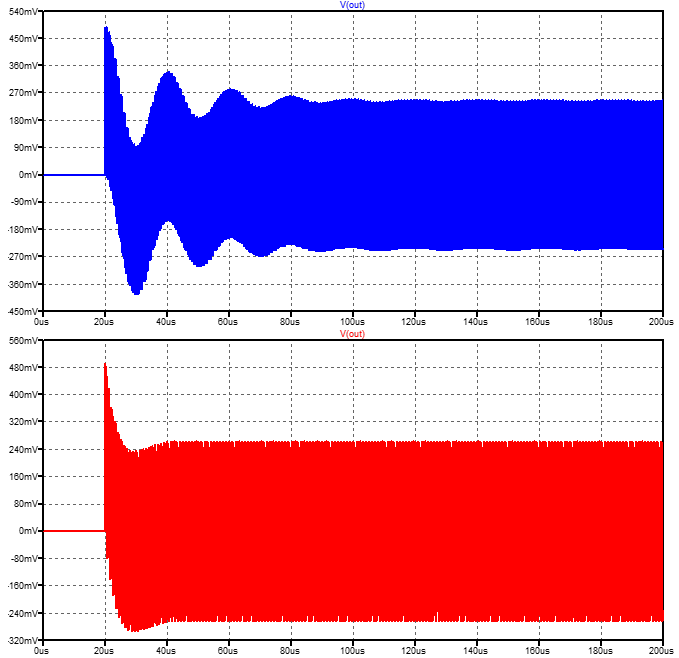

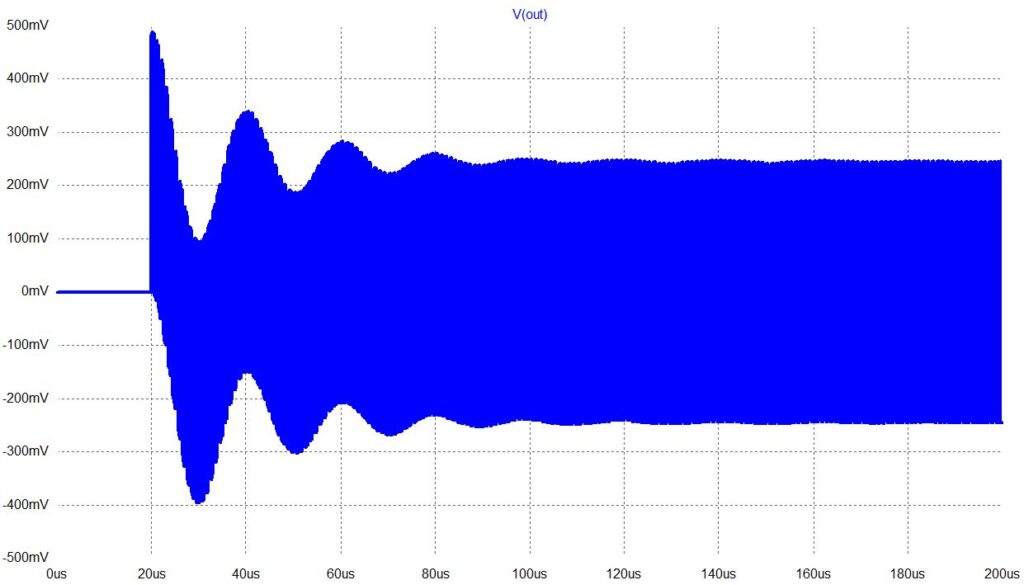

“すばやく”戻すにはPLLの応答速度を早くする必要があります。

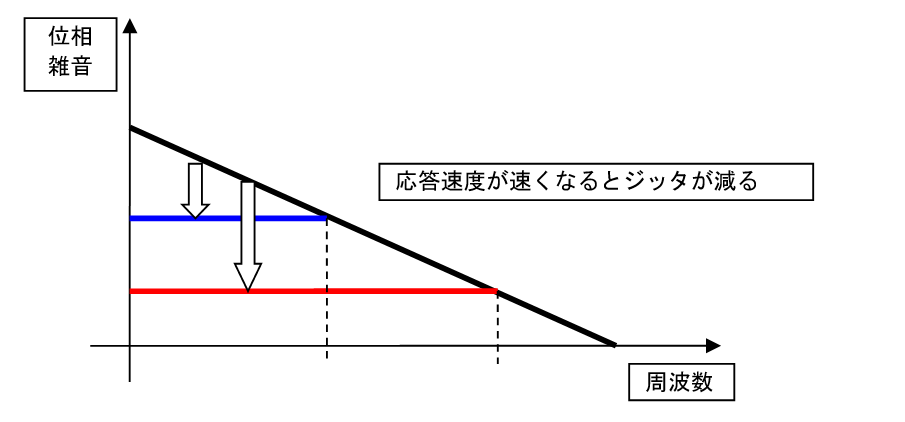

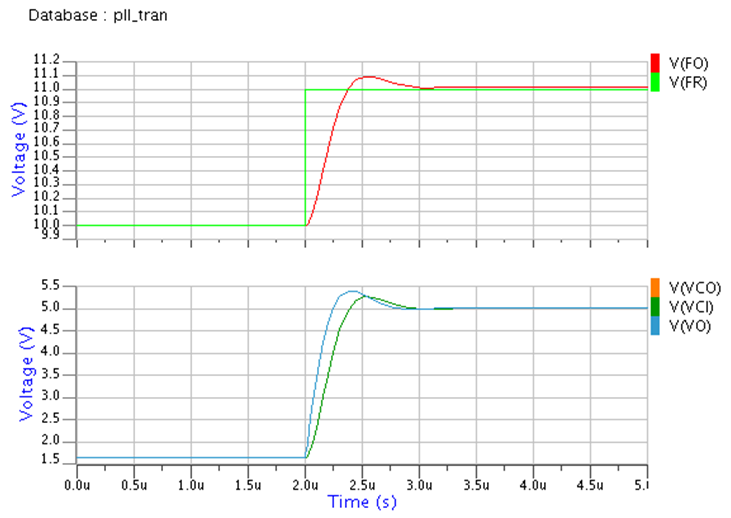

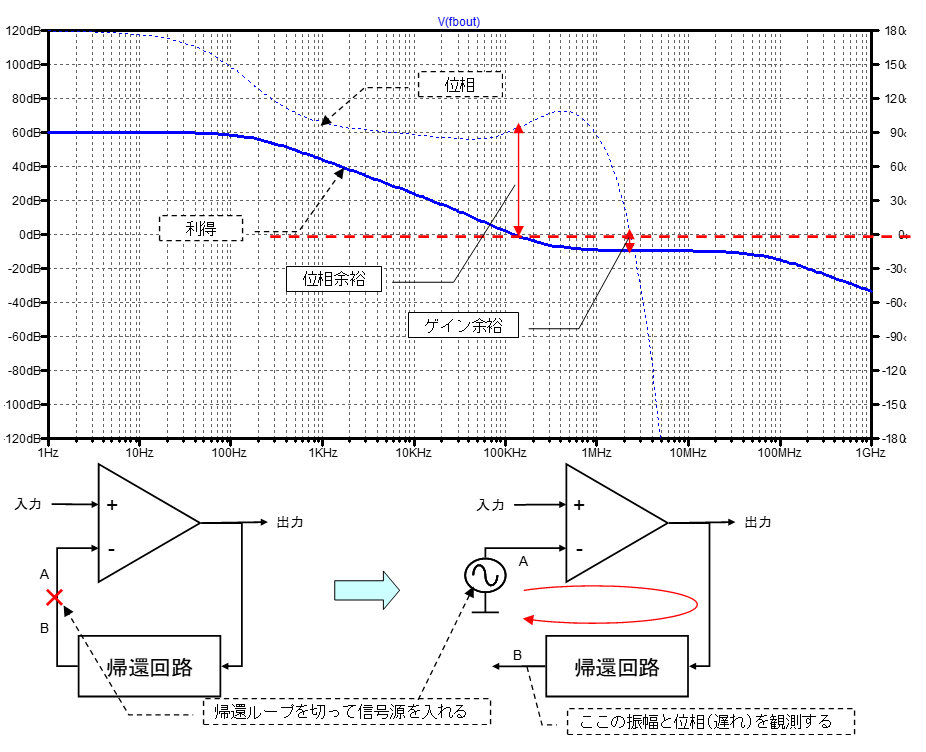

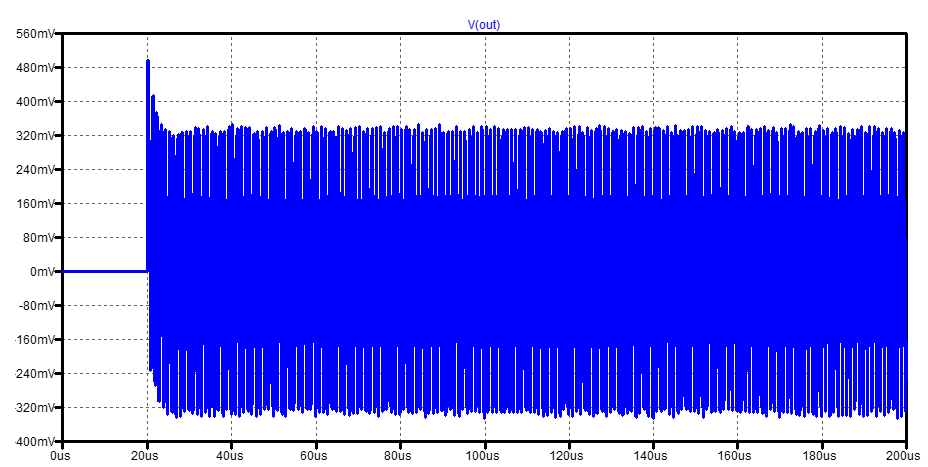

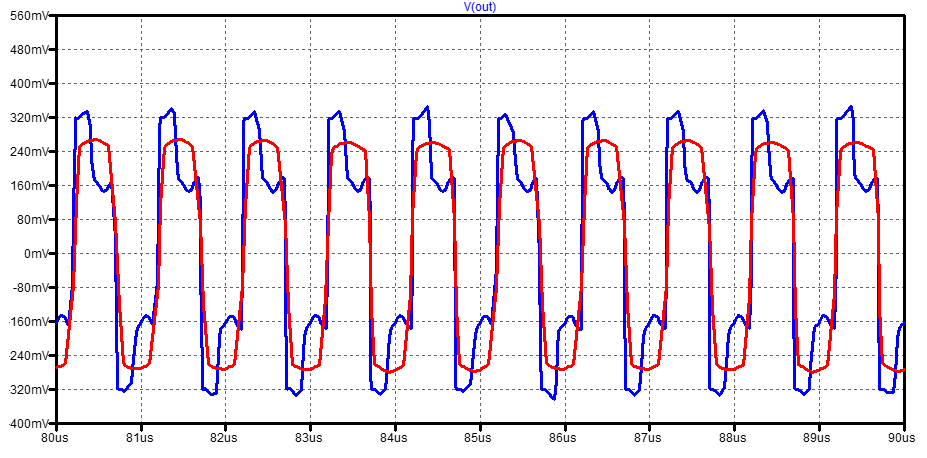

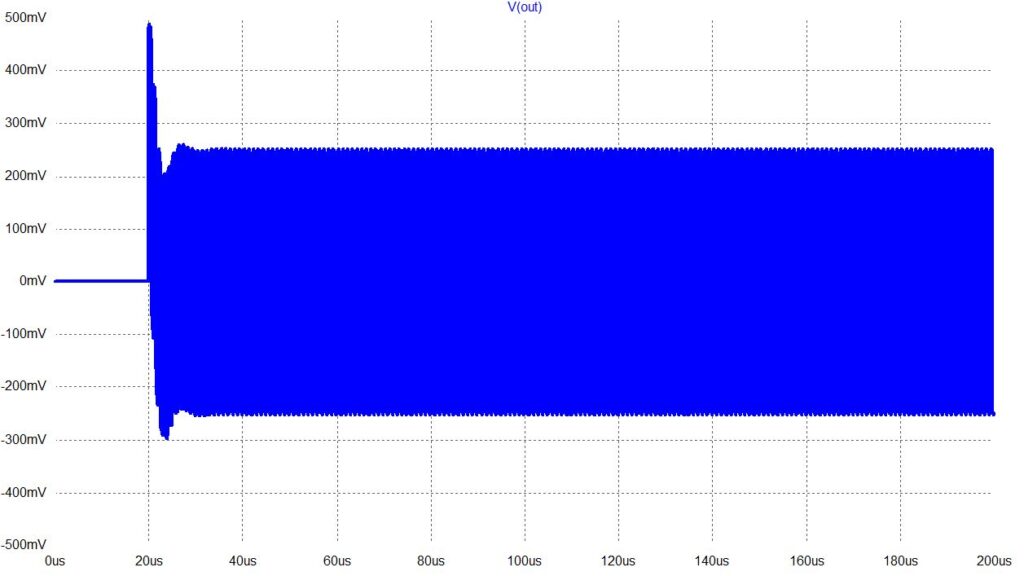

ジッタはほっておくとどんどん増えるので、低い周波数の方(周期が長いほど)その量が多い事になります。PLLの応答が間に合う周波数であれば、基準からずれた位相を基準に合わせる事ができるので、ジッタが無くなる事になります。

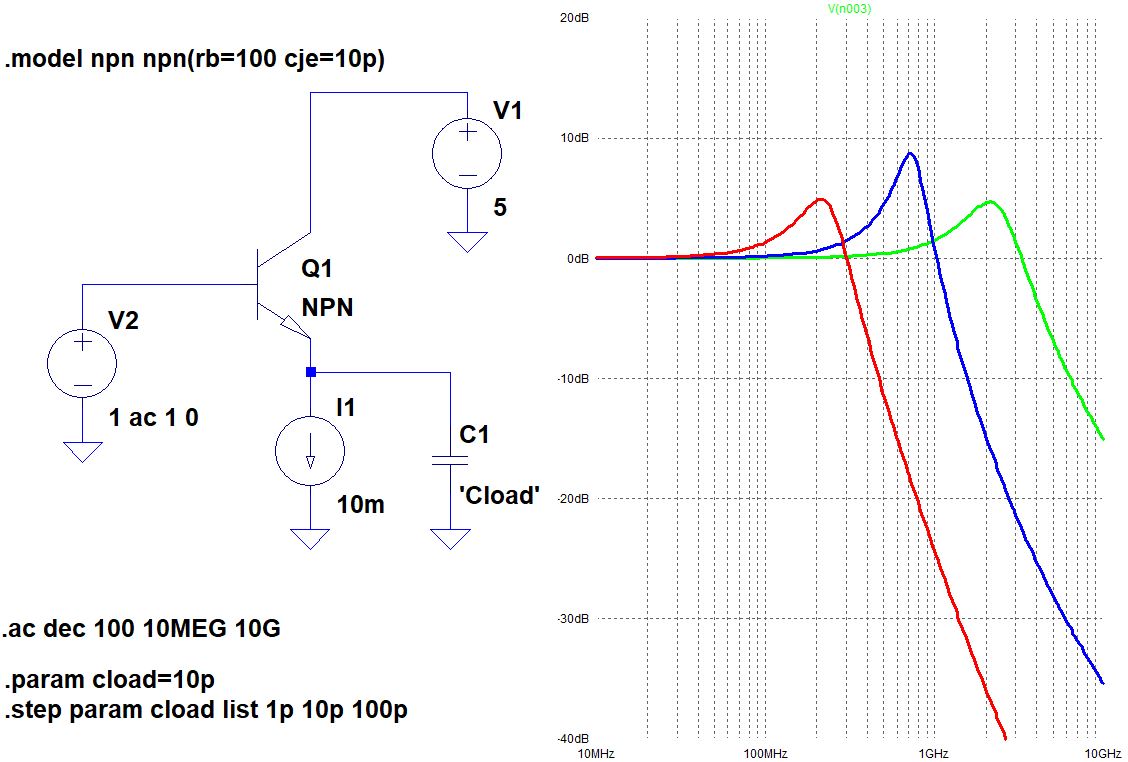

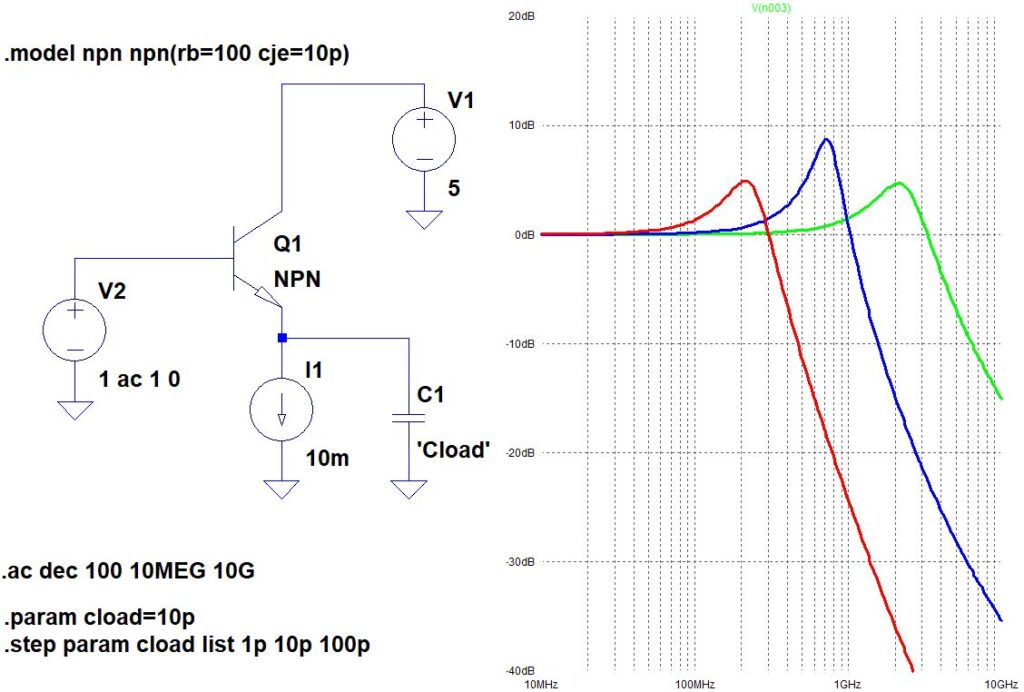

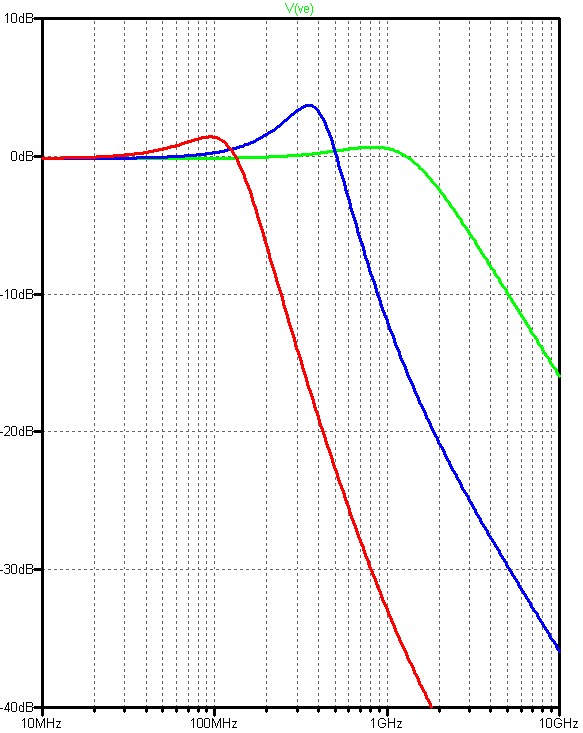

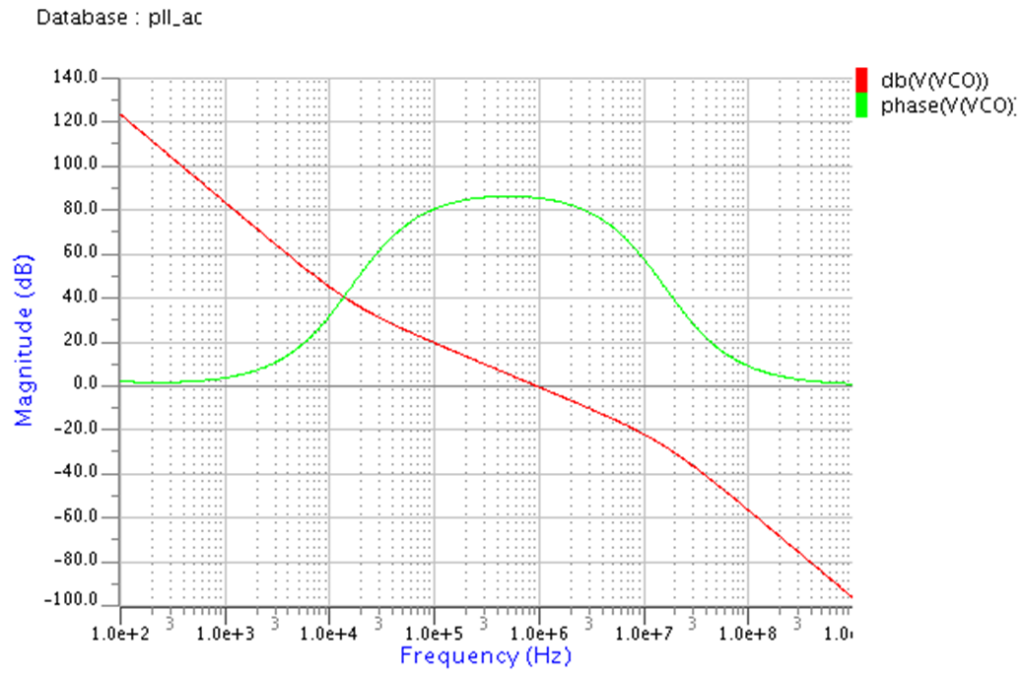

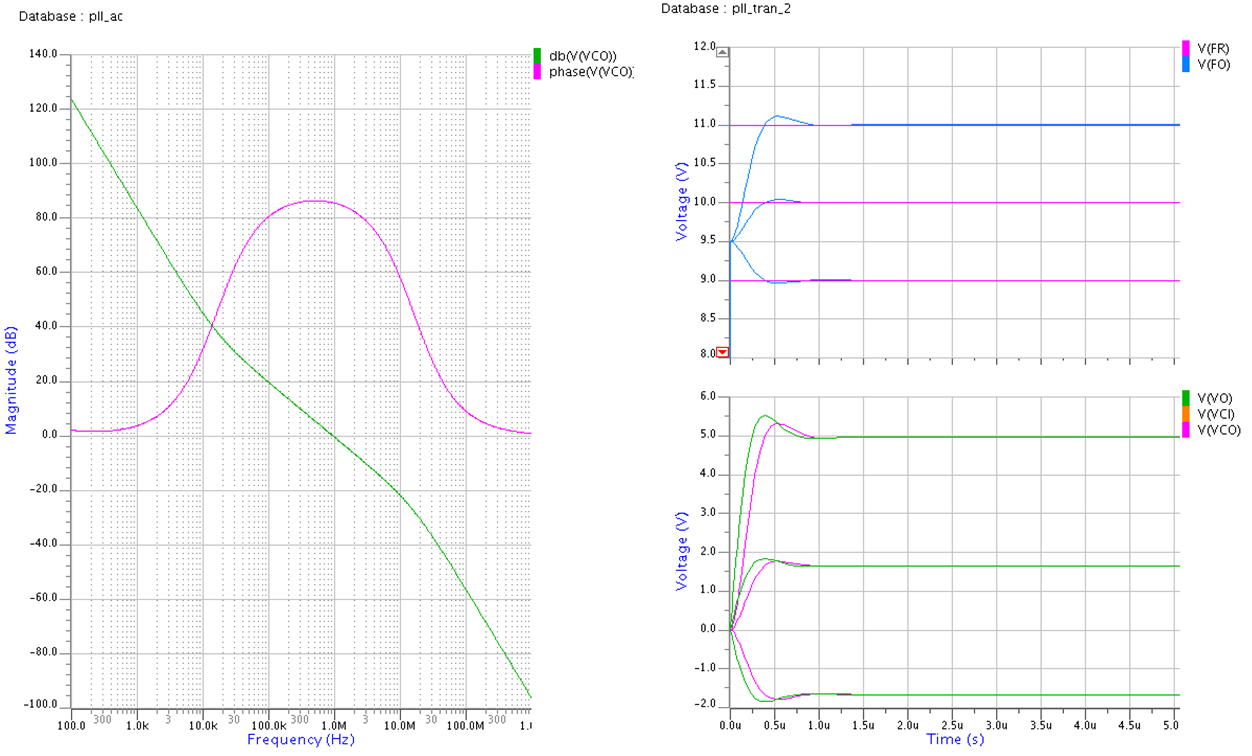

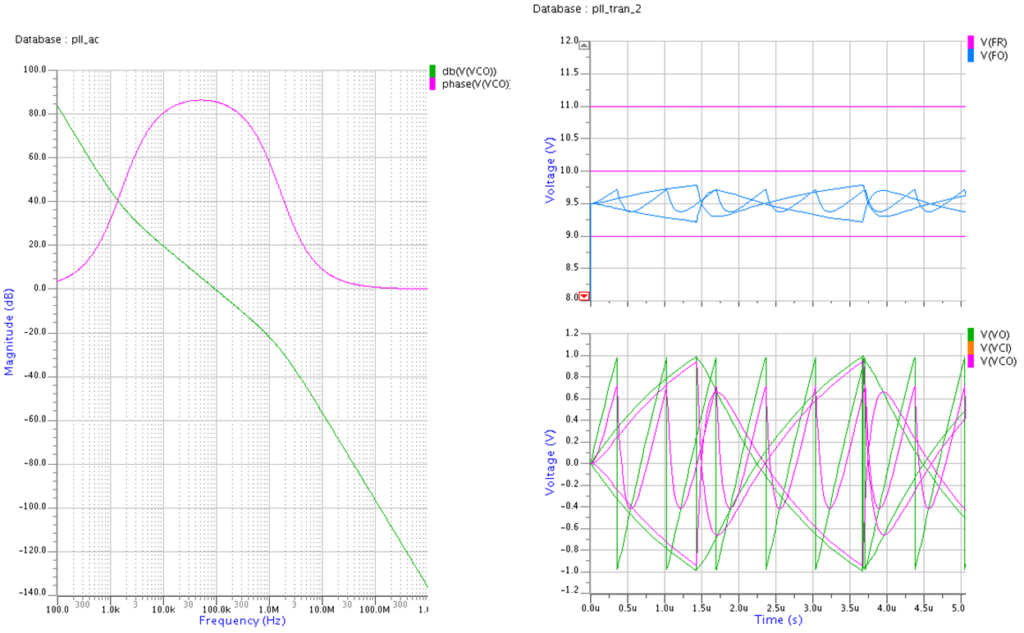

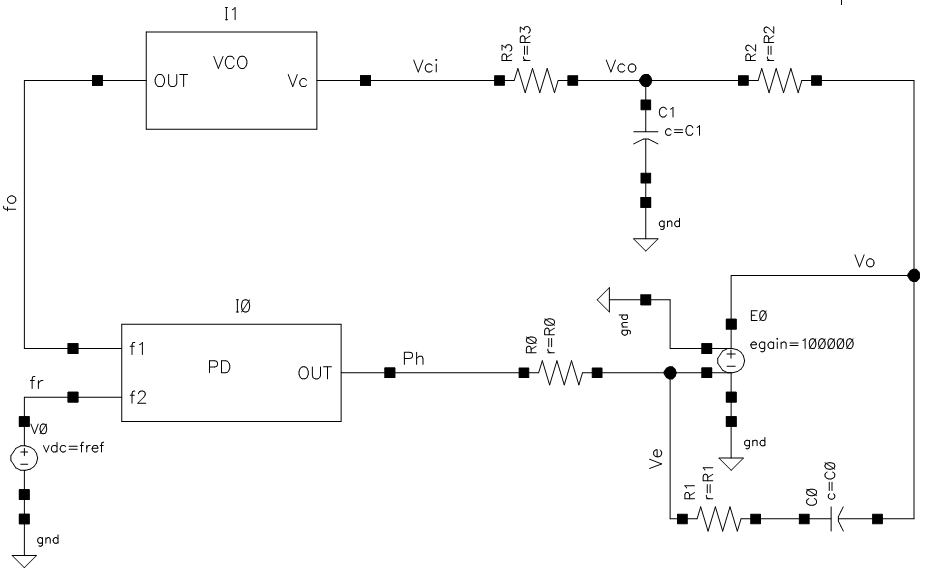

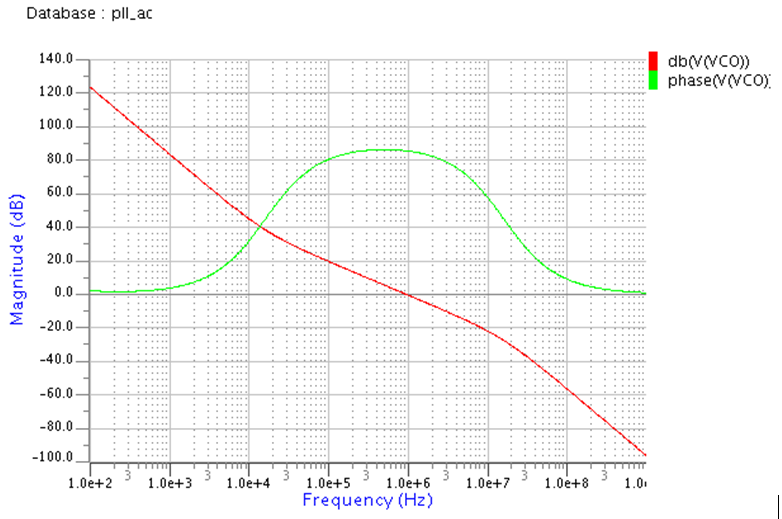

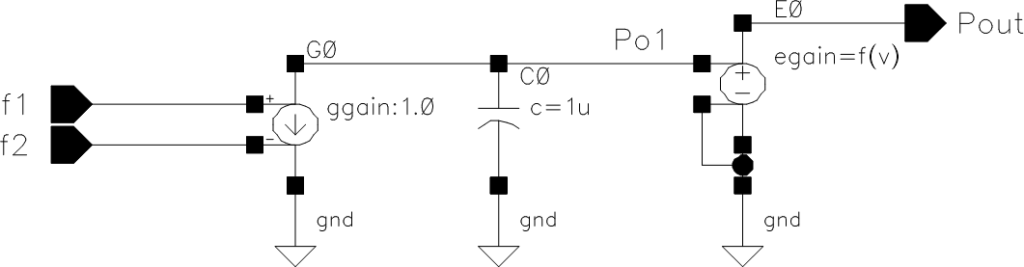

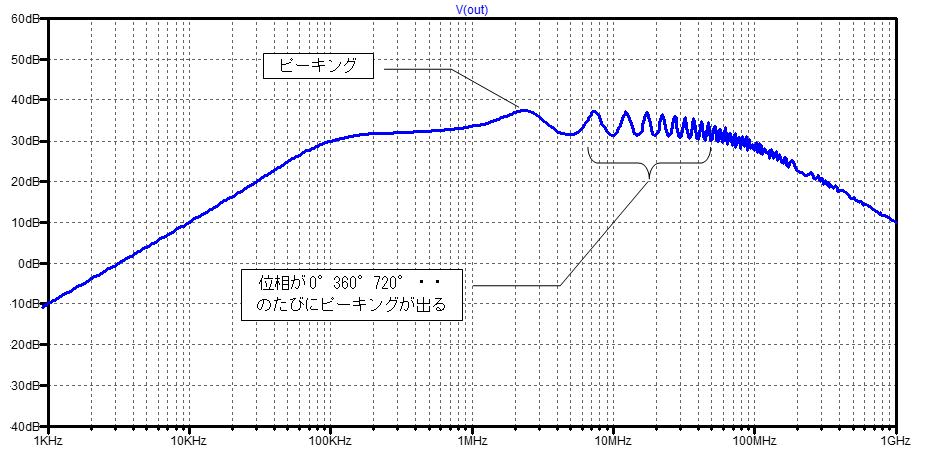

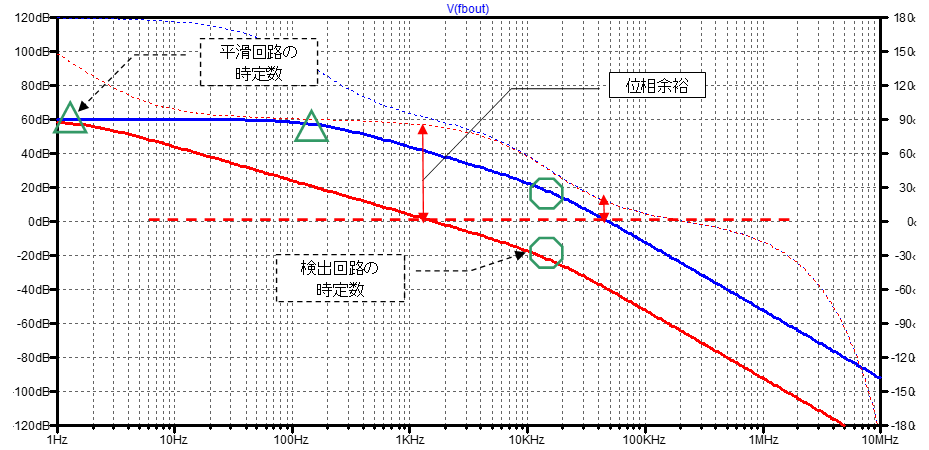

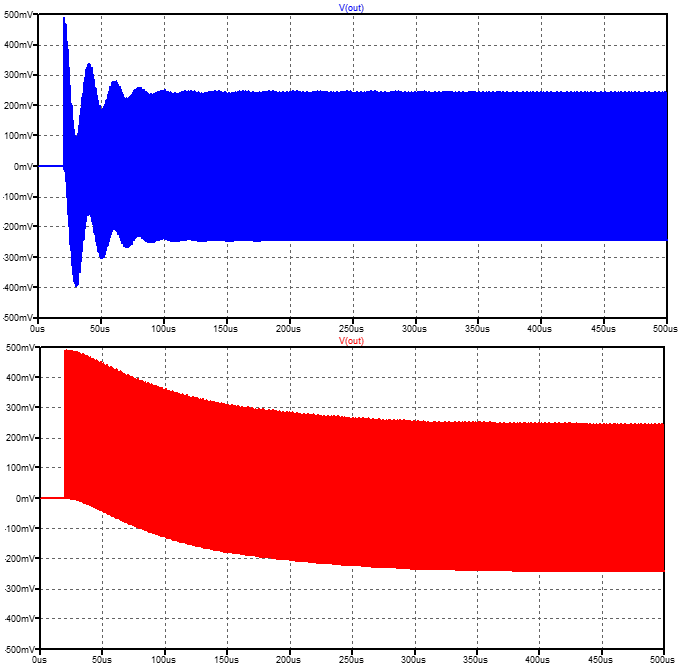

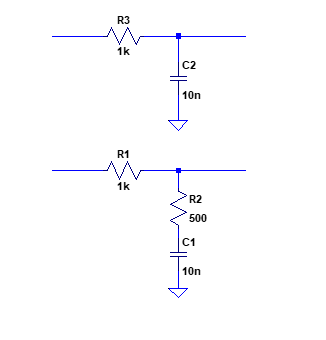

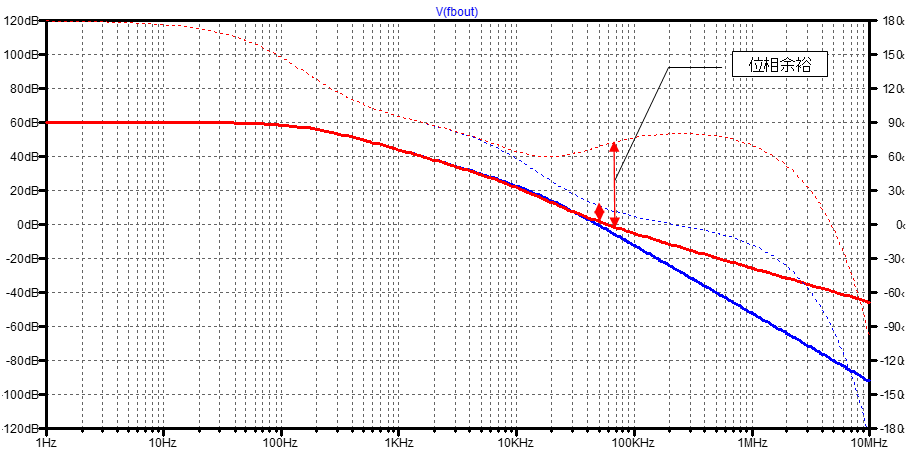

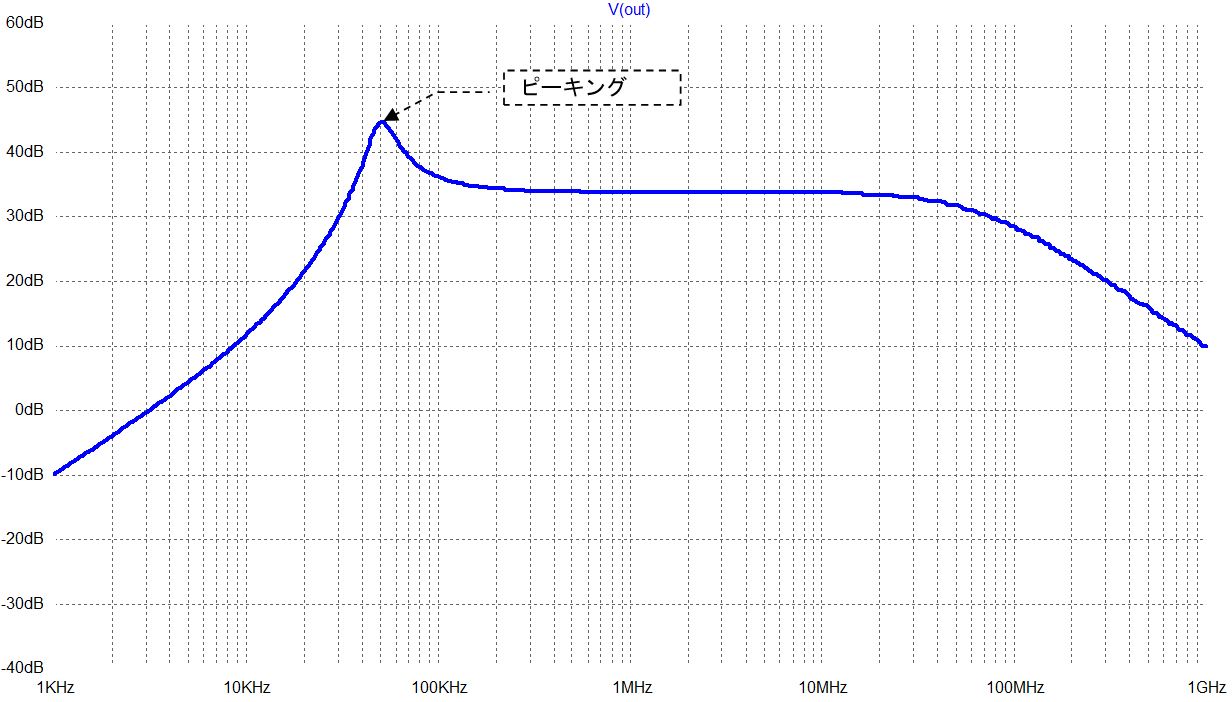

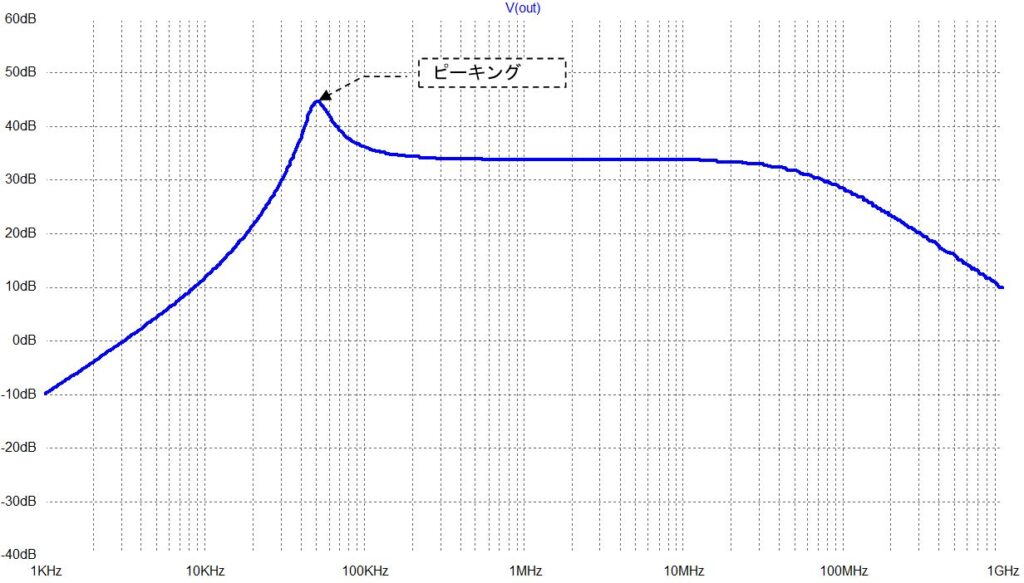

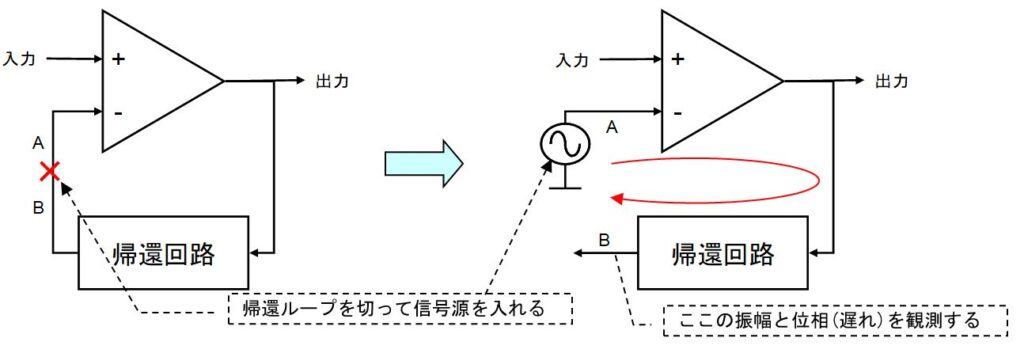

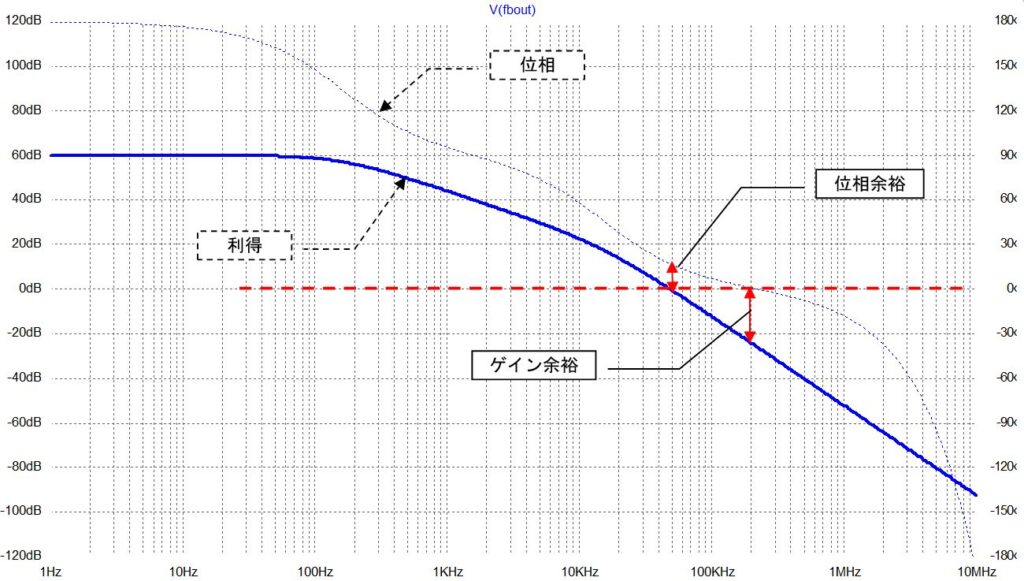

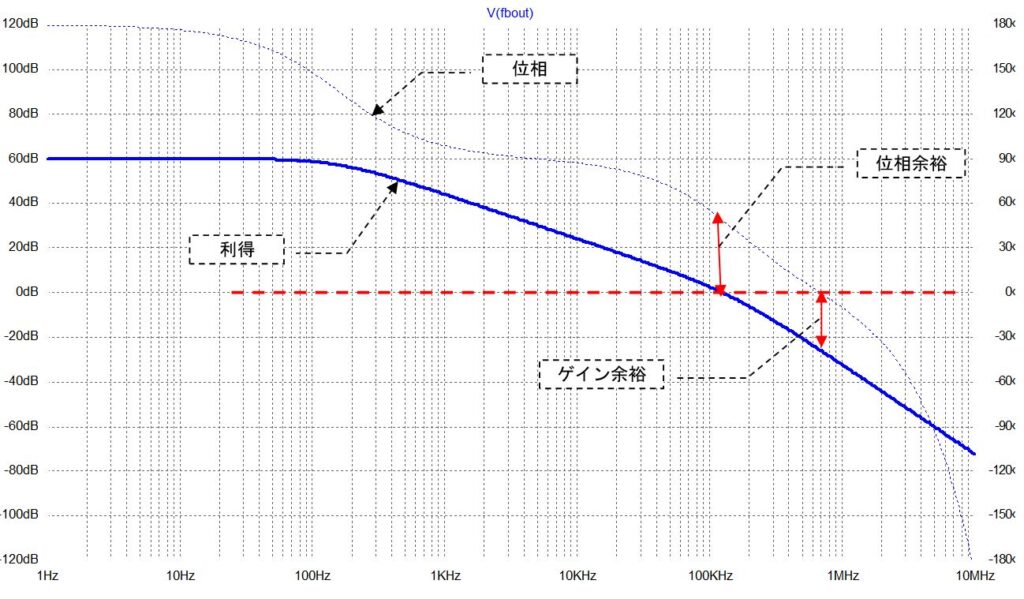

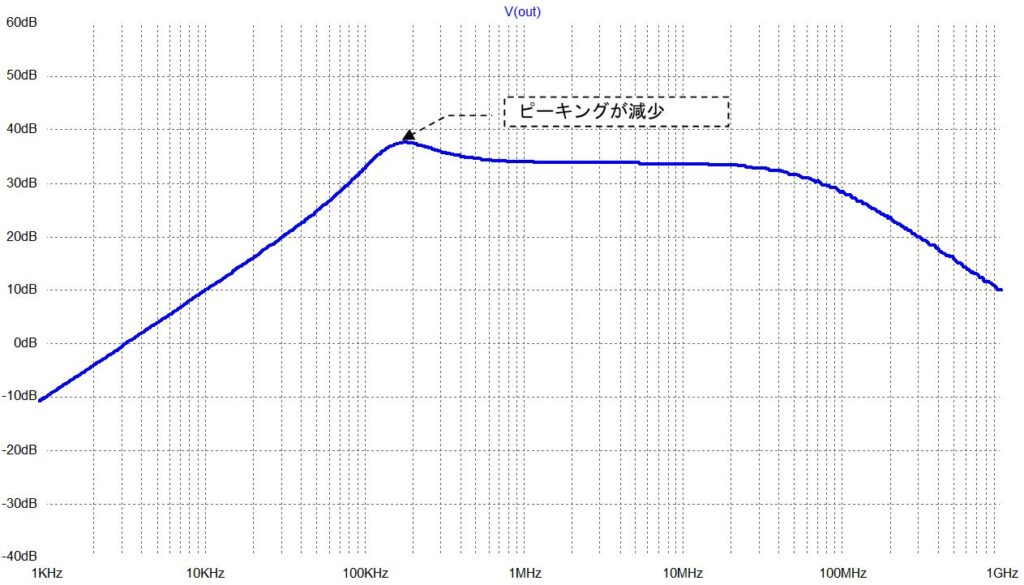

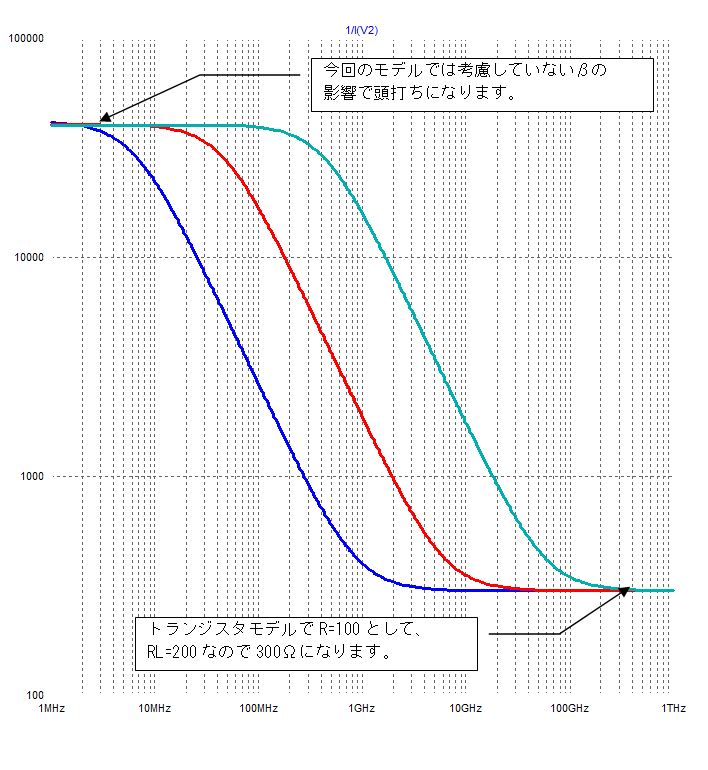

PLLの応答速度は、オープンループ特性(PLL(その2)を参照ください)の利得が0dBとなる周波数とほぼ同じになります。上の図では1MHzなので、1MHzより遅いジッタが修正できることになり、その分のジッタはVCO出力からは無くなる事になります。

次回は、ビヘイビアモデルを使って応答速度とジッタの量の関係を確認してみたいと思います。(美斉津)

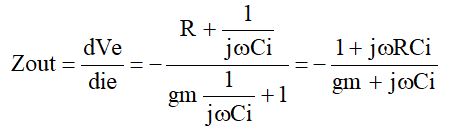

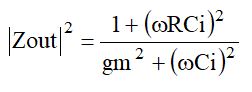

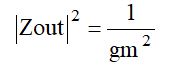

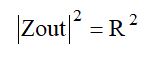

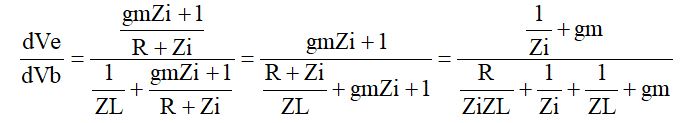

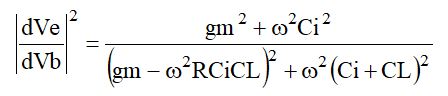

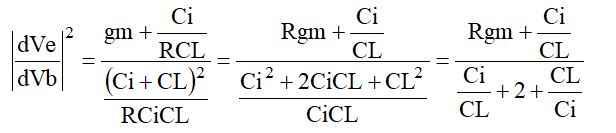

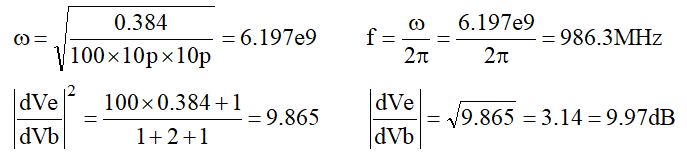

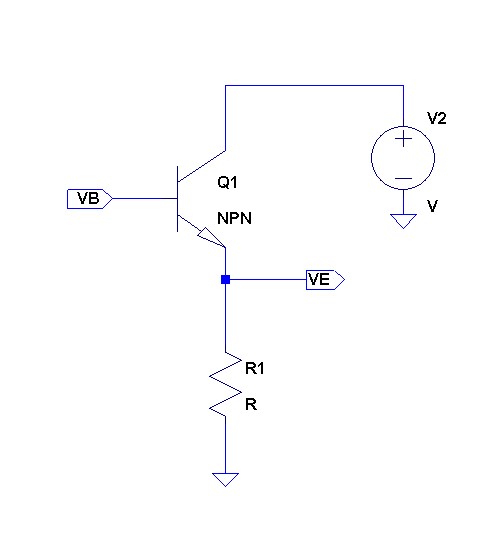

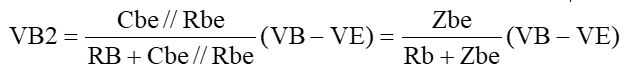

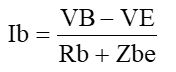

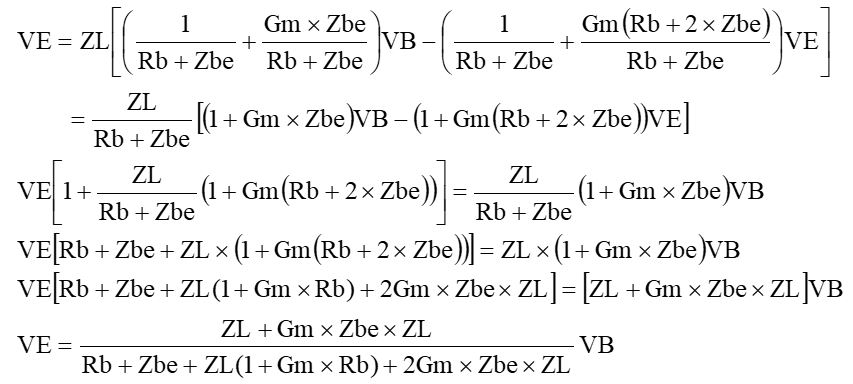

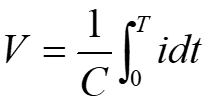

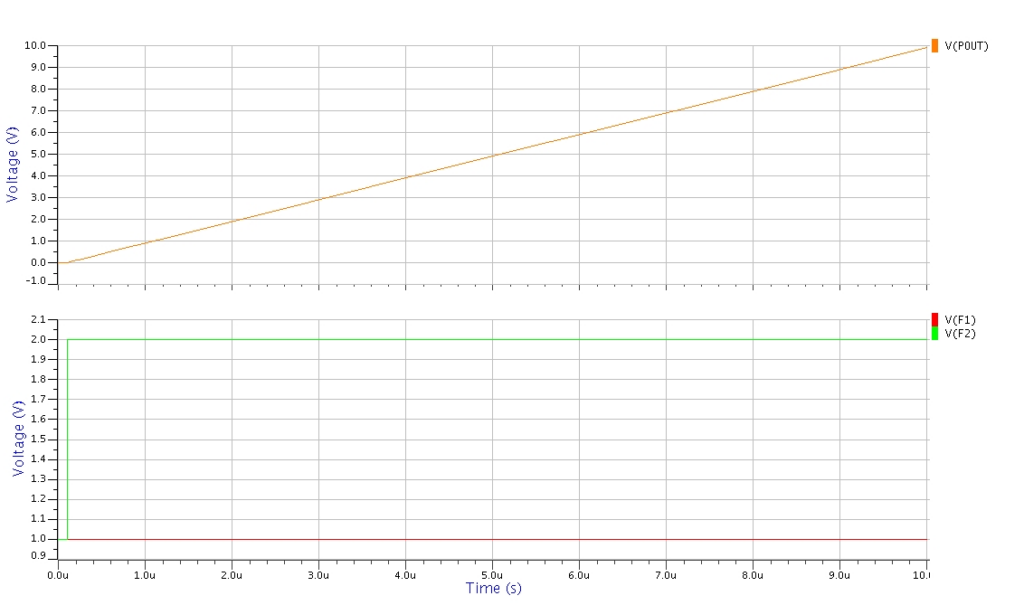

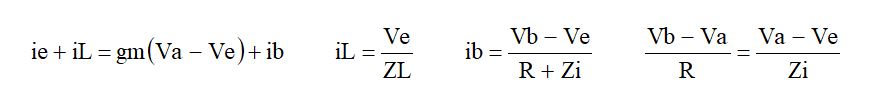

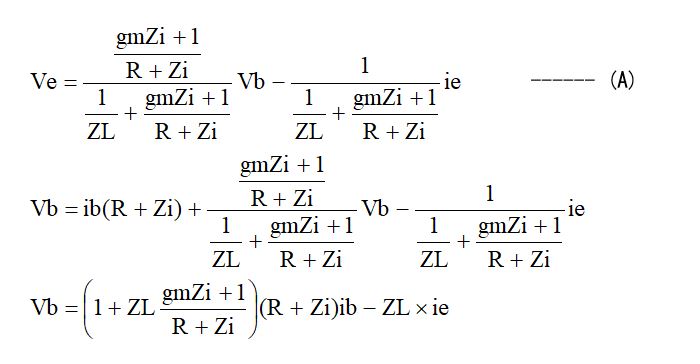

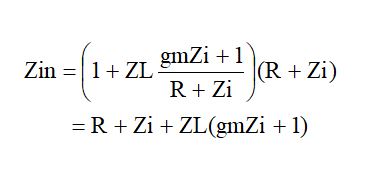

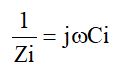

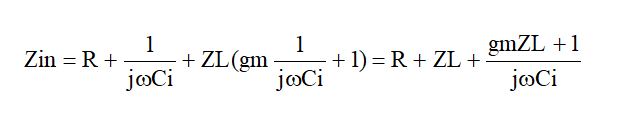

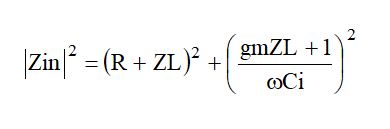

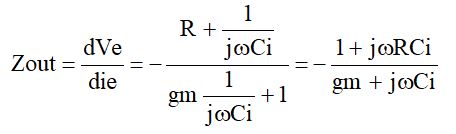

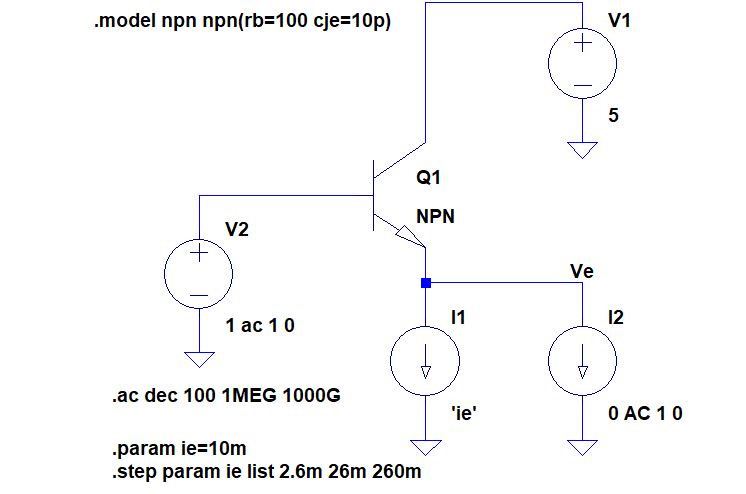

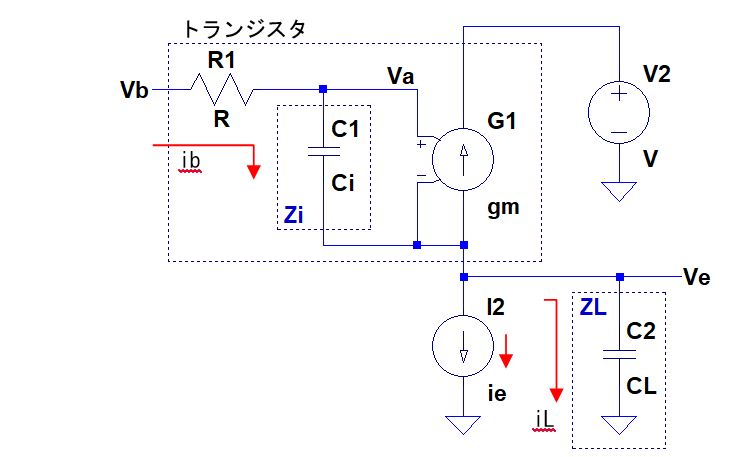

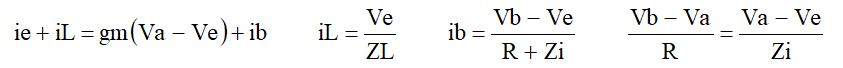

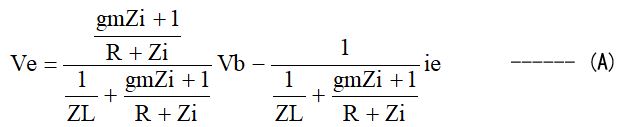

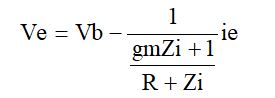

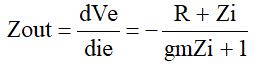

を求めればよいことになります。つまり

を求めればよいことになります。つまり

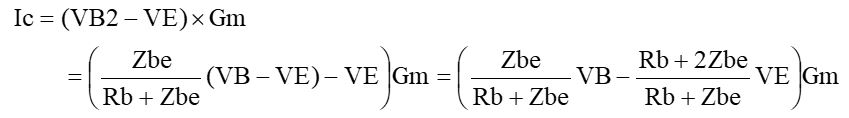

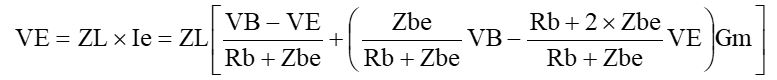

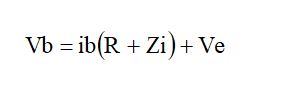

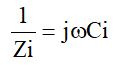

を代入すると、

を代入すると、