今回も“反射”について話をしてみたいと思います。

終端抵抗についてのこれまでの認識

終端抵抗をOpenにしても波形のひずみが出ないことに驚きました。もちろん終端抵抗が特性インピーダンスと整合していないので、思いっきり反射はするのですが、終端抵抗の両端、つまりVoutの波形は歪んでいません。

今までの理解は「終端抵抗で最初の反射が発生するので、この箇所の整合は一番重要でここさえ抑えておけば、後は少し整合が悪くても波形は歪まない」でした。

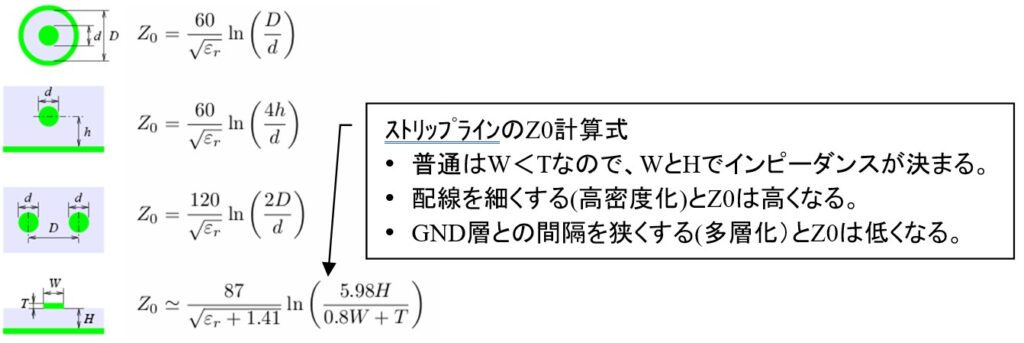

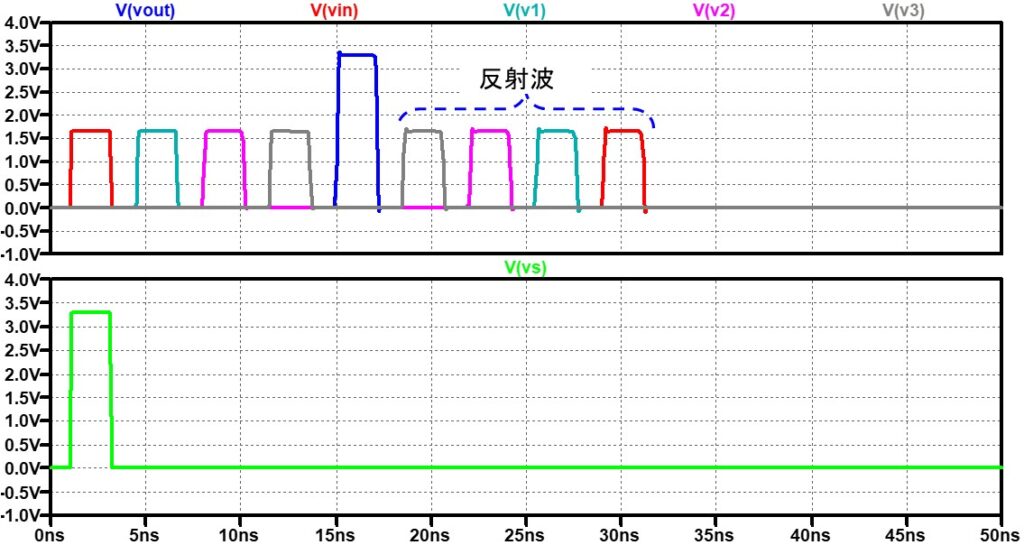

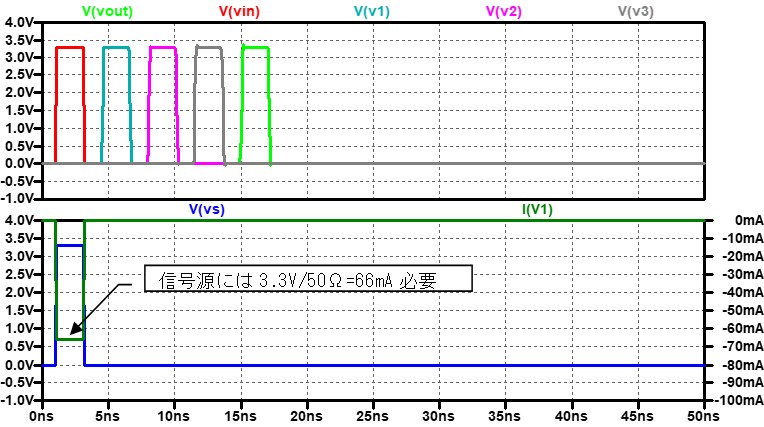

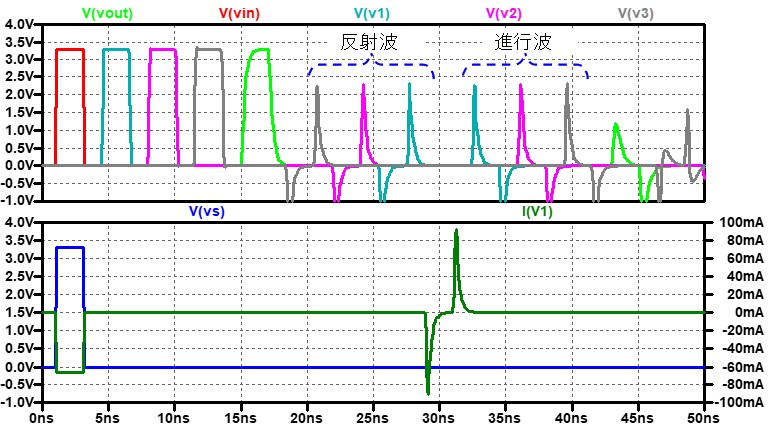

図 1は信号源インピーダンスを5mΩで、終端抵抗を50Ωにした場合です。当たり前ですが終端側で整合しているので、反射波が発生していません。このとき信号源には3.3V/50Ω=66mAの電流を流す能力が必要になります。

信号源インピーダンスを50Ωにして、終端抵抗を50GΩとする

図 2は信号源インピーダンスを50Ωにして、終端抵抗を50GΩとした結果です。

終端側では整合していませんので、反射波が発生します。しかし、受信端の波形V(vout)は図 1とさほど変わりません。また、信号源に流れている電流は図 1の半分で済んでいます。更には反射波が同じ量で逆向きの電流を流しているので、信号源に流れる平均電流、つまり直流の電流は打ち消されてゼロになっています。終端抵抗が50GΩ(OPEN)なので、直流電流が流れないと言ってしまえばその通りなのですが、感覚的には納得いかないところです。こうなると、終端側に整合抵抗を入れるよりも信号源側に整合抵抗を入れた方が消費電力が少なくて済むので、有利だと言うことになります。

寄生デバイスの影響を考慮した反射とインピーダンス整合

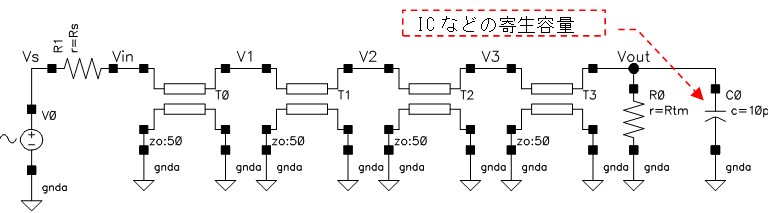

今までは終端側が理想的な状態、つまり寄生デバイスの影響がない事を前提にしてきました。実際には終端側(例えば、ICの入力端子)には寄生容量などがついています。

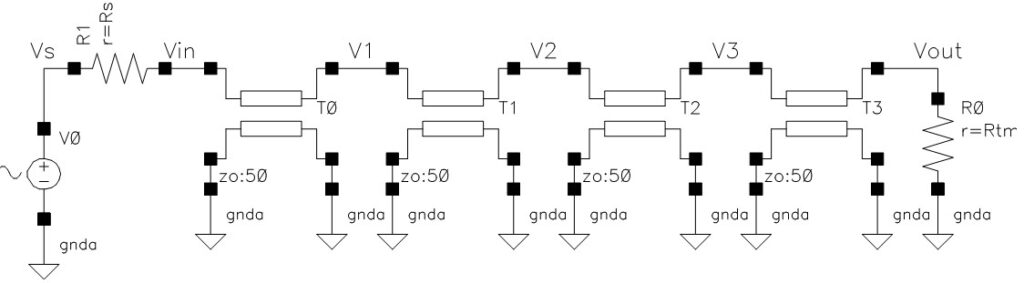

寄生容量=10pFとしたときの反射の様子

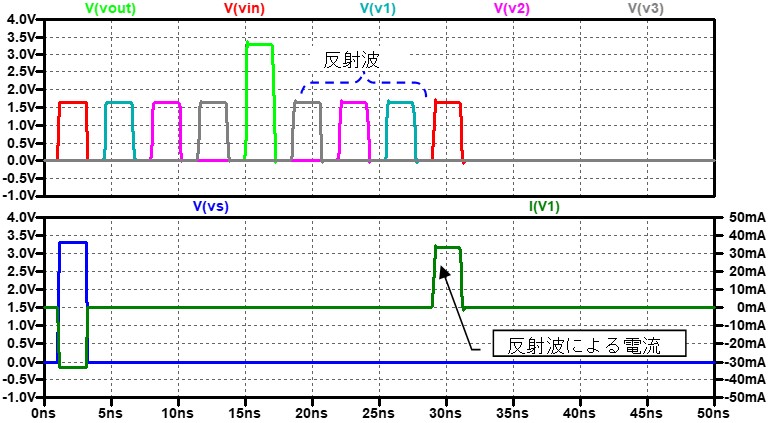

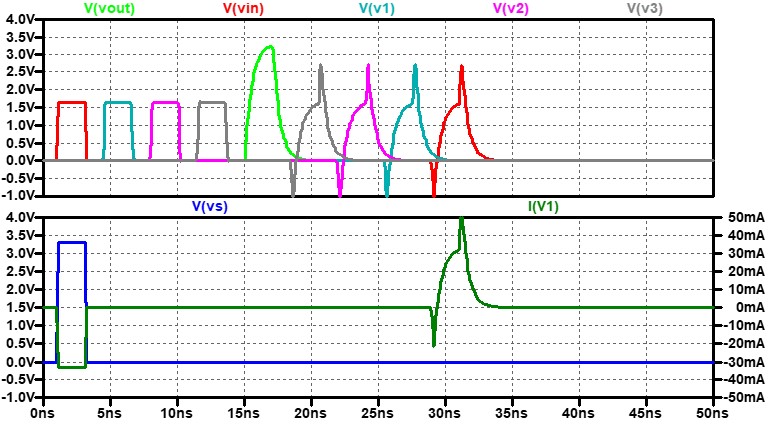

例えば図 3の様に寄生容量=10pFとしたときの反射の様子をシミュレーションしてみると次の様になります。

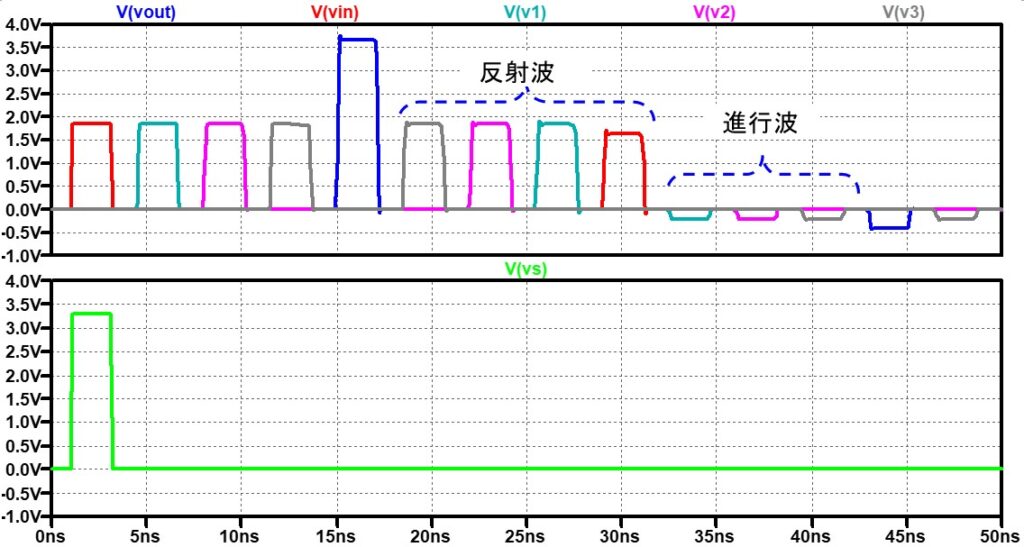

図 4が終端側で整合したもの、図 5が信号源側で整合したものです。

両図とも早い周波数成分の立上りや立下りの部分が寄生容量C0(10pF)の影響で反射していることが分かります。これは寄生容量の影響で終端側の入力インピーダンスが高周波になるほど低くなっているためです。また終端部分の波形V(vout)を比較してみると、信号源側で整合した方の波形がなまっているのが分かります。単に消費電力の点では信号源側の整合が有利なのですが、伝送速度と寄生容量に依っては信号源側での整合では十分な特性が得られないことがあるので、終端側との併用も検討する必要が出てきます。両方で整合するのが一番なのですが、消費電力や性能を、寄生容量や伝送路の長さなどの制約条件から最適化することが設計者の腕の見せ所と言えると思います。

パルス幅を長くして、反射波と重ねる

今まではパルスの幅が2nsecと短くして反射波が重ならないようにしてきました。

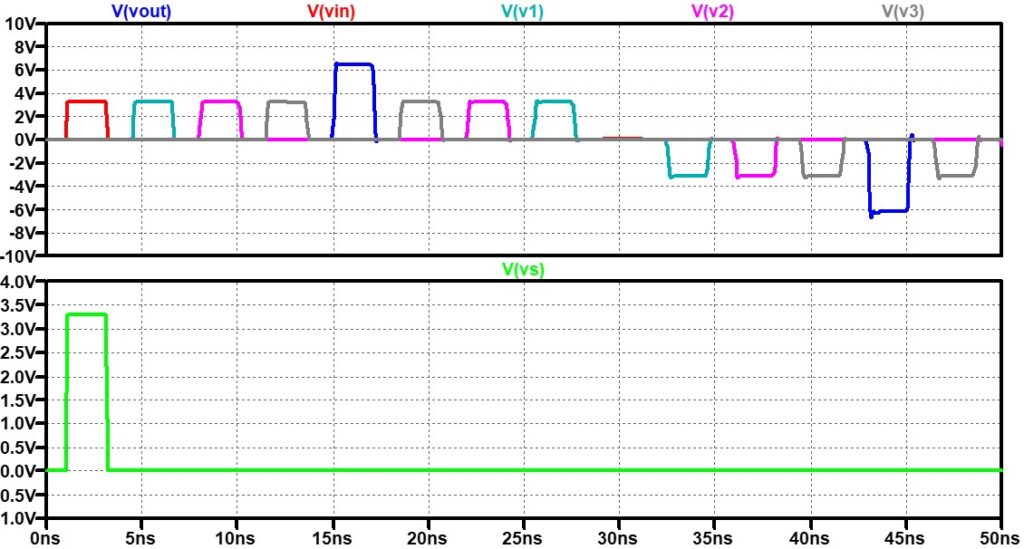

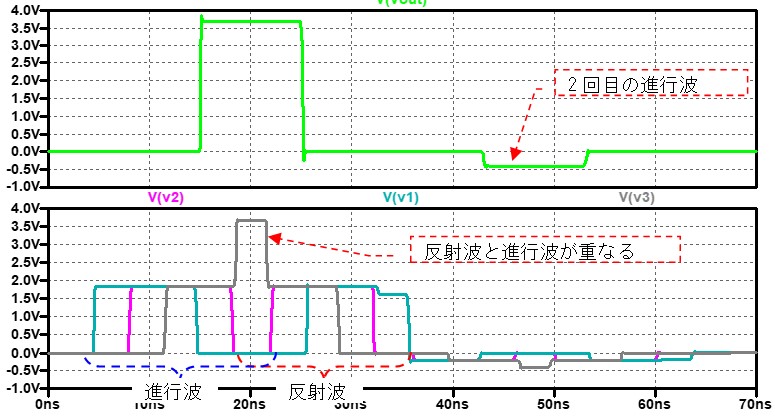

図 6はパルス幅を20nsecと長くして、反射波と重なる様にしたものです。なお、信号源インピーダンスRsを40Ω(すこし反射します)、終端インピーダンスRtmを50GΩ(全反射です)としています。

終端側のV(vout)にはあまり影響が見られないですが、伝送路内のV(v3)では進行波と反射波が重なるため振幅が2倍になる箇所が出てきます。

例えば、伝送路の中間(例えばv3)から信号を取り出すように信号を分配する仕組み(mini-LVDSインターフェースなど)では要注意です。

さらに、複数のパルスを扱う

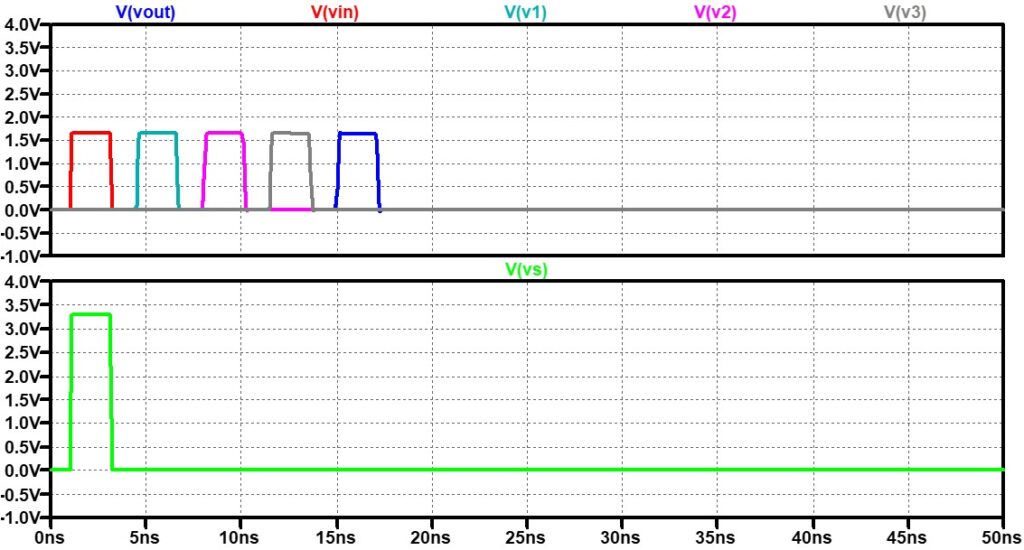

今までは孤立パルス(1個だけ)を扱ってきましたが、実際には複数のパルスが使われます。

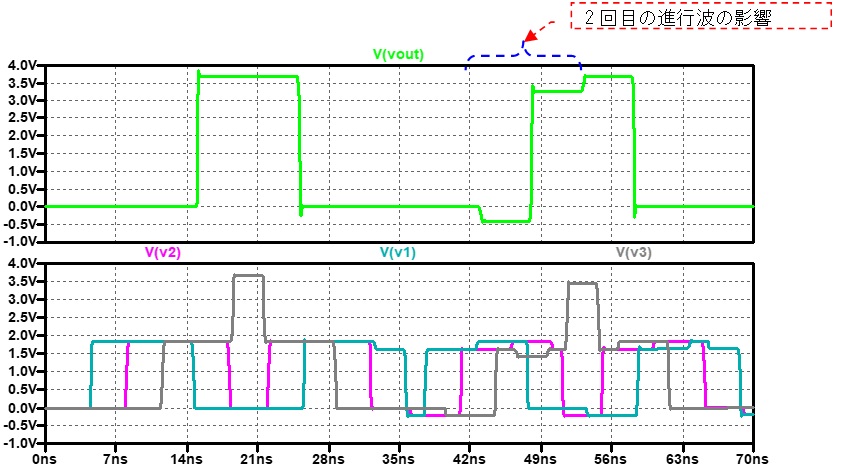

図 7の様に、前のパルスの反射に依って発生した2回目の進行波と次のパルスが重なると終端側の電圧に干渉として現れます。

反射は発生させないことに越した事は無いですが、反射波をいち早く整合させて消失させる事が大切で、信号源側と終端側の両方で反射を繰り返すと(多重反射が起きると)、自パルス以外の波形にも大きな影響を与える事に成ります。

いままでは過渡解析を使って反射を説明してきましたが、次回は小信号解析(AC解析)も使って、もう少し反射と格闘してみたいと思います。