少し間が開いてしまいましたが、今回は前回触れなかった「ゲイン余裕」とか「位相補償」について話してみたいと思います。

まずは「ゲイン余裕」が無い場合、どんなことが起きるかを紹介します。

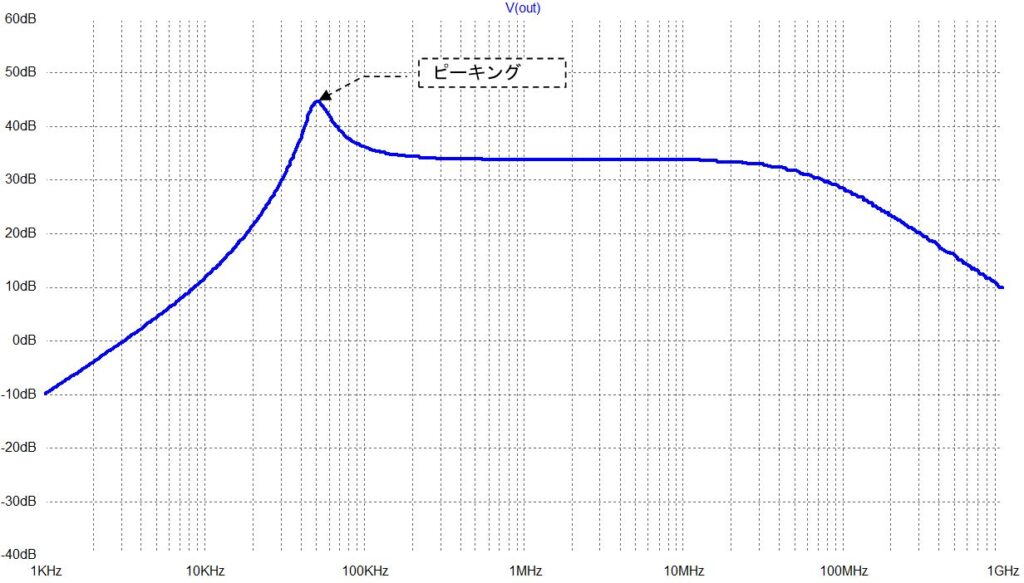

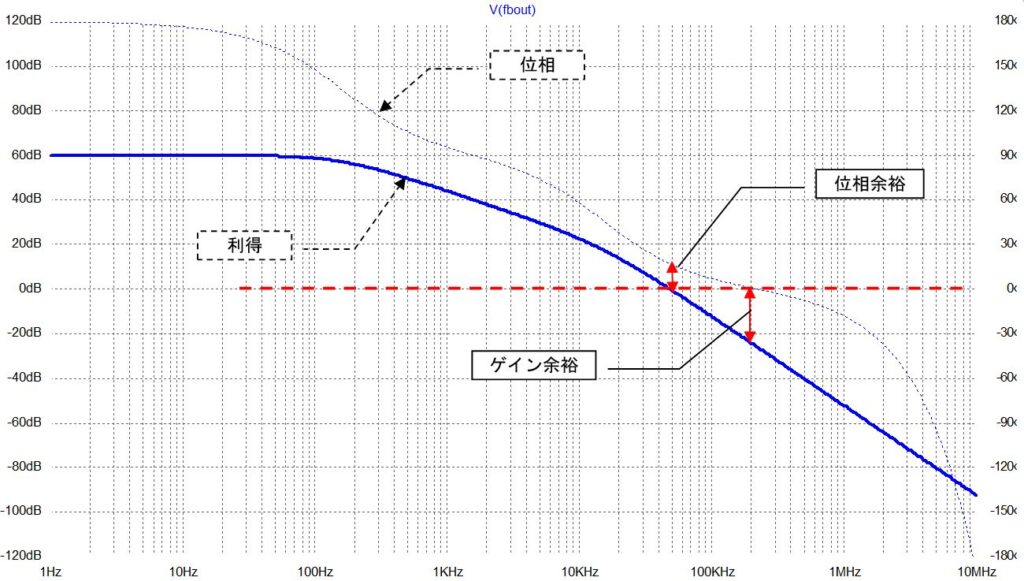

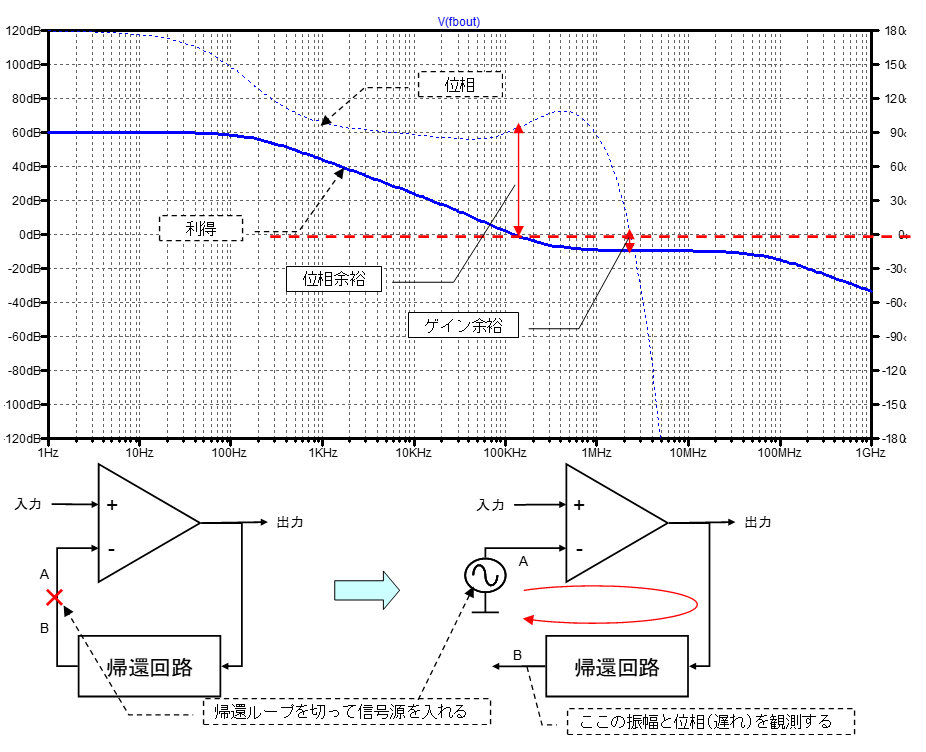

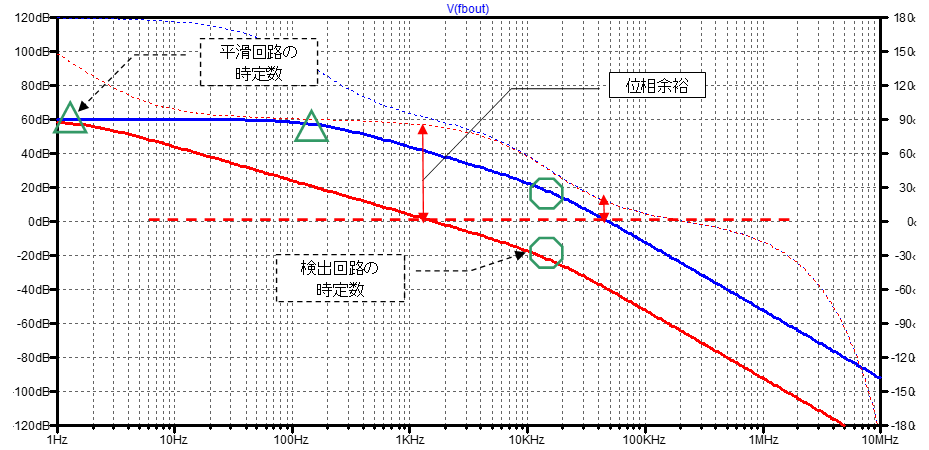

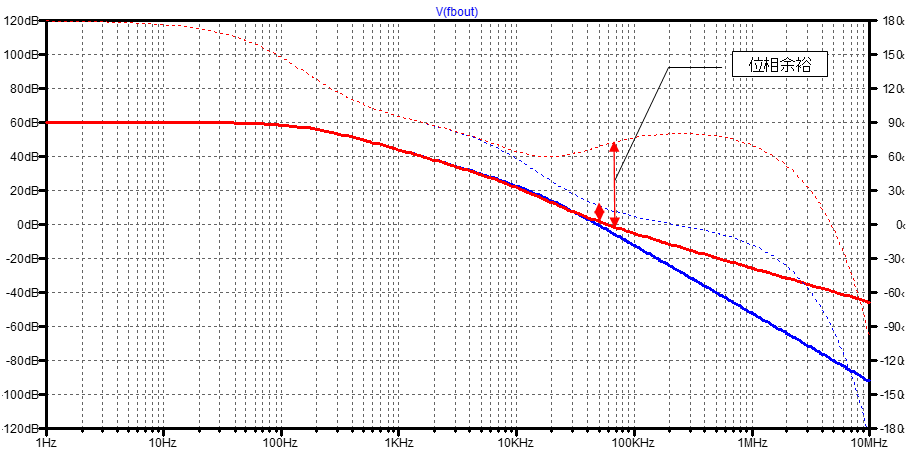

上のボード線図は、位相余裕は90°以上あり十分ですが、ゲイン余裕は9dB程度しかない状態です。

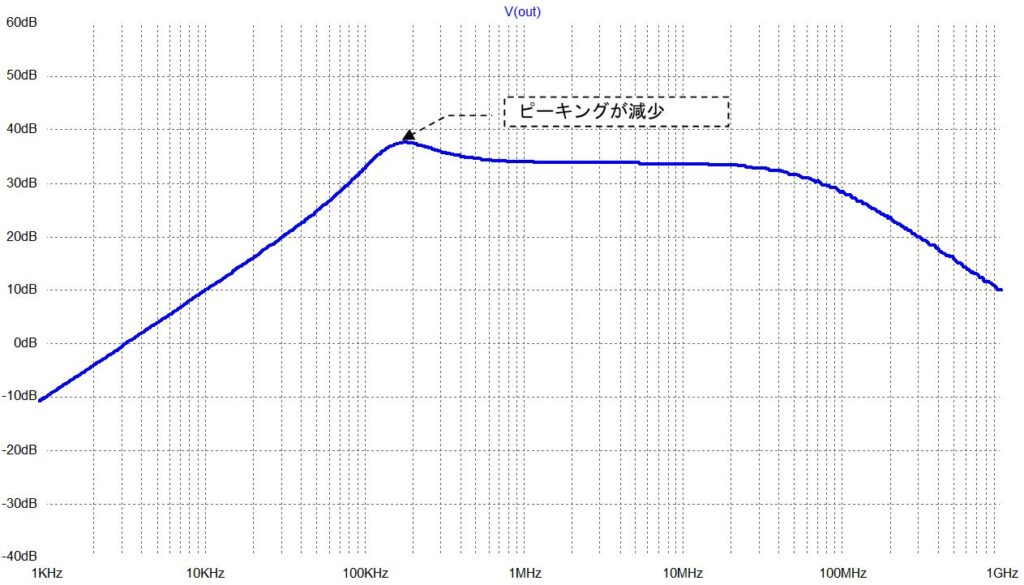

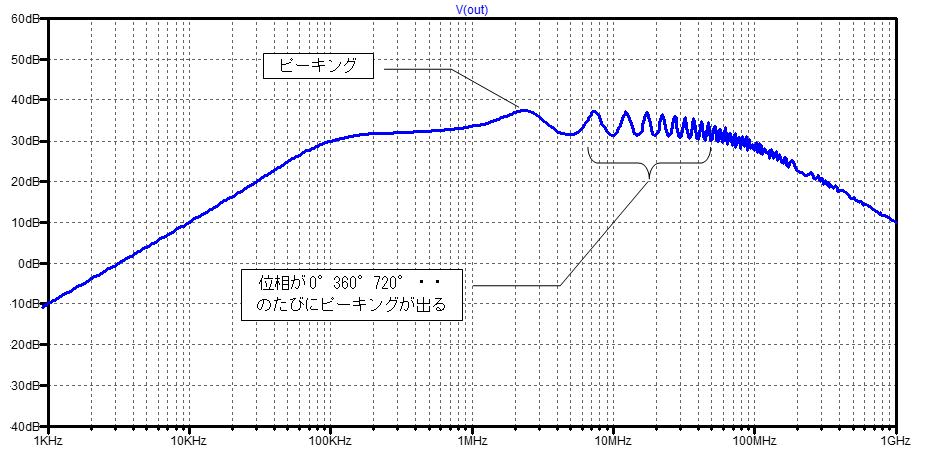

この状態で出ループを閉じてアンプの入力=>出力の周波数特性を見ると、ゲイン余裕が少ない周波数(この例では2MHz以上)にピーキングが発生します。

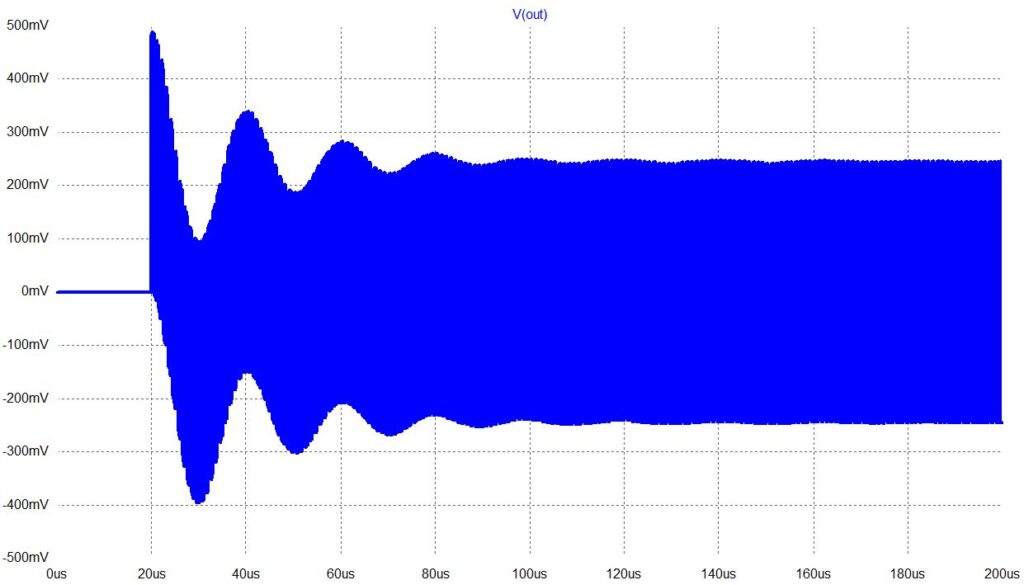

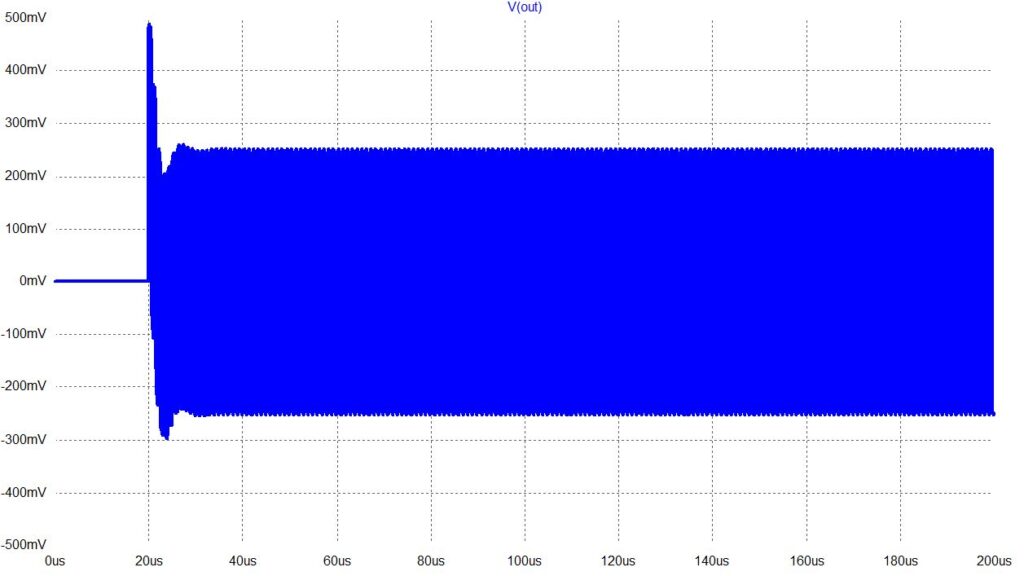

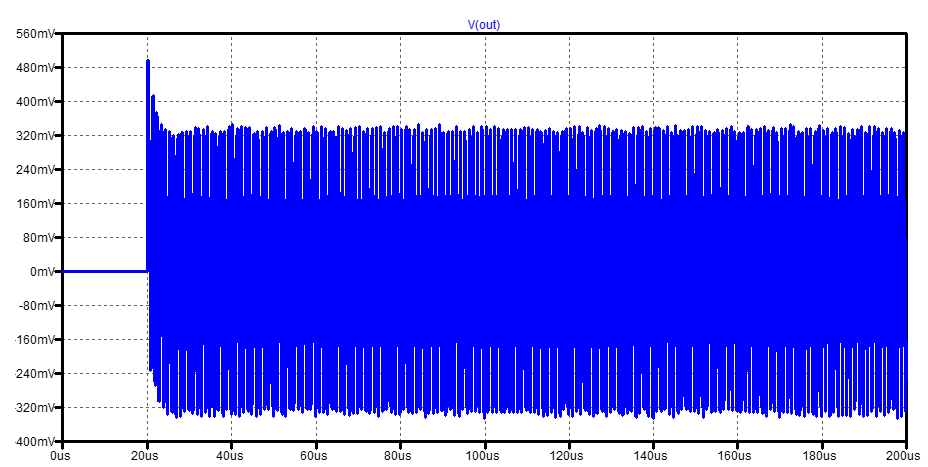

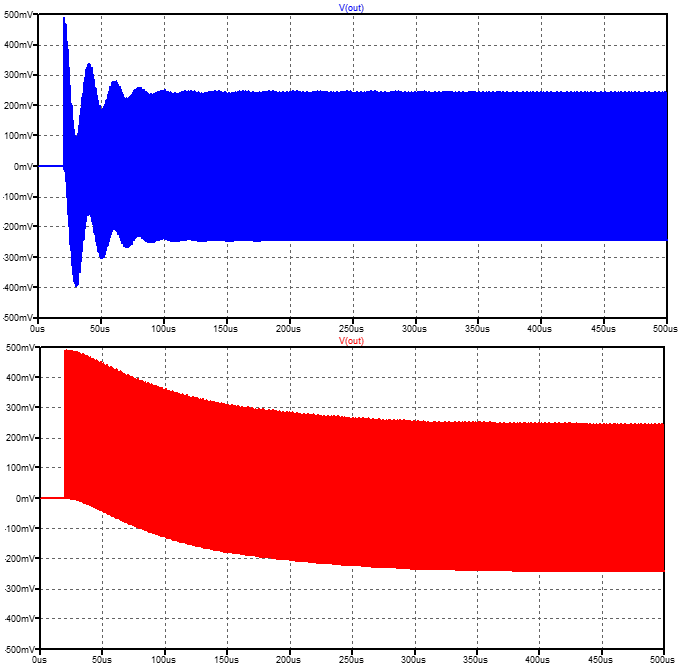

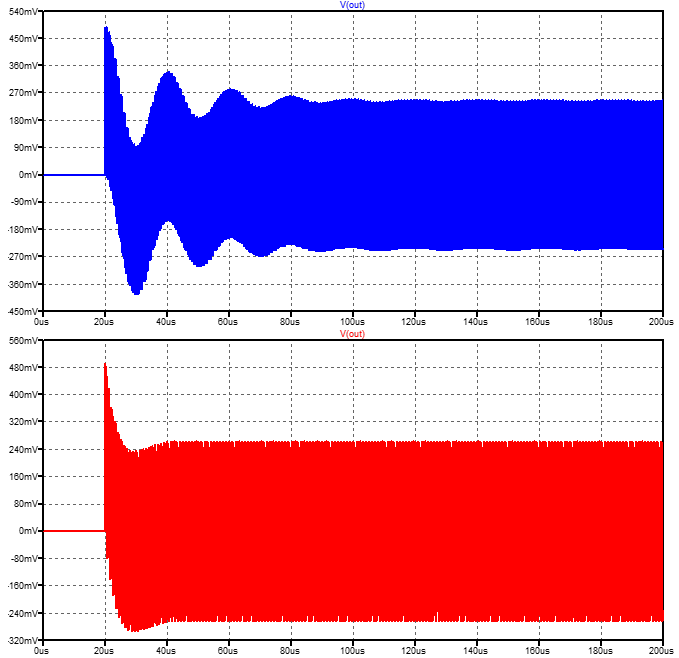

アンプの出力波形は、一見よさげに見えますが、拡大してみると・・・

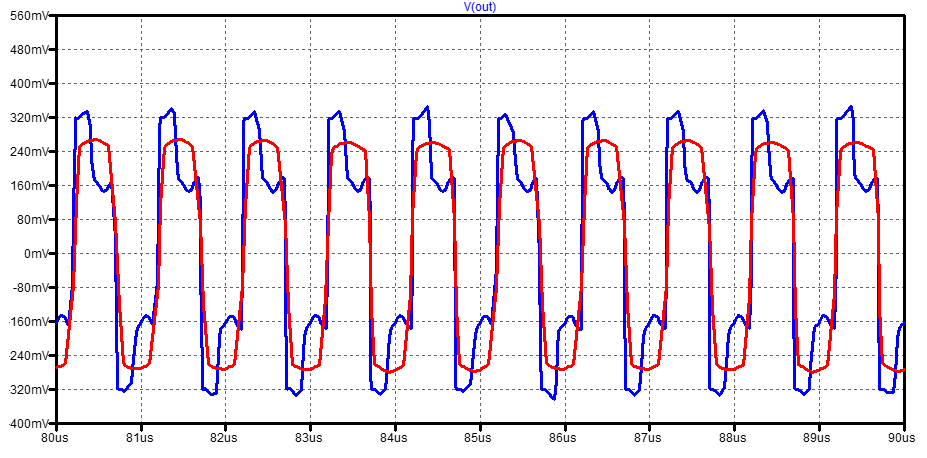

ゲイン余裕が確保できているときの波形(赤色)に対して、ゲイン余裕がないときの波形(青色)は歪んでしまっています。

現実の回路では、ゲイン余裕だけがなくなるケースは少ないため位相余裕の方に注意が行きますが、ゲイン余裕も目を配らないと後で痛い目を見ます(汗)。

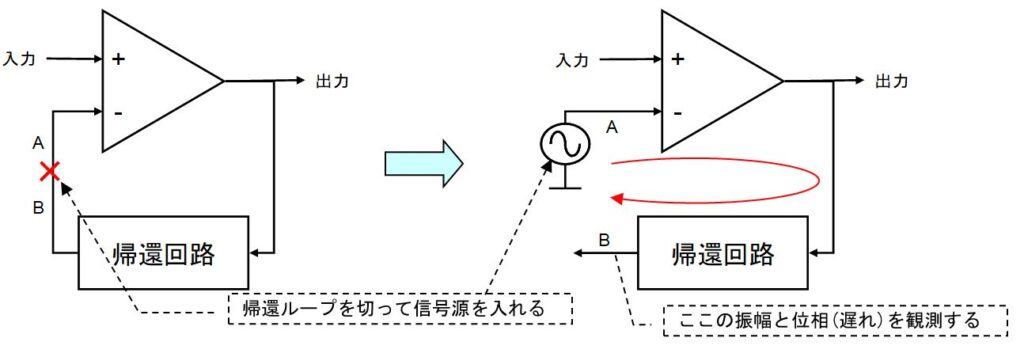

続いて位相補償について触れたいと思います。

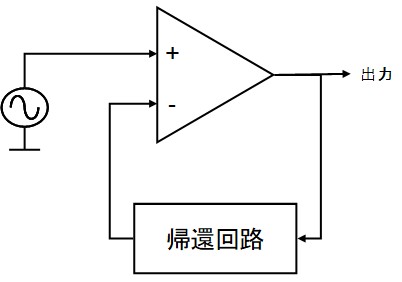

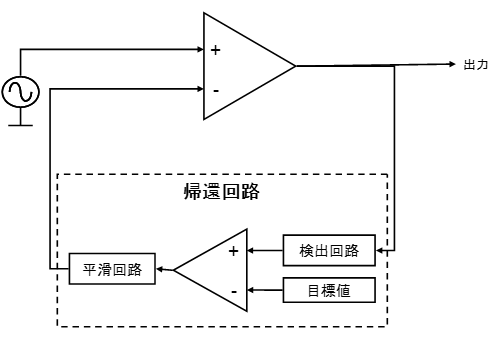

たいていの負帰還回路は上の様な構成になっています。制御したい成分を”検出回路”で検出し、目標値と比較した後、平滑化して元のアンプの反転入力に戻します。平滑化は無くてもすむ場合もありますが、帰還回路で発生した雑音を除去するためにLPF(Low Pass Filter)を入れるケースがほとんどです。

出力電圧の平均をある値に制御する(一致させる)ときなどは、平均値を検出するためにLPFを使います。このような場合、検出回路と平滑回路の両方に位相が遅れ、位相余裕がなくなりループが不安定になり、リンギングが発生します。

これを改善するためには平滑回路と(平均値)検出回路の時定数を”大きく離すこと”が有効です。

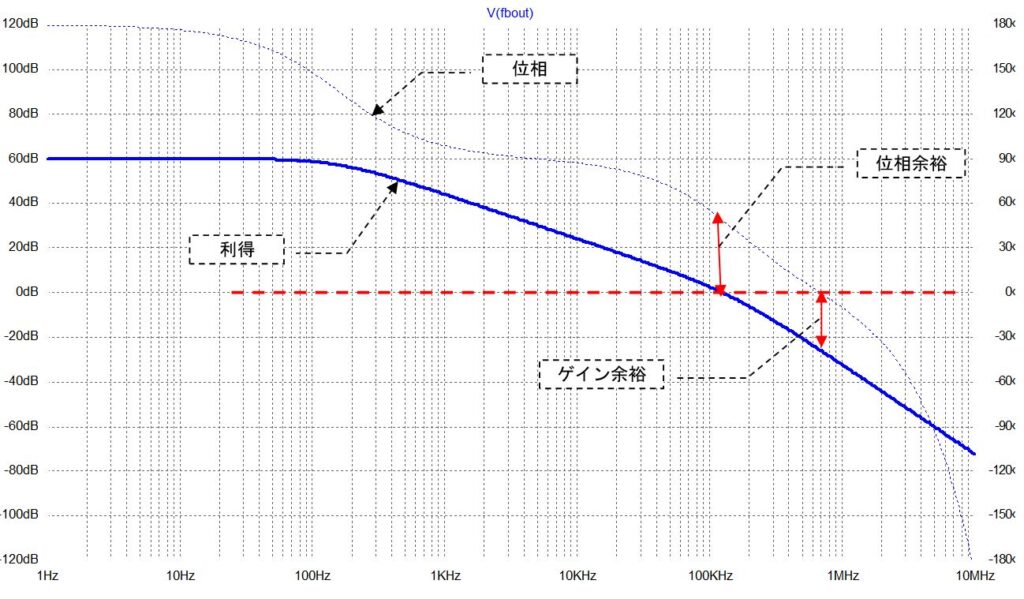

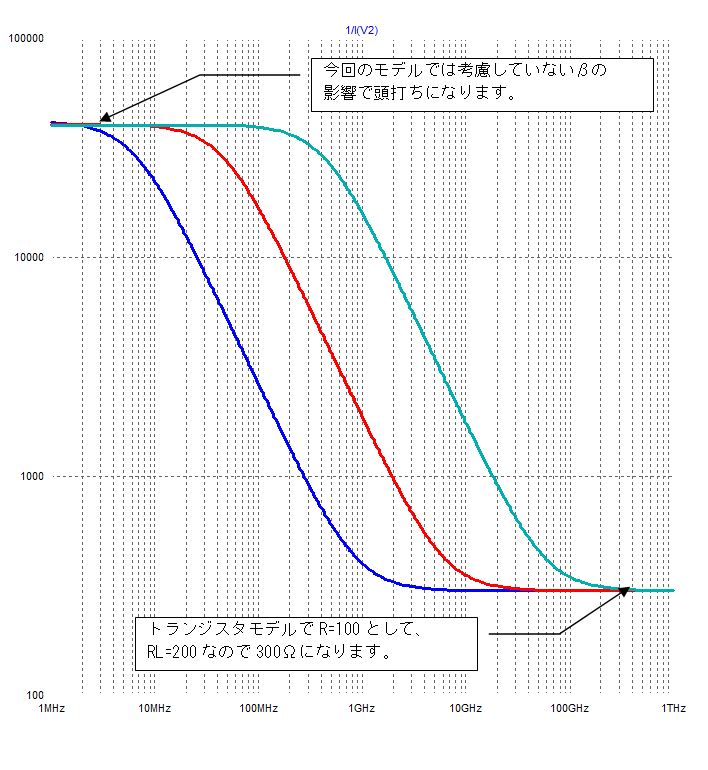

青の線の場合は、2桁しか時定数に差が無いのですが、赤の線では、4桁の落差を時定数につけています。

時定数に落差をつけることで、リンギングはなくなります・・・しかし、収束するのに時間がかかるようになってしまいます。

別の方法で、位相余裕を改善するには”位相戻し”回路を使う方法があります。

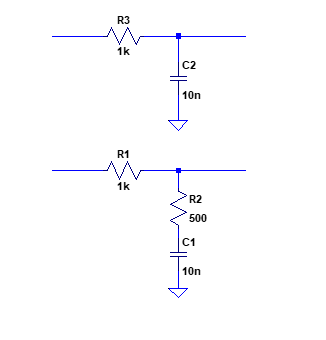

上は普通の平均値検出回路(単なるRCのLPFです)ですが、下は位相戻し回路を追加した平均値検出回路です。

抵抗R2が追加されただけなのですが、R2とC1が微分回路になっているため位相が進み、遅れていた位相を補正することが出来ます。

位相戻し回路が入った赤線は位相余裕も多く確保できていて、リンギング量が少なくなっていることが分かります。

位相補償の方法として”時定数を大きく離す”、”位相戻し回路を入れる”の2種類を紹介しましたが、後者のほうが応答速度(収束)を遅くすること無く安定動作をするので広く使われています。

負帰還回路を安定動作させるためには”位相が0°の時に利得を正にしないこと” が基本なので位相補償のやり方は様々ですが、負帰還回路に共通して言えるポイントは以下の2点です。

✔ 検出は迅速に。

✔ 比較結果はゆっくり戻すこと。

会社や組織をうまく機能させるコツも負帰還回路と一緒で、”情報を迅速に集めて、的確に判断し、じっくりと実施する”こと、すなわち、”位相余裕を確保すること”ではないかと思います。

次回はPLLの話を始めたいと思います。