今回から何回かに分けて、フリップフロップ(FF)について紹介していきたいと思います。以前のブログに“メタステーブル”と書きましたが、この単語もフリップフロップの紹介の中で説明できたらと思います。

FFというとデジタル回路という感覚をお持ちの方も多いと思いますが、その中では非常に高度なアナログ的な動作が行われています。FFは信号の”1”,”0″を記憶することができるので、カウンターやシーケンス回路などあらゆるデジタル回路に使われています。

FFの基本はラッチ回路

FFの基本はラッチ(latch)回路です。単語の意味は“掛け金”で、一度カチッとさしたら抜けなくなる仕組みのことです。これを電気回路では”正帰還“をかけて実現しています。

ラッチ回路の仕組み

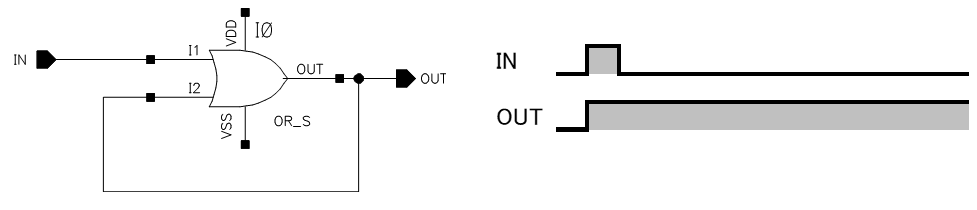

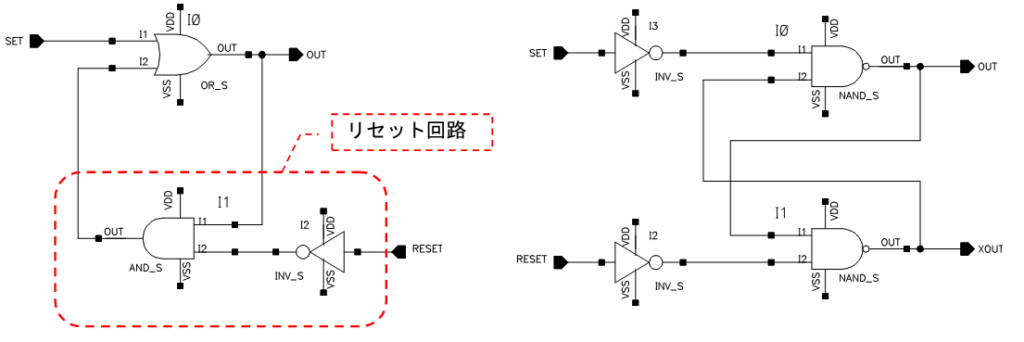

一番簡単なラッチはOR回路の出力を入力に戻して正帰還をかける回路(図 1)です。ORなので一旦出力が”1“に成ってしまうとそのまま元にはもどらず、この状態のままとなります。実際に回路ではこのままでは使えないので元に戻すリセット回路(図 2の左)を追加します。

SRラッチ

AND回路やOR回路で構成した回路と同じ動作をNAND回路で構成して、トランジスタ数を少なくした回路が図 2の右です。動作は図 3の様になります。この回路はSetとResetの動作をするのでSRラッチと呼んでいます。

Dラッチ

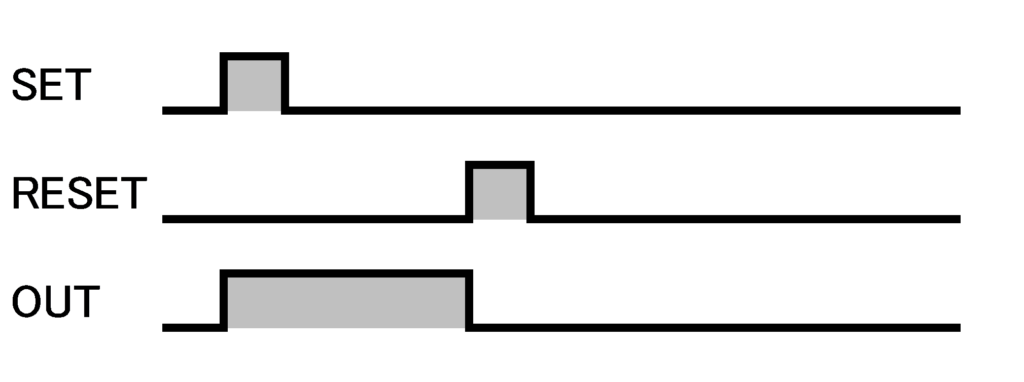

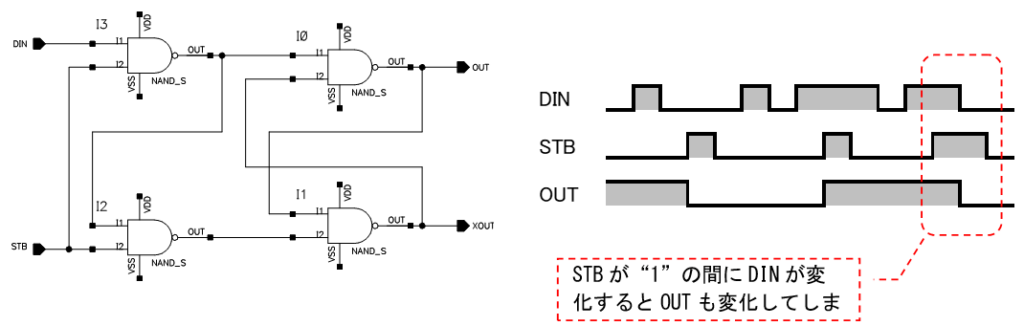

このSRラッチを応用して入力したデータを保持する様にしたDラッチという回路(図 4)があります。

この回路はSTB(ストローブ)信号が“1”の時間は、入力DINがそのまま出力OUTに現れて、STBを“0”にするとその状態を保持する回路です。しかし、STB=”1“のときは入力信号が変化すると出力も変化してしまい、いろいろと問題が発生します(したのだと思います)。

D-FF回路

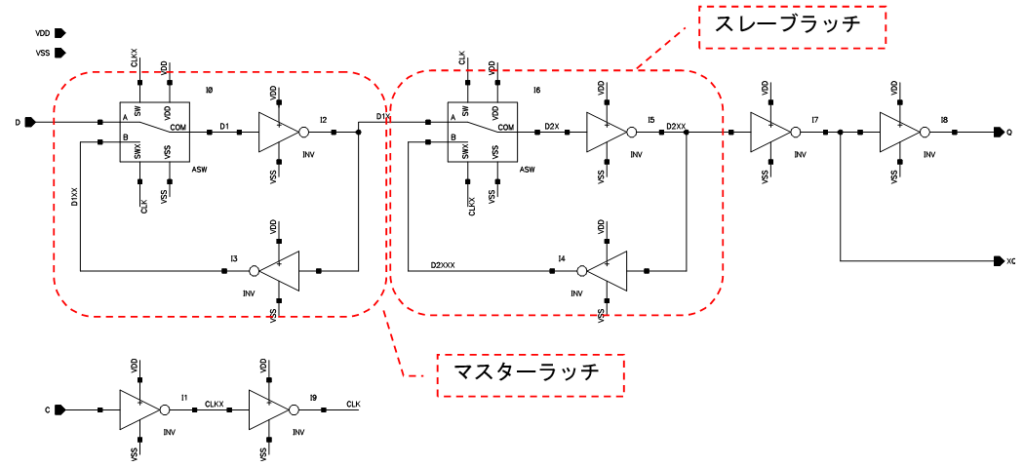

そこで出てきたのが、D-FF回路(図 5)です(やっと本題にたどり着きました)。

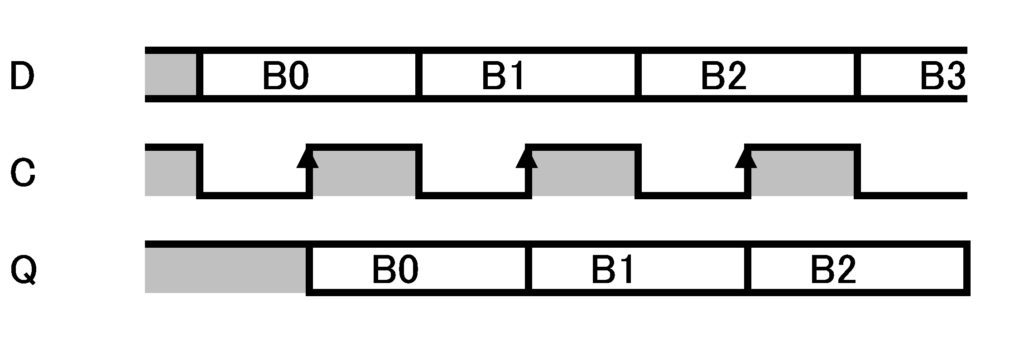

この回路はトランスファーゲートを使ったラッチ回路を2段直列につないだ構成になっていて、前段をマスターラッチ、後段をスレーブラッチと呼びます。この回路はクロックのエッジのみ動作し、一旦ラッチがかかると図 4のDラッチ回路みたいに入力が変化しても出力は変化しません。したがって、クロックのエッジの瞬間の入力状態を保持することができます(図 6)。これにSET,RESET機能をつけたものが最も多く使われているのではないでしょうか。

次回はこのD-FFの動作についてもうちょっと詳しく紹介したいと思います。