こんにちは。PLL設計シリーズの2回目です。今日は、PLLの内部構成についてご紹介します。

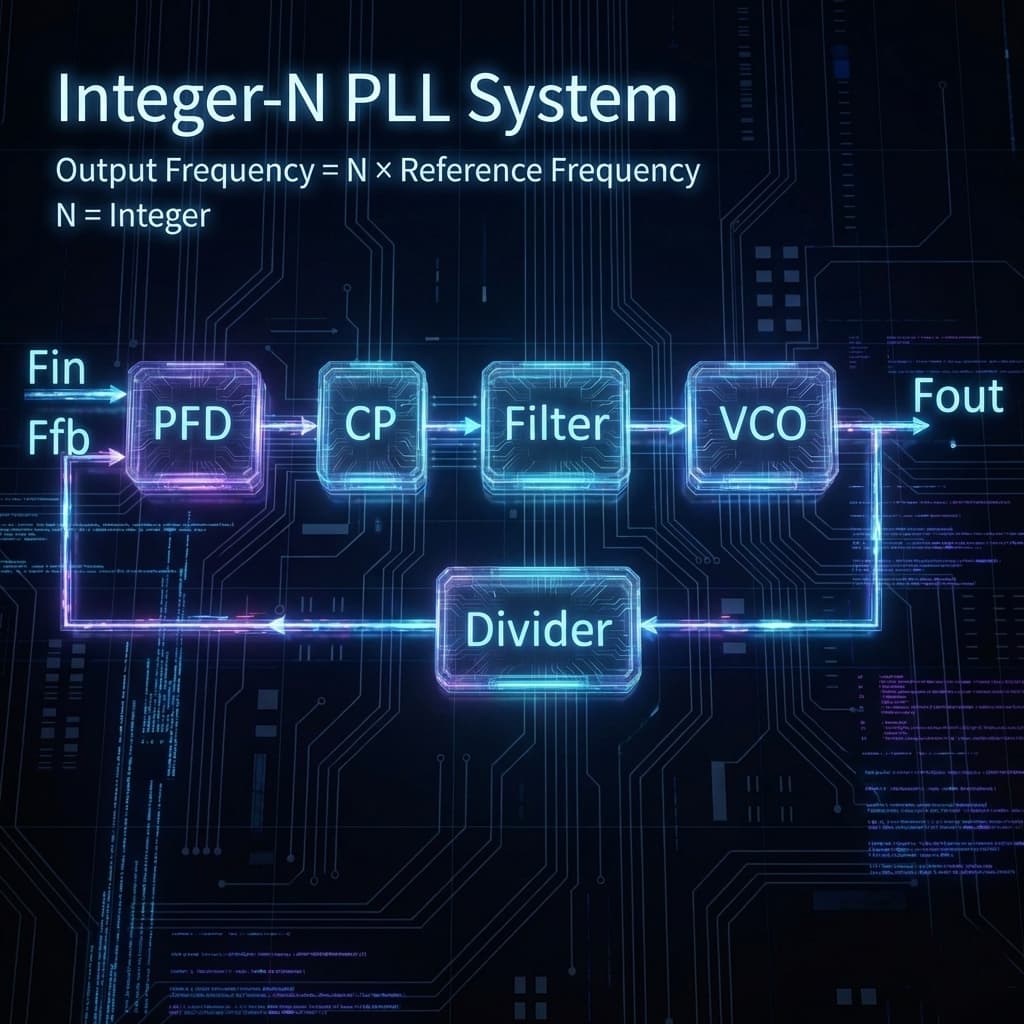

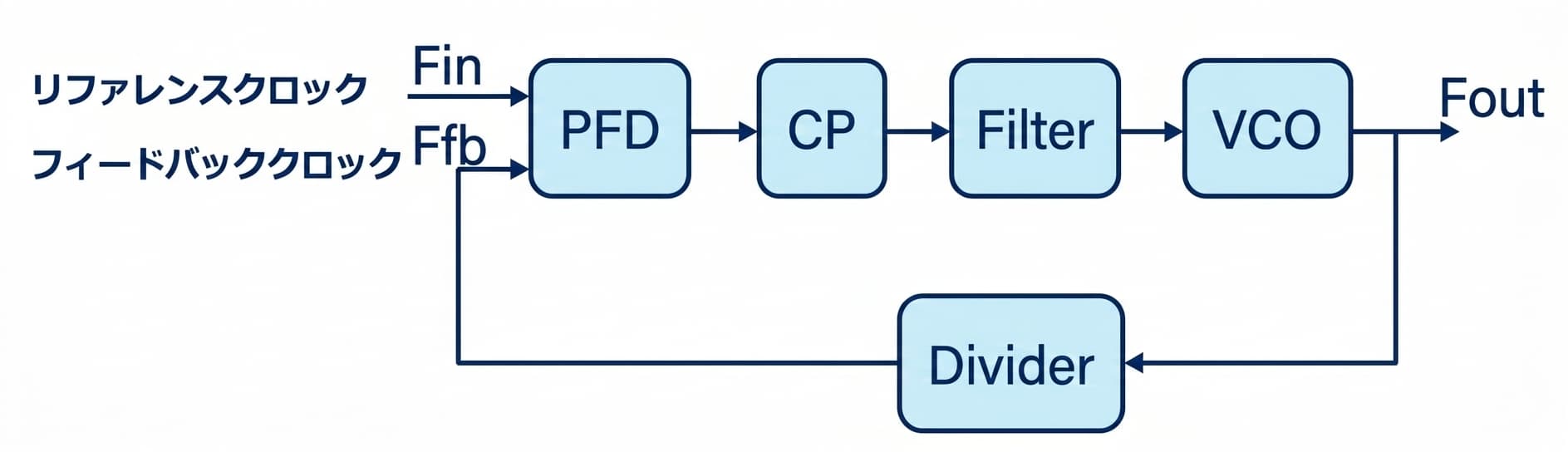

PLLブロック構成

PLLがどのようにして正確な同期を実現しているのか、その内部を覗いてみましょう。PLLは主に5つの機能ブロックで構成されています。それぞれの役割を理解することで、PLLという自動調整システムの全体像が見えてきます。

1. PFD (Phase Frequency Detector:位相周波数比較器)

まず、システムの入り口に位置するのがPFDです。 ここでは、外部から入力される「基準信号(リファレンス)」と、自分自身が出力して戻ってきた「フィードバック信号」の位相と周波数を比較します。二つの信号のタイミングがどれくらいズレているかを検出し、その差分を次のステージへ伝えます。

2. CP (Charge Pump:チャージポンプ)

PFDで検出されたズレの情報(UP/DOWN信号)は、CPへと送られます。 チャージポンプはその名の通り、ズレの量に応じて電流を出し入れする役割を担います。デジタルのパルス信号を、アナログ的な「電荷(電流)」という形に変換する橋渡し役です。

3. LPF (Loop Filter:ループフィルタ)

次に控えるのが、PLLの特性を決定づける重要な要素であるLPFです。 チャージポンプから送られてきた電流を、電圧(制御電圧)に変換します。また、不要なノイズ成分を除去し、VCOを安定して制御するための「滑らかな電圧信号」を作り出す役割も持っています。

4. VCO (Voltage Controlled Oscillator:電圧制御発振器)

PLLの心臓部とも言えるのが、このVCOです。 LPFから受け取った電圧に応じて、出力する周波数を変化させます。電圧が高ければ速く、低ければ遅く振る舞うことで、基準信号に追いつこうと動く「実行部隊」です。

5. Divider (分周器)

最後に忘れてはならないのがDividerです。 VCOが出力した高い周波数を、1/Nにカウントダウン(分周)してPFDへ戻します。この分周器があるおかげで、基準信号と同じ低い周波数で比較を行うことができ、結果として基準信号の「N倍」という高い周波数を作り出すことが可能になるのです。

5つのブロックが生み出す「輪(ループ)」

これら5つのブロックが円を描くように繋がることで、「ズレを見つけ、電圧に変え、周波数を直し、また戻す」という一連のフィードバック・ループが完成します。この精緻な連携こそが、過酷な環境下でも揺るがない安定したクロック信号を生み出す鍵となっています。

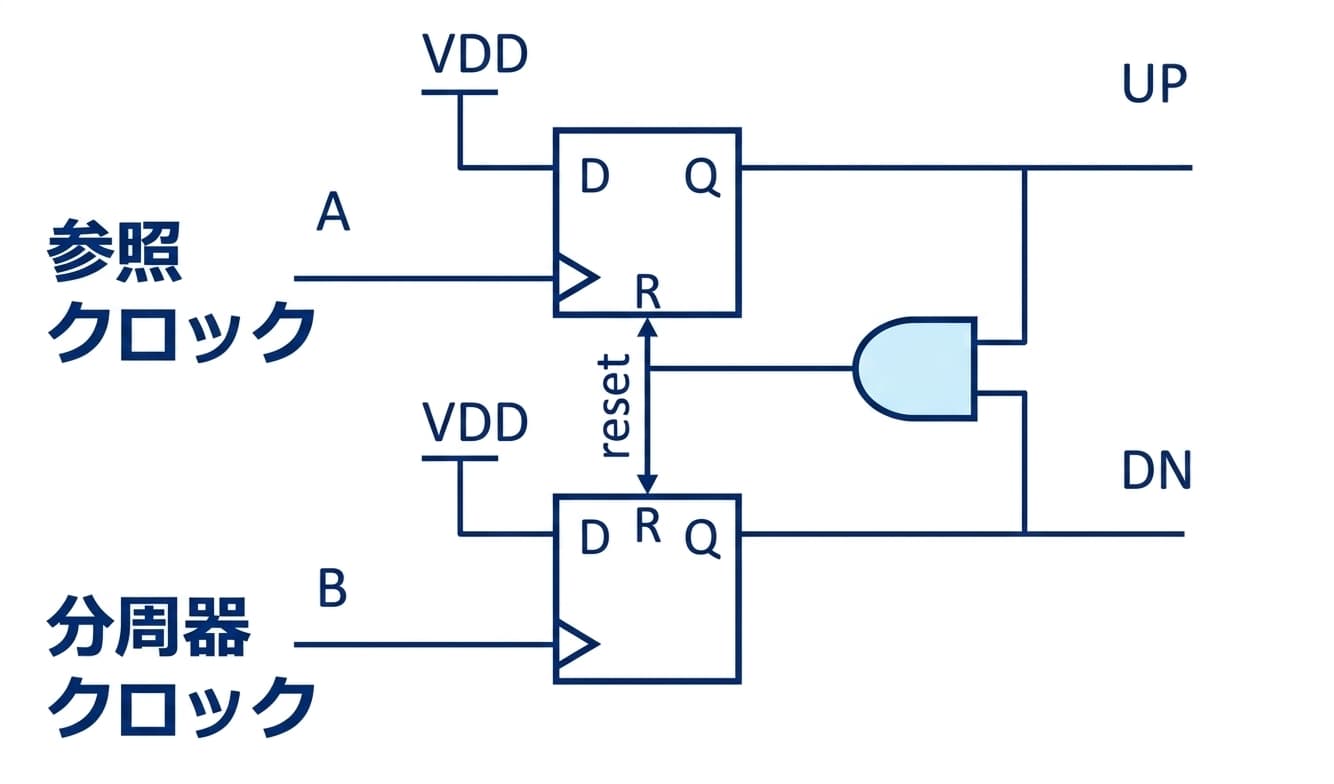

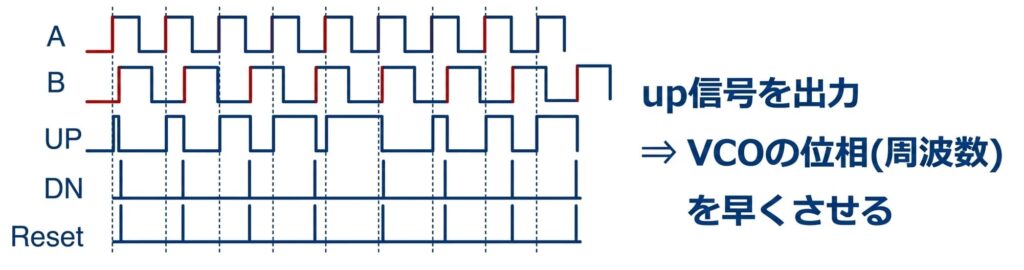

PFD (Phase Frequency Detector):位相誤差をパルスに変換する

PLLの入り口であるPFD(位相周波数比較器)は、2つの入力端子に入ってくる信号のタイミングを厳密にチェックする「目」の役割を担います。基準となる「参照クロック」をA、VCOから戻ってきた「分周クロック」をBとして、その仕組みを詳しく見ていきましょう。

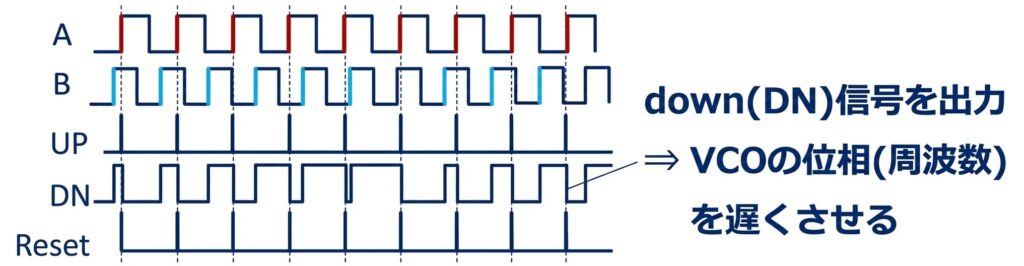

① Aに対してBの位相が「遅れている」場合

参照クロックAに対して、戻ってきた分周クロックBの到着が遅い状態です。 このとき、PFDはUP信号を出力します。これは「VCOの周波数を上げて、もっと速く回転させなさい」という指示になります。

② Aに対してBの位相が「進んでいる」場合

逆に、参照クロックAよりも先に分周クロックBが届いてしまった状態です。 このとき、PFDはDOWN信号を出力します。これは「VCOの周波数を下げて、回転を遅くしなさい」という指示になります。

PFDの最大の特徴は、これらAとBの位相誤差をPWM(パルス幅変調)波形で出力する点にあります。PWMとは、信号の「0か1か」という情報の代わりに、パルスの「横幅(時間)」を使って情報の大きさを表現する方式です。

- ズレが小さいとき:パルスの幅が狭くなる

- ズレが大きいとき:パルスの幅が広くなる

このように、位相のズレ(アナログな量)をパルスの幅(時間の長さ)に置き換えて出力することで、後段の回路へ「どれくらい修正すべきか」を正確に伝えることができるのです。

チャージポンプ/フィルタ:パルスを電圧に変換し、特性を決める

PFDが出力したPWM波形(UP/DOWN信号)は、そのままではVCOを動かすことができません。これらをVCOが理解できる「制御電圧(Vc)」へと変換するのが、チャージポンプ(CP)とフィルタ(LPF)の役割です。

このセクションは、PLL全体の「安定性」や「応答スピード」といった周波数特性を決定づける非常に重要な心臓部です。

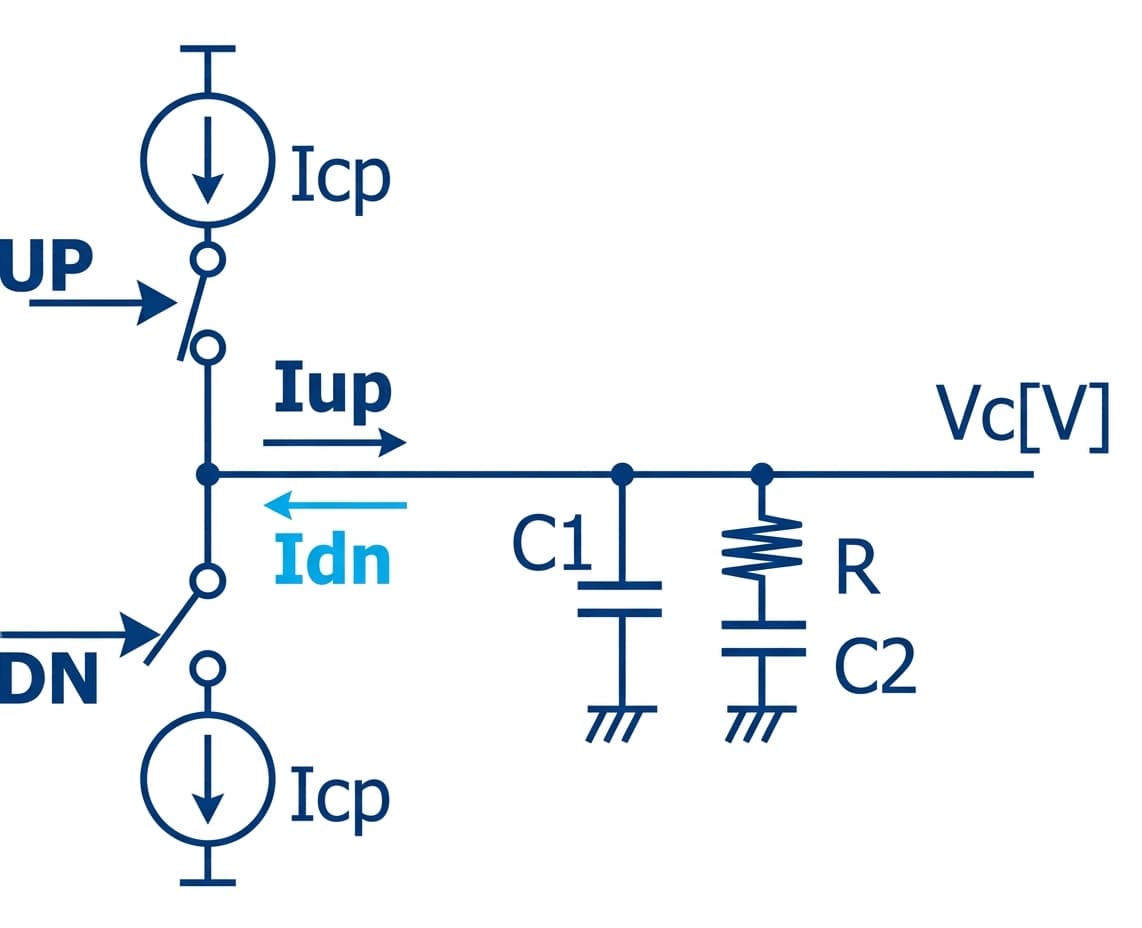

チャージポンプ(CP)の動き:パルスを電流に変える

チャージポンプは、PFDからのパルス信号に応じて電流を出し入れするスイッチのような働きをします。

- UP信号が入ったとき(位相を進めさせたい場合): チャージポンプ内のスイッチが切り替わり、フィルタ側へ電流(Iup)が流れ出します。 これにより、フィルタ内のコンデンサに電荷が蓄えられ、制御電圧(Vc)が上昇します。結果として、VCOの発振周波数が増加します。

- DN(DOWN)信号が入ったとき(位相を遅れさせたい場合): 逆に、フィルタからチャージポンプ側へ電流(Idn)が流れ込みます。 コンデンサの電荷が引き抜かれるため、制御電圧(Vc)が下降し、VCOの発振周波数は減少します。

ループフィルタ(LPF)の役割:電圧を整え、特性を創る

チャージポンプの後ろに控える抵抗(R)とコンデンサ(C1, C2)のネットワークがフィルタです。

単に電圧を滑らかにするだけでなく、PLL全体のループ周波数特性を決定するという極めて重要な役割を持っています。このフィルタの設計(各素子の値の決め方)によって、目標の周波数にどれくらい早くロックするか、あるいはどれくらいノイズ(ジッタ)を抑えられるか、といったPLLの「性格」が決まります。

次回は、PLLの構成要素の残り、VCOと分周期についてご紹介いたします。

参考文献:群馬大 元澤 篤史 先生「PLL設計の基礎」 https://kobaweb.ei.st.gunma-u.ac.jp/lecture/20190723_motozawa.pdf