「高速インターフェース」や「高速伝送設計」と聞くと、“GHz帯は上級者向けで難しい”と感じる方が多いかもしれません。

しかし、正しい知識と論理的な手順で設計すれば、上級者でなくても十分に挑戦できます。

特に、配線(伝送路)やインターフェースの物理特性を正しく理解することが、設計成功のカギとなります。

高速IF設計の基本ステップ

高速インターフェース開発は、下記の流れで進めます。

- 伝送路の特性を知る

PCBやケーブルなど、信号が通るすべての物理経路を定量的に評価し、シミュレーションモデル(IBIS、Touchstoneファイル等)を用いて精度高く再現しましょう。 - 必要な機能・要件を整理

データレートやクロック方式、ノイズ耐性など、必要条件を洗い出しましょう。 - ブロック構成を考える

データ・クロックパスの流れや終端方法、バッファIC配置までの全体設計を固めましょう。 - 回路設計・レイアウト・シミュレーション

回路図設計とシミュレーションを繰り返し、設計の妥当性を確認しましょう。

伝送路のモデリングと評価

高速IF設計の最初の難関は、「伝送路特性の正確な把握」です。

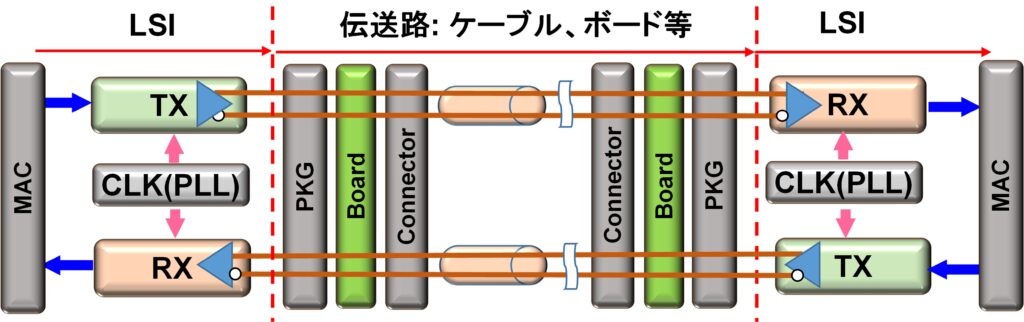

伝送路は“複合システム”

実際の高速伝送系は、単なる配線ではありません。

- 基板配線(ストリップライン、差動ペア)

- ケーブル(外部との接続、ピン間クロストーク)

- コネクタ・ボンディングワイヤ

- 終端抵抗やバッファ回路

など、伝送路は、物理層として多数の素子が直列・並列で接続され、それぞれ固有の寄生成分(L, C, R, M)や損失、反射要素を持っています。

初級エンジニアが陥りがちなのが、“回路だけ”に着目してしまい、伝送路も含めての複合システムで考えることが、システム全体の品質を左右することを見落としてしまう点です。そうならないためにも、まず各要素をSpectre等の回路シミュレータ上で形成しシステム全体を統合的にシミュレーションすることが最初のステップとして重要です。

Spectreでシステム全体を統合シミュレーション

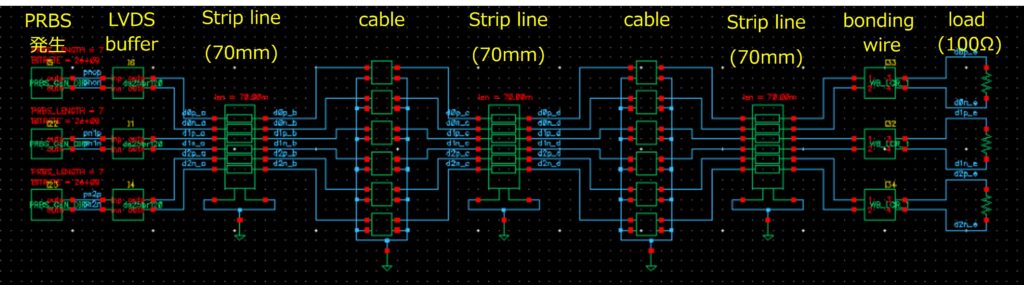

2Gbps伝送モデルを例に実際にSpectre上で各要素を結合して高速IFを設計してみました。

以下は統合シミュレータ上での高速IF設計上のポイントです。

- PRBS発生(Verilog-Aでモデル化)

ランダムパターン信号(Pseudo Random Binary Sequence)を生成して、システムのストレステストシミュレーションを実行できます。 - LVDSバッファ(IBISモデル)

シリコンICバッファの、現物に近い出力特性を再現します。 - ストリップライン(70mm)・ケーブル

伝送路の主要経路。ケーブル部はSパラメータ(Touchstoneファイル)で、帯域損失・反射特性・高次モード影響の評価をします。 - ボンディングワイヤ(L, R, C, MのSPICEネットリスト)

チップ-パッケージ間の物理的なワイヤ配線。伝送路特性上無視できません。

伝送路も含めての全体シミュレーションを基に、伝送波形、ビットレベル波形・ノイズ伝播・損失分布・終端ミスマッチによる反射や過渡現象などを想定しながら、システムとして統合的に再現・解析していきましょう。

ココで重視するポイント

- メーカー値の鵜呑み厳禁:各素子のカタログ値だけでなく、現物配線や温度・実装条件も考慮。

- 設計段階で“波形崩れの発生点”を特定:補償・改善策(終端調整やPE値最適化)の優先順位を付ける。

このように「伝送路の物理現象を細かくモデル化することが、高速IF設計の第一歩」です。

設計初期から現実の回路挙動を忠実に反映したシミュレーションを心がけましょう。

次回は、伝送波形とその評価方法、アイパターンについてです。