今回は「PLL(その2)」です。

前回はPLLに不可欠な位相比較器をビヘイビアモデルを使ってモデル化しました。

今回は、電圧制御発振器(VCO)をモデル化してPLL全体の動作を、位相や周波数を分かりやすい電圧に置き換えてPLLを説明してみたいと思います。

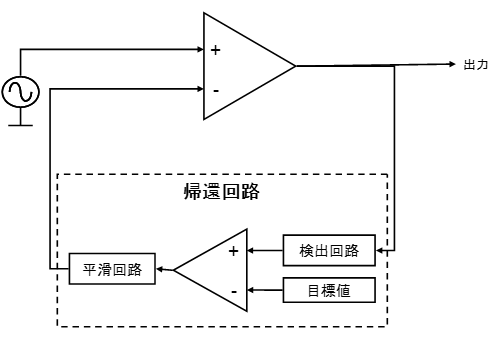

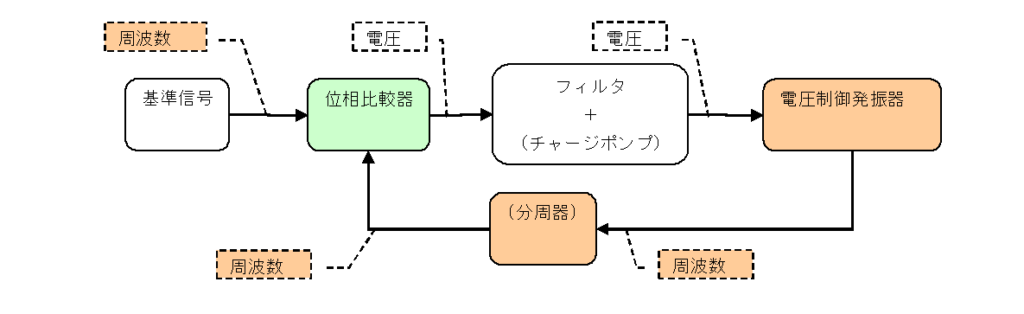

PLLは、位相比較器、フィルタ+チャージポンプ、電圧(または電流)制御発信器、分周器の4つの要素で作る事ができます。

(チャージポンプや分周器はPLLの性能や機能を高めるための回路で、PLLに必須の回路ではありません。)

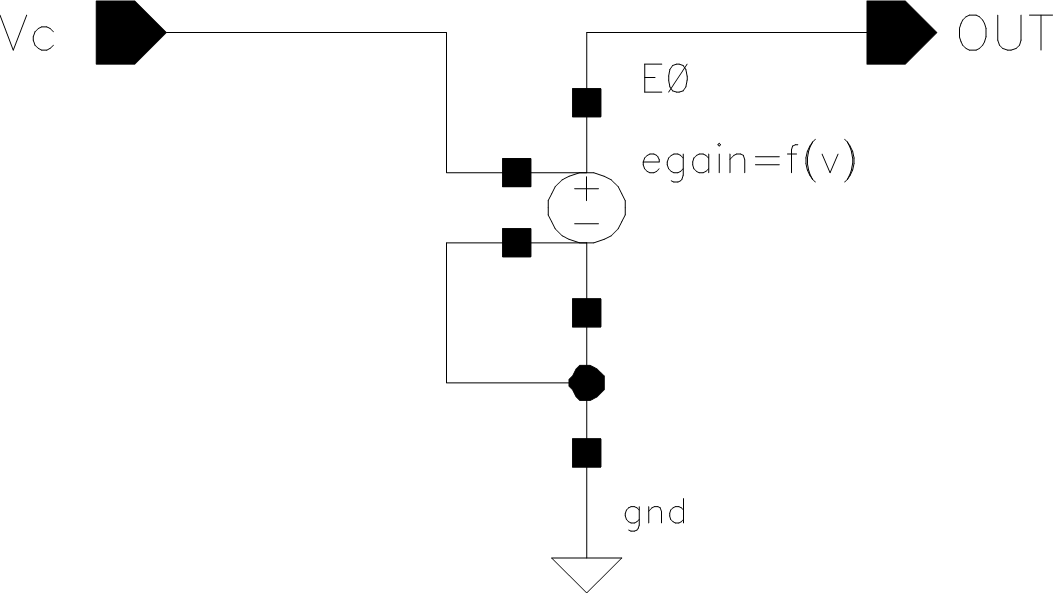

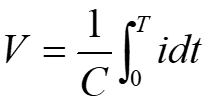

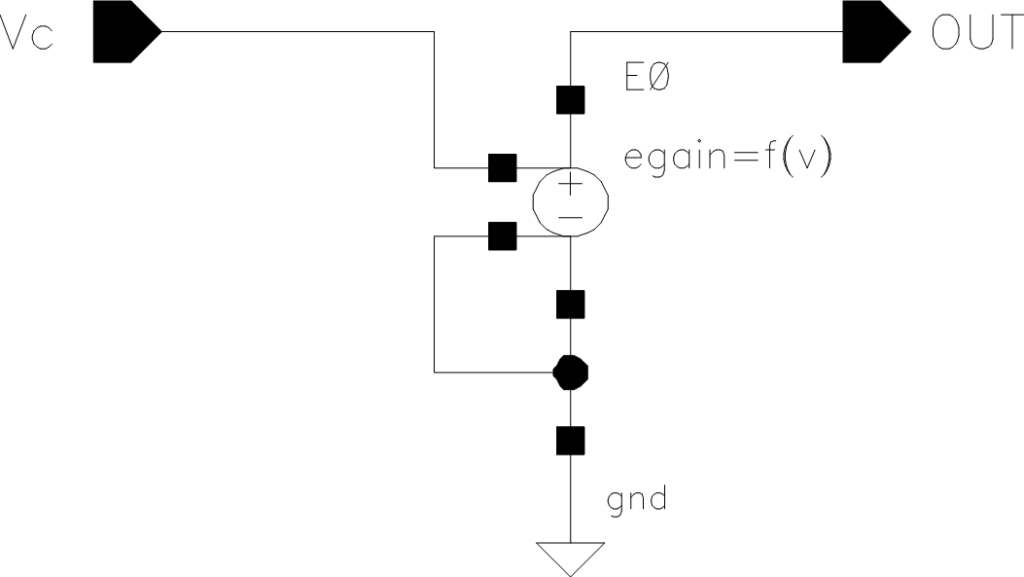

VCOも位相比較器と同じように1MHz=1Vと定義して等価モデルを作ります。こちらは、位相比較器より簡単に電圧制御電圧源(VCVS)のみモデル化できます。

.param fo=10

.param dfp=’0.1/3.3′

.param Kv=’1/(2*dfp)’

.param Vref=1.65

e0 out 0 Value=fo*(2/(exp((Vref-v(vc))/Kv)+1))

周波数(1MHz)を電圧(1V)で表現すればよいので好みの計算式を入れるだけです。

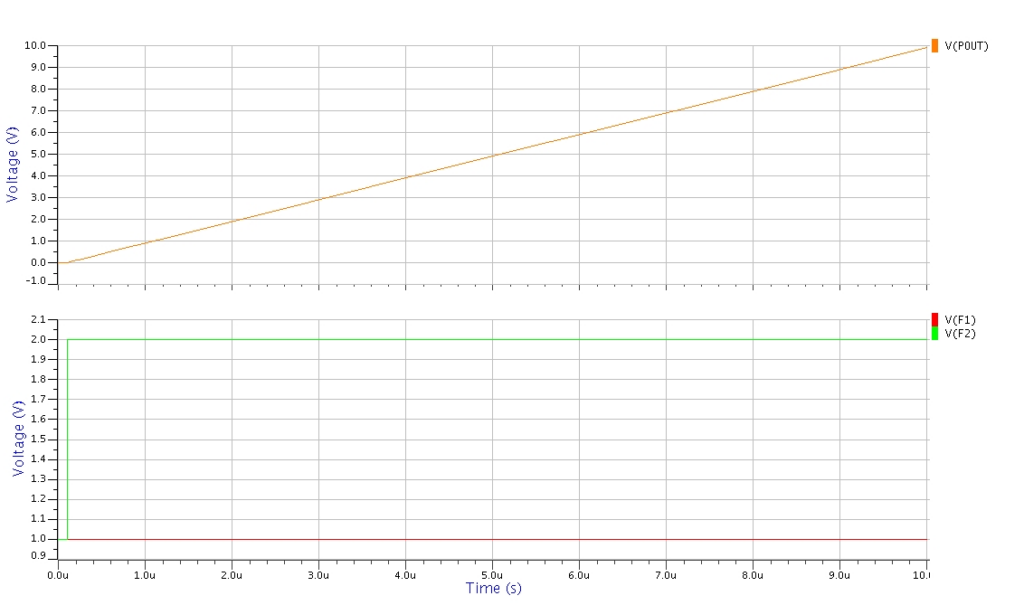

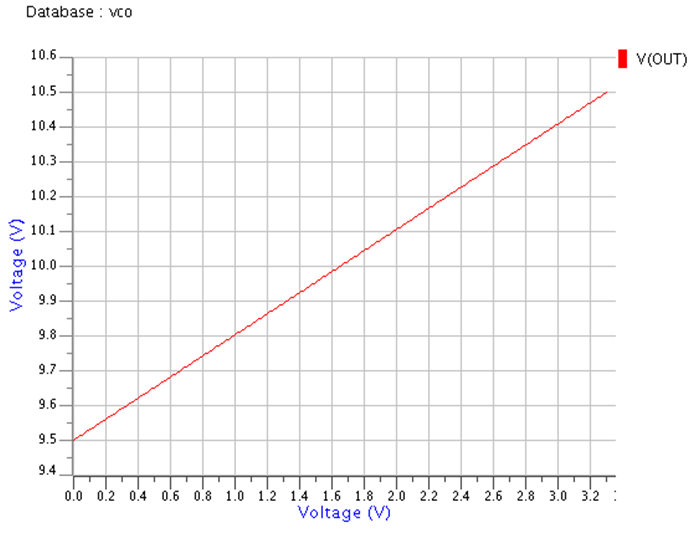

上の例では自然対数を使って、Vcに1.65Vを与えた時に10MHz(10V)が、Vc=0~3.3Vと変えると周波数は9.5~10.5MHzと変化するようにパラメータを設定しています(下図参照)。

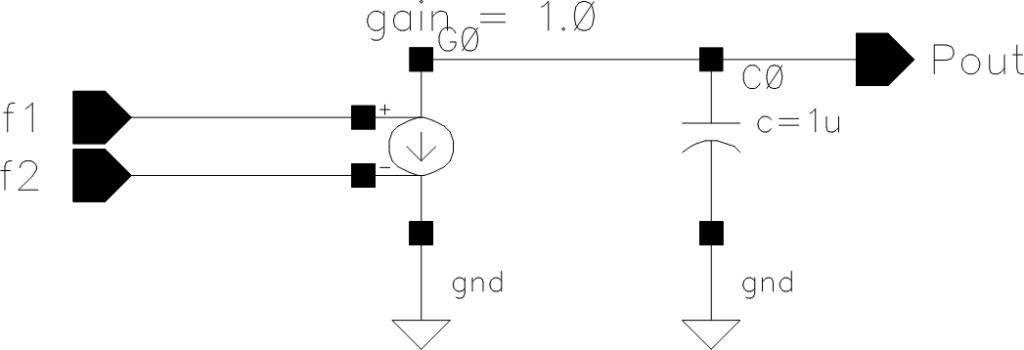

続いて前回の位相比較器(PC)と合わせて、PLL全体をシミュレーションしてみます。

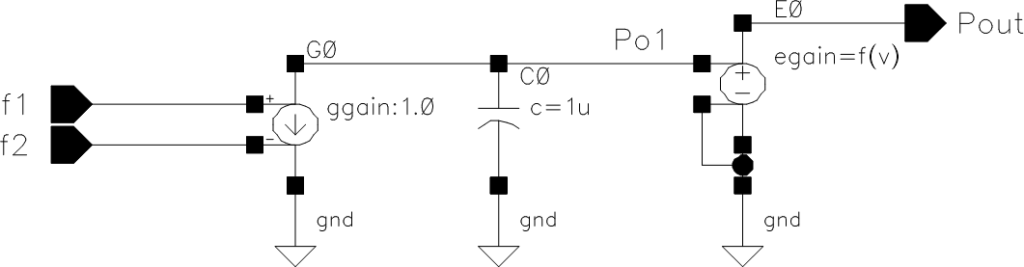

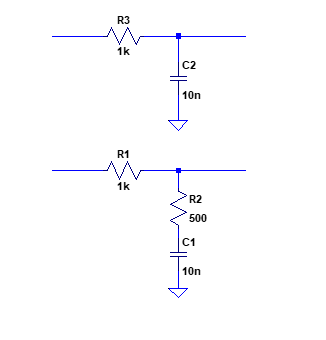

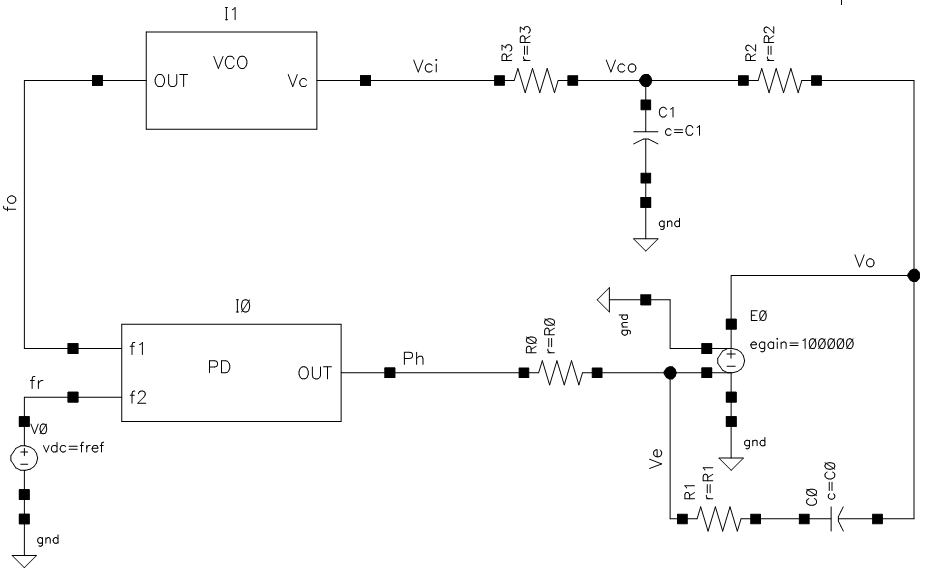

今回のVCOと前回のPD(位相比較器)をサブサーキットにして、ラグリードフィルタ(R0,R1,C0)と利得100dBの圧縮アンプ(E0)、VCOの制御電圧の雑音除去用に1次のLPF(R2,C1)で構成しています。R3はオープンループ特性などをシミュレーションするときに都合が良いので、入れていますが、実際には0Ωにします。

PDの出力PhもVCOの制御Vciも電圧なので、実際にPLLに使う回路をそのまま使ってシミュレーションが出来るところが都合いいところです。

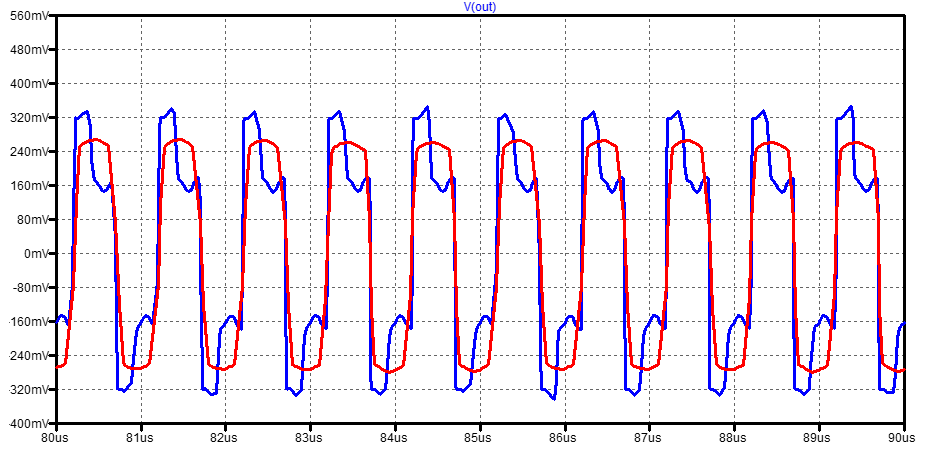

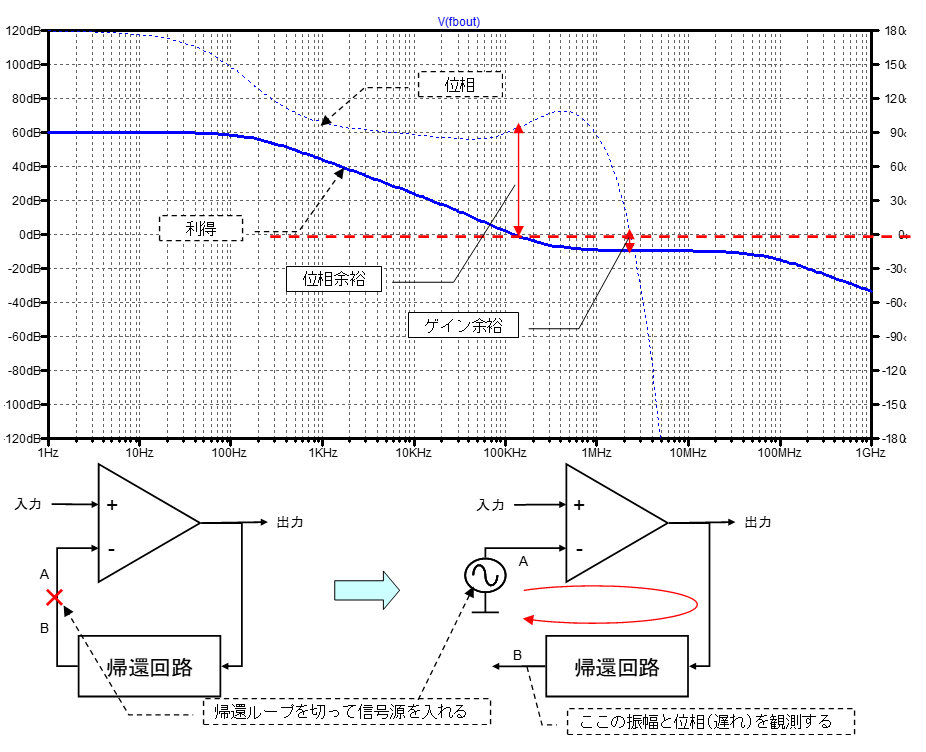

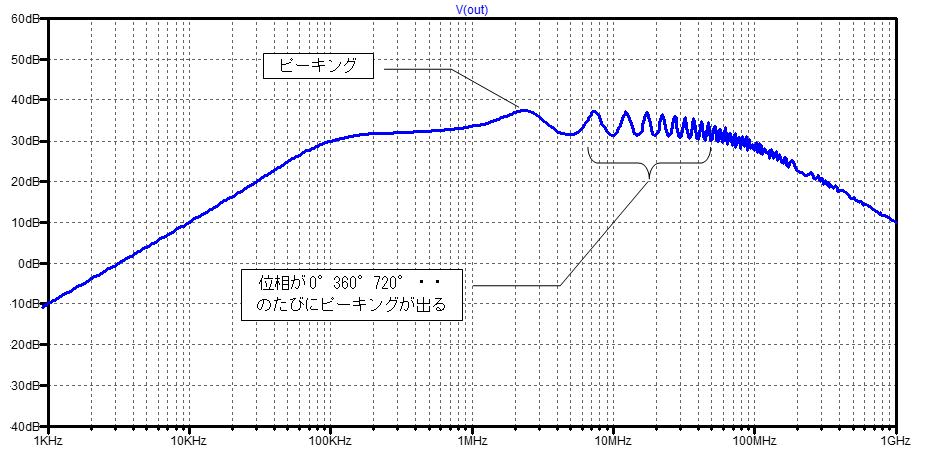

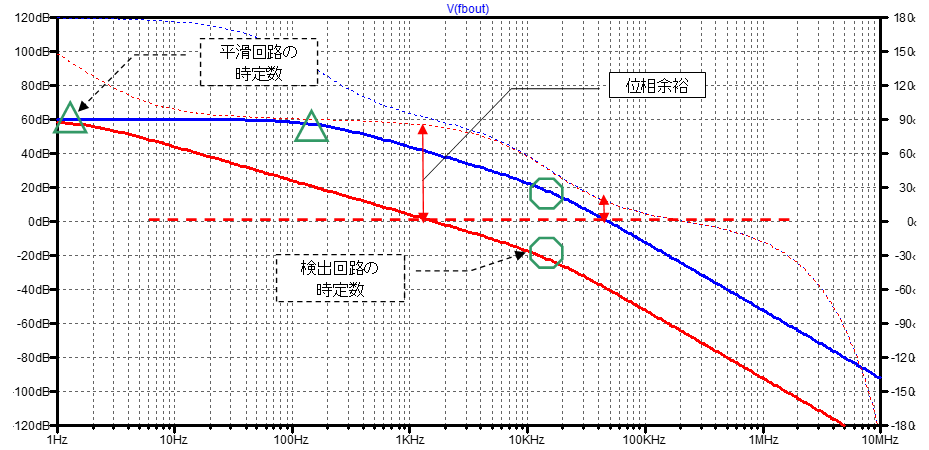

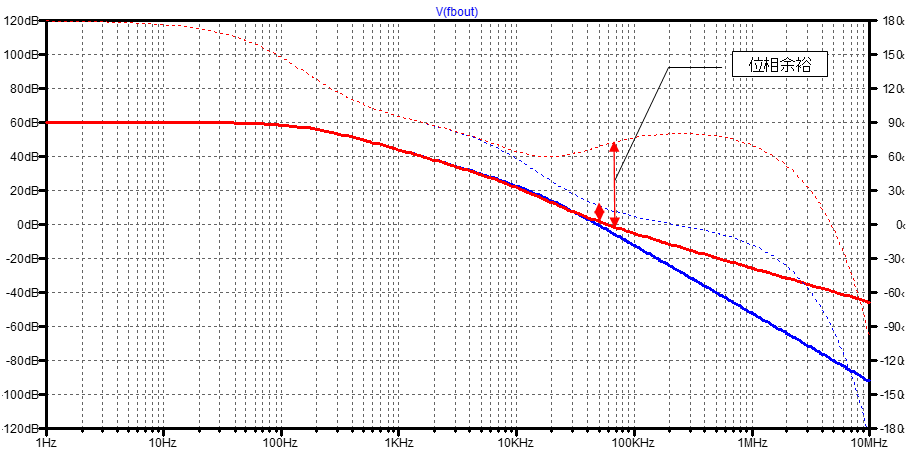

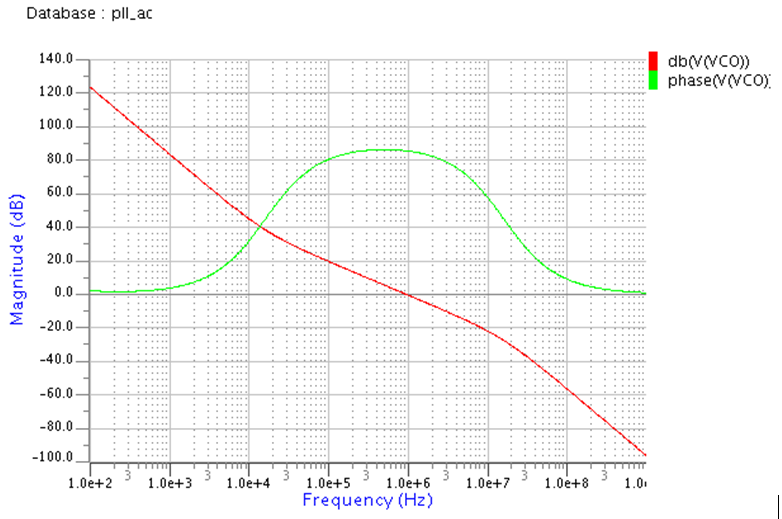

R3をOPENにしてシミュレーションしたオープンループ特性を上図に示します。利得特性(赤線)が0dBとなる周波数(1MHz)の位相が85°であることから、十分な位相余裕が確保できています。このときの各部品の定数は下記に通りです。

.param r0=510 r1=10k c0=1n

.param r2=1k c1=10p

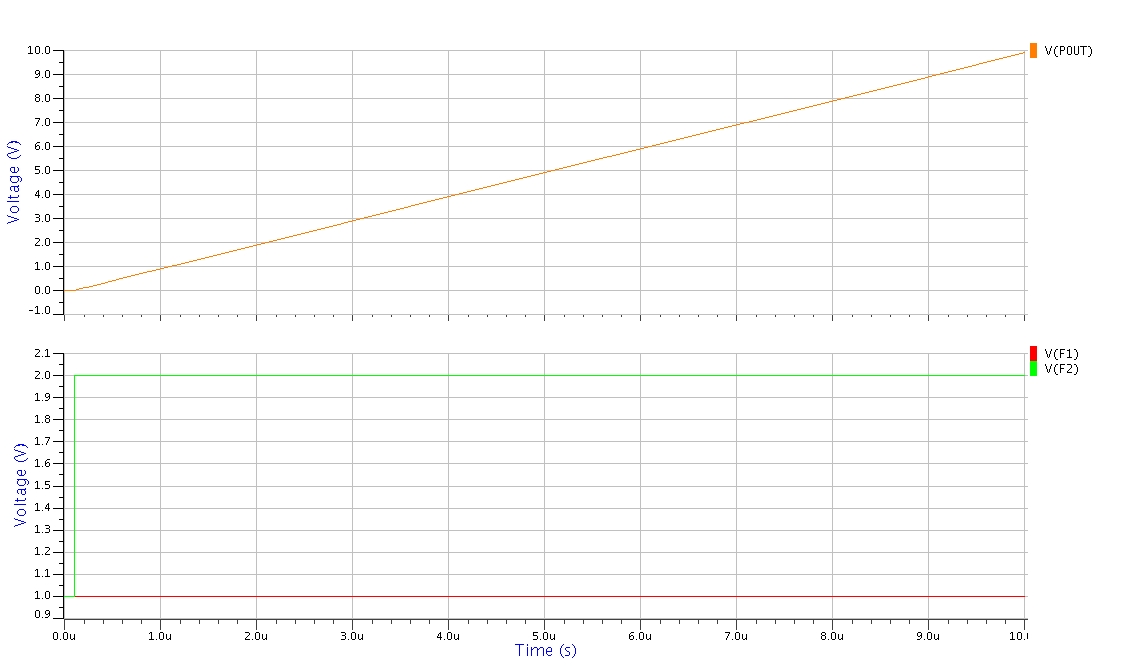

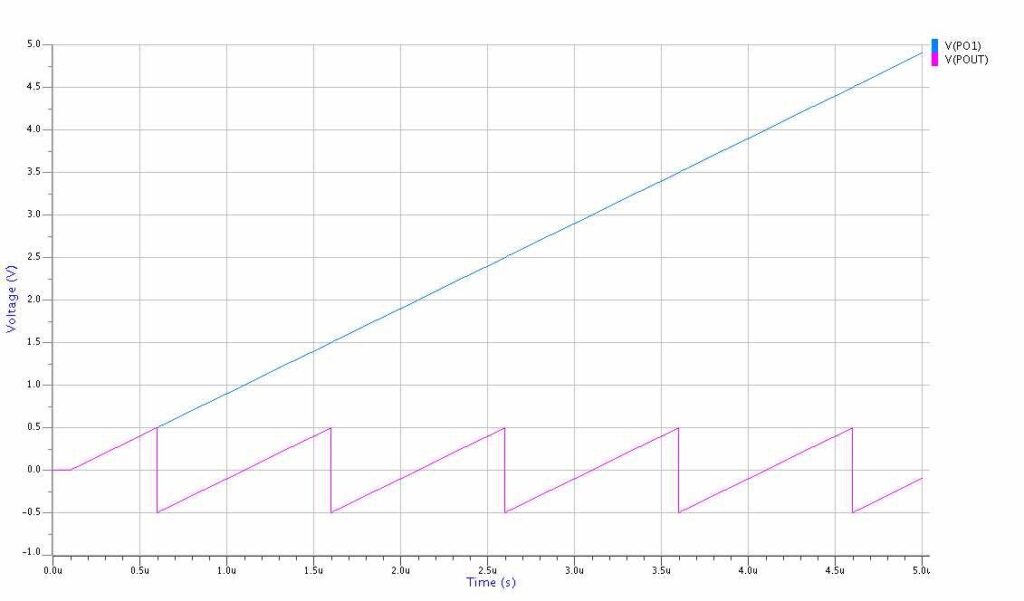

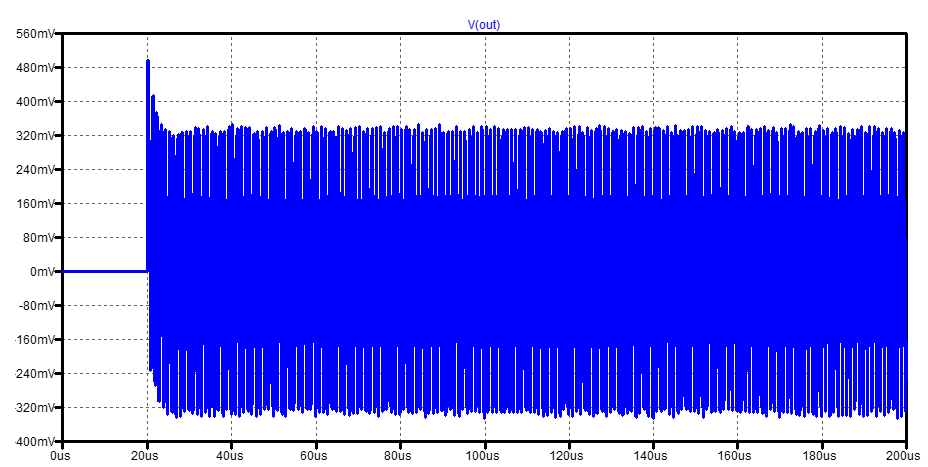

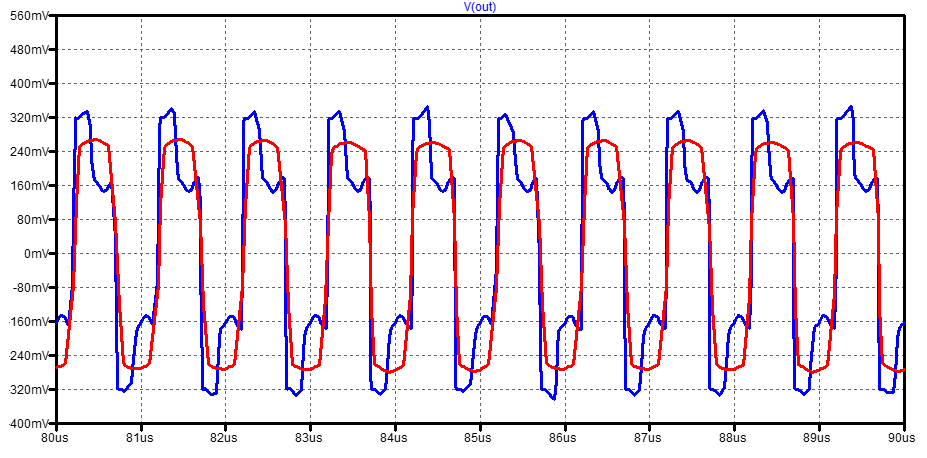

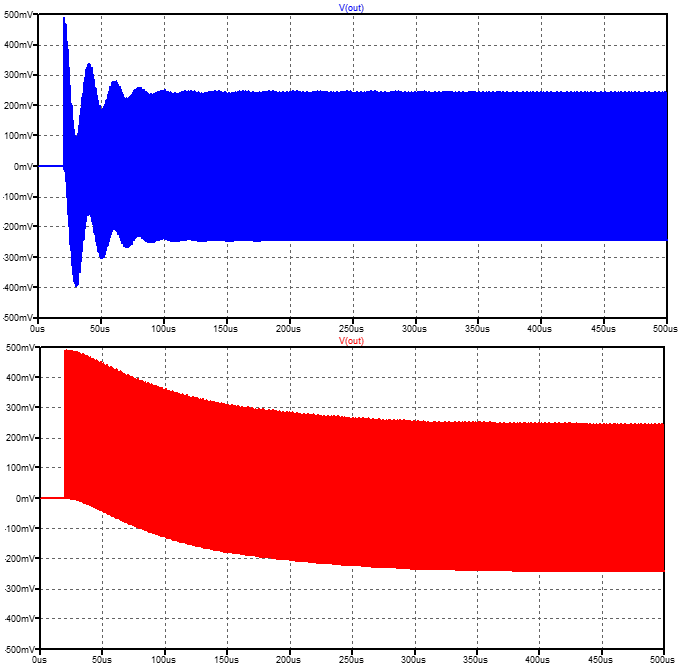

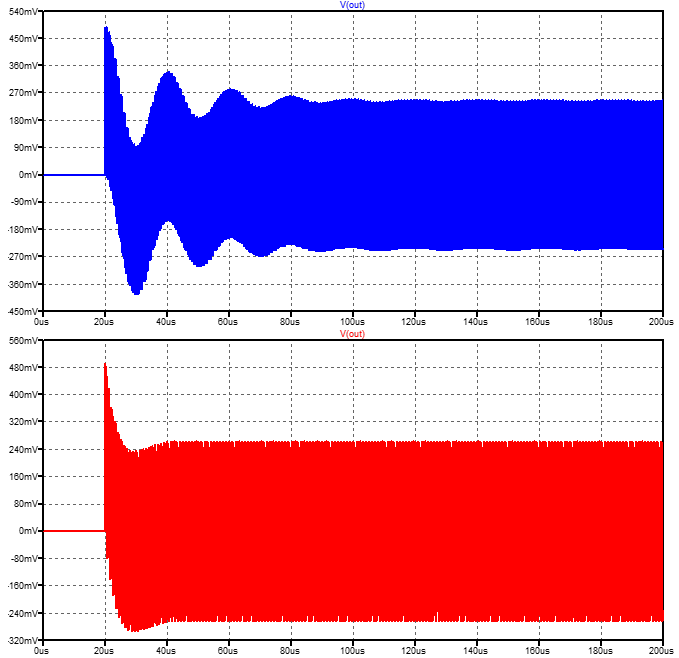

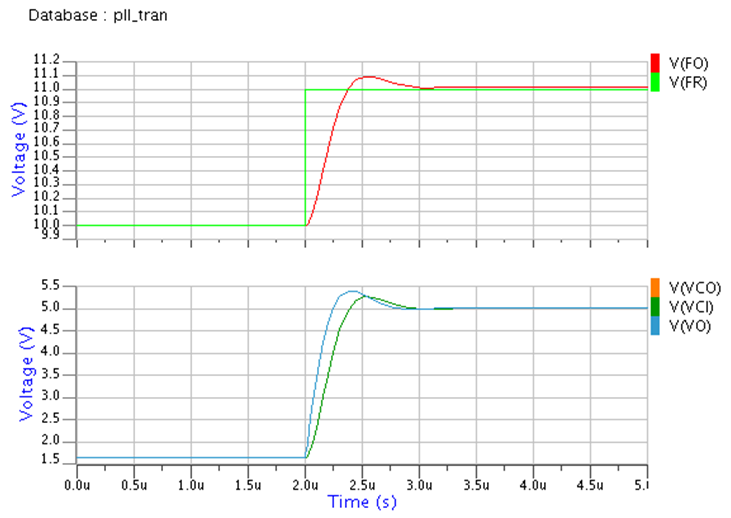

このままR3をSHORTにして、過渡解析を実施した結果を下図に示します。

2usecでレファレンス周波数(FR)を10MHz => 11MHzと変えたときの過渡解析です。約1uscで安定して収束しています。

PLLは時間に関連する操作をする回路なので理解しにくいし、実際の回路のまま過渡解析をすると時間がかかる嫌な回路なのですが、電圧制御発振器(VCO)と位相比較器(PD)の扱う周波数や位相をビヘイビアモデルで電圧に置き換えることで、解析時間も短くなるし、理解も簡単になると思います。

次回は、PLL特有の特性(ロックレンジやシーズインレンジなど引き込みに関する特性)を今回のモデルを使って説明したいと思います。(美斉津)